Abstract

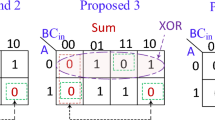

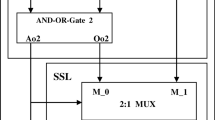

This paper presents two new inexact sum-based 1-bit approximate full adders (AFAs). The proposed 1-bit approximate adders (PAAs), namely PAA1 and PAA2, are derived based on the majority logic. The layouts of PAAs are designed in quantum cellular automata (QCA) technology using the QCADesigner tool. To assess the performance of PAAs, we compare them against the reported AFAs in terms of various design metrics, such as the total area, delay, and performance. The comparison results show that the PAA1 and PAA2, having an area of 0.02 \(\upmu \hbox {m}^{2}\) and 0.04 \(\upmu \hbox {m}^{2}\), provide area savings of 60% and 20%, respectively, compared with the lowest-area AFA reported in the literature. Also, the PAA1 and PAA2 have an equal delay of 0.5 clock cycles, that is, 33.33% less as compared to the AFA with the lowest delay. The designs are analyzed in terms of image quality metrics for image processing applications. Besides area efficiency and delay performance, on average, PAA1 provides the worst PSNR/SNR, while PAA2 provides the best PSNR/SNR compared to the other state-of-the-art approximate adders.

Similar content being viewed by others

Availability of data and materials

Both data and methods are available upon request.

References

H.A.F. Almurib, T.N. Kumar, F. Lombardi, Inexact designs for approximate low power addition by cell replacement, in Proceedings of IEEE International Conference on Design, Automation and Test in Europe Conference and Exhibition (DATE), Dresden, Germany, pp. 660–665 (2016)

I.E. Arani, A. Rezai, Novel circuit design of serial-parallel multiplier in quantum-dot cellular automata technology. J. Comput. Electron. 7, 1–9 (2018)

B. Aravinth, L.J.A. Marcilin, Implementation of coplanar approximate adders in QCA, in 2016 International Conference on Wireless Communications, Signal Processing and Networking (WiSPNET), pp. 680–684 (2016)

H. Cho, E.E. Swartzlander, Adder and multiplier design in quantum-dot cellular automata. IEEE Trans. Comput. 58(6), 721–727 (2009)

R. Courtland, Transistors could stop shrinking in 2021: a key industry report forecasts an end to traditional scaling of transistors, IEEE Spectrum (2016). https://spectrum.ieee.org/semiconductors/devices/transistors-could-stop-shrinking-in-2021

A. Dalloo, A. Najafi, A. Garcia-Ortiz, Systematic design of an approximate adder: the optimized lower part constant-OR adder. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 26(8), 1595–1599 (2018)

R. Hegde, N.R. Shanbhag, Soft digital signal processing. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 9(6), 813–823 (2001)

W.M. Holt: 1.1 Moore’s law: a path going forward, in IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, pp. 8–13 (2016). https://doi.org/10.1109/ISSCC.2016.7417888

International Road Map for Devices and Systems (IRDS): Beyond CMOS, 2020 Edition, available at https://irds.ieee.org/images/files/pdf/2020/2020IRDS_MM.pdf

C. Labrado, H. Thapliyal, F. Lombardi, Design of majority logic based approximate arithmetic circuits, in IEEE International Symposium on Circuits and Systems (ISCAS), 2017, pp. 1–4 (2017)

C.S. Lent, B. Isaksen, M. Lieberman, Molecular quantum-dot cellular automata. J. Am. Chem. Soc. 125(4), 1056–1063 (2003)

C.S. Lent, P.D. Tougaw, W. Porod, G.H. Bernstein, Quantum cellular automata. Nanotechnology 4, 49–57 (1993)

O. Liolis, V.A. Mardiris, G.C. Sirakoulis, I.G. Karafyllidis: Quantum-dot cellular automata RAM design using crossbar architecture, in IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH). Athens, 2018, pp. 1–5 (2018)

H.R. Mahdiani, A. Ahmadi, S.M. Fakhraie, C. Lucas, Bio-inspired imprecise computational blocks for efficient VLSI implementation of soft-computing applications. IEEE Trans. Circuits Syst. I Regul. Pap. 57(4), 850–862 (2010)

NASA: Bit-serial adder based on quantum dots, Washington, DC [Online]. Available http://www.nasatech.com/Briefs/Jan03/NPO20869.html

M.C. Parameshwara, Approximate full adders for energy efficient image processing applications. J. Circuits Syst. Comput. 30(13) (early access)

V. Pudi, K. Sridharan, Low complexity design of ripple Carry and Brent-Kung adders in QCA. IEEE Trans. Nanotechnol. 11(1), 105–119 (2012)

D. Rairigh, Limits of CMOS Technology Scaling and Technologies Beyond-CMOS (Institute of Electrical and Electronics Inc., Piscataway, 2005)

B. Sen, T. Adak, A.S. Anand, B.K. Sikdar, Synthesis of reversible universal QCA gate structure for energy efficient digital design, in TENCON 2011—2011 IEEE Region 10 Conference, Bali, 2011, pp. 806–810. https://doi.org/10.1109/TENCON.2011.6129222.

T. Skotnicki, J.A. Hutchby, H.-P. Tsu-Jae King, F. Boeuf. Wong, The end of CMOS scaling: toward the introduction of new materials and structural changes to improve MOSFET performance. IEEE Circuits and Devices Magazine 21(1), 16–26 (2005). https://doi.org/10.1109/MCD.2005.1388765

P.D. Tougaw, C.S. Lent, Logical devices implemented using quantum cellular automata. J. Appl. Phys. 75(3), 1818–1824 (1994)

V. Vankamamidi, M. Ottavi, F. Lombardi, Clocking and cell placement for QCA, in Sixth IEEE Conference on Nanotechnology, 2006, pp. 343–346 (2006)

K. Walus, A. Vetteth, G. Jullien, V. Dimitrov, RAM design using quantum-dot cellular automata, in Tech Proceedings of Nanotechnology Conference and Trade Show 2, 160–163 (2003)

W. Wang, K. Walus, G.A. Jullien, Quantum-dot cellular automata adders, in 2003 Third IEEE Conference on Nanotechnology, 2003. IEEE-NANO 2003., San Francisco, CA, USA, 2003, vol. 2, pp. 461–464

K. Walus, T.J. Dysart, G.A. Jullien, R.A. Budiman, QCADesigner: a rapid design and Simulation tool for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 3(1), 26–31 (2004)

Y. Xia, K. Qiu, Design and application of universal logic gate based on quantum-dot cellular automata, in 2008 11th IEEE International Conference on Communication Technology, Hangzhou, 2008, pp. 335–338. https://doi.org/10.1109/ICCT.2008.4716260

R. Zhang, K. Walus, W. Wang, G.A. Jullien, Performance comparison of quantum-dot cellular automata adders, in 2005 IEEE International Symposium on Circuits and Systems, Kobe, 2005, vol. 3, pp. 2522–2526

Z. Zareei, K. Navi, P. Keshavarziyan, Low-power, high-speed 1-bit inexact full adder cell designs applicable to low-energy image processing. Int. J. Electron. 105(3), 375–384 (2018)

T. Zhang, W. Liu, E. McLarnon, M. O’Neill, F. Lombardi, Design of majority logic (ML) based approximate full adders, in IEEE International Symposium on Circuits and Systems (ISCAS), 2018, pp. 1–5 (2018)

Funding

Not applicable.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Code availability

Code used to analyze performance is available upon request.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Parameshwara, M.C., Maroof, N. An Area-Efficient Majority Logic-Based Approximate Adders with Low Delay for Error-Resilient Applications. Circuits Syst Signal Process 41, 4977–4997 (2022). https://doi.org/10.1007/s00034-022-02014-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-02014-6