Abstract

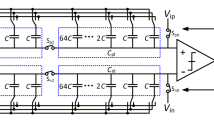

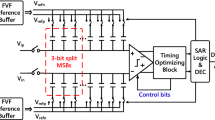

This paper presents a low-power asynchronous 8-bit 500MS/s 2b/cycle successive-approximation-register (SAR) analog-to-digital converter (ADC) in 40 nm CMOS process. The proposed ADC shows high energy efficiency and good performance against process–voltage–temperature (PVT) variations by a background offset mismatch calibration technique, a supply voltage calibration technique and an efficient 2b/cycle switching scheme. The background offset mismatch calibration eliminates the effect of offset mismatches of the comparator array without any extra phase. The supply voltage calibration is presented to monitor the conversion speed of the ADC and adjust the speed of comparators to ensure the ADC can work properly at different process corners. The improved switching scheme helps cut down the switch times and simplifies the switch logic, which saves 87.8% switching energy compared with conventional VCM-based scheme. The proposed SAR ADC simulated a signal-to-noise plus distortion ratio (SNDR) of 45.8 dB and a spurious-free dynamic range (SFDR) of 55.5 dB for a near-Nyquist input while consuming a total power of 2.59 mW, culminating in a Walden figure of merit (FoM) of 32 fJ/conversion-step.

Similar content being viewed by others

Data availability

The datasets generated during and/or analyzed during the current study are available from the corresponding author on reasonable request.

References

S. Babayan-Mashhadi, R. Lotfi, Analysis and design of a low-voltage low-power double-tail comparator. IEEE Trans. Very Large Scale Integr. VLSI Syst. 22, 343–352 (2014)

B. Chen, M. Maddox, M.C.W. Coln, Y. Lu, L.D. Fernando, Precision passive-charge-sharing SAR ADC: analysis, design, and measurement results. IEEE J. Solid-State Circuits 53, 1481–1492 (2018)

Y. Chen, J. Wang, H. Hu, F. Ye, J. Ren, A time-interleaved SAR assisted pipeline ADC with a bias-enhanced ring amplifier. IEEE Trans. Circuits Syst. II Exp. Briefs 65, 1584–1588 (2018)

Z. Cao, S. Yan, Y. Li, A 32mW 1.25GS/s 6b 2b/step SAR ADC in 0.13μm CMOS. ISSCC Dig. Tech. Papers, pp. 542–543 (2008)

C. Chan, Y. Zhu, W. Zhang, U. Seng-Pan, R.P. Martins, A two-way interleaved 7-b 2.4-GS/s 1-then-2 b/cycle SAR ADC with background offset calibration. IEEE J. Solid-State Circuits 53, 850–860 (2018)

B.P. Ginsburg, A.P. Chandrakasan, An energy-efficient charge recycling approach for a SAR converter With capacitive DAC. In: 2005 IEEE International Symposium on Circuits and Systems. 1, pp. 184–187 (2005)

H. Huang, L. Du, Y. Chiu, A 1.2-GS/s 8-bit two-step SAR ADC in 65-nm CMOS with passive residue transfer. IEEE J. Solid-State Circuits 52, 1551–1562 (2017)

H. Hong, W. Kim, H. Kang, S. Park, M. Choi, H. Park, S. Ryu, A decision-error-tolerant 45 nm CMOS 7b 1 GS/s nonbinary 2b/cycle SAR ADC. IEEE J. Solid-State Circuits 50, 543–555 (2015)

H. Huang, H. Xu, B. Elies, Y. Chiu, A non-interleaved 12-b 330-MS/s pipelined-SAR ADC with PVT-stabilized dynamic amplifier achieving sub-1-dB SNDR variation. IEEE J. Solid-State Circuits 52, 3235–3247 (2017)

H. Jeon, Y.-B. Kim, A CMOS low-power low-offset and high-speed fully dynamic latched comparator. International SoC Conference (SoCC). In: IEEE Proceeding, pp. 285–288 (2010)

L. Kull et al., A 3.1mW 8b 1.2GS/s single-channel asynchronous SAR ADC with alternate comparators for enhanced speed in 32 nm digital SOI CMOS. ISSCC Dig. Tech. Papers, pp. 468–470 (2013)

J. Kim, T. Yoo, D. Jung, D. Yoon, K. Seong, T. Kim, K. Baek, A 0.5 V 8–12 Bit 300 KSPS SAR ADC with adaptive conversion time detection-and-control for high immunity to PVT variations. IEEE Access 8, 101359–101368 (2020)

C.C. Liu, S.J. Chang, G.Y. Huang, Y.Z. Lin, A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 45, 731–740 (2010)

W. Lin, T. Kuo, A compact dynamic-performance-improved current-steering DAC ith random rotation-based binary-weighted selection. IEEE J. Solid-State Circuits 47, 444–453 (2012)

J. Luo, Y. Liu, J. Li, N. Ning, K. Wu, Z. Liu, Q. Yu, A low voltage and low power 10-bit non-binary 2b/cycle time and voltage based SAR ADC. IEEE Trans. Circuits Syst. I Reg. Pap. 67, 1136–1148 (2020)

D. Li, J. Liu, H. Zhuang, Z. Zhu, Y. Yang, N. Sun, A 7b 2.6mW 900MS/s Nonbinary 2-then-3b/cycle SAR ADC with Background Offset Calibration. IEEE CICC, pp. 1–4 (2019)

K. Ragab, N. Sun, A 1.4mW 8b 350MS/s loop-unrolled SAR ADC with background offset calibration in 40nm CMOS. IEEE ESSCIRC, pp. 417–420 (2016)

V. Savani, N.M. Devashrayee, Design and analysis of low-power high-speed shared charge reset technique based dynamic latch comparator. Microelectron. J. 74, 116–126 (2018)

D. Shinkel, E. Mensink, E. Klumperink, E. van Tuijl, B. Nauta, A double-tail latch-type voltage sense amplifier with 18ps Setup+Hold time. IEEE ISSCC Dig. Tech. Papers, pp. 314–315 (2007)

M. van Elzakker, et al., A 1.9 uW 4.4fJ/conversion-step 10b 1MS/s charge-redistribution ADC. IEEE ISSCC Dig. Tech. Papers, pp. 244–245 (2008)

S. Wong, U. Chio, C. Chan, H. Choi, S. Sin, Seng-Pan U, R. P. Martins, A 4.8-bit ENOB 5-bit 500MS/s binary-search ADC with minimized number of comparators. IEEE ASSCC, pp. 73–76 (2011)

H. Wei, C. Chan, U. Chio, S. Sin, Seng-Pan U, R. P. Martins, F. Maloberti, A 0.024mm2 8b 400MS/s SAR ADC with 2b/cycle and resistive DAC in 65nm CMOS. ISSCC Dig. Tech. Papers, 188–190 (2011)

H. Wang, W.M. Xie, Z.X. Chen, S.J. Cai, A capacitor-splitting switching scheme with low total power consumption for SAR ADCs. J. Circuits Syst. Comput. 28, 1920002 (2018)

H. Xu, H. Huang, Y. Cai, L. Du, Y. Zhou, B. Xu, D. Gong, J. Ye, Y. Chiu, A 78.5-dB SNDR radiation- and metastability-tolerant two-step split SAR ADC operating up to 75 MS/s with 24.9-mW power consumption in 65-nm CMOS. IEEE J. Solid-State Circuits 54, 441–451 (2019)

D. Xing, Y. Zhu, C. Chan, S. Sin, F. Ye, J. Ren, U. Seng-Pan, R.P. Martins, Seven-bit 700-MS/s four-way time-interleaved SAR ADC with partial Vcm-based switching. IEEE Trans. Very Large Scale Integr. VLSI Syst. 25, 1168–1172 (2017)

C. Yuan, Y. Lam, Low-energy and area-efficient tri-level switching scheme for SAR ADC. Electron. Lett. 48, 482–483 (2012)

Y. Zhu, C.H. Chan, U.F. Chio, S.W. Sin, U. Sweng-Pan, R.P. Martins, F. Maloberti, A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits 45, 1111–1121 (2010)

H.Y. Zhuang, W.J. Guo, J.X. Liu, H. Tang, Z. Zhu, L. Chen, N. Sun, A second-order noise-shaping SAR ADC with passive integrator and tri-level voting. IEEE J. Solid-State Circuits 54, 1636–1647 (2019)

Y. Zhou, B. Xu, Y. Chiu, A 12 bit 160 MS/s two-step SAR ADC with background bit-weight calibration using a time-domain proximity detector. IEEE J. Solid-State Circuits 50, 920–931 (2015)

Y. Zhou, B. Xu, Y. Chiu, A 12-b 1-GS/s 31.5-mW time-interleaved SAR ADC with analog HPF-assisted skew calibration and randomly sampling reference ADC. IEEE J. Solid-State Circuits 54, 2207–2218 (2019)

Z. Zhu, Y. Xiao, X. Song, VCM-based monotonic capacitor switching scheme for SAR ADC. Electron. Lett. 49, 327–329 (2013)

Acknowledgements

This work is supported by the Science and Technology on Low-Light-Level Night Vision Laboratory (No.61424120503162412005) and Wuhu and Xidian University special fund for industry-university-research cooperation (Project No.: XWYCXY-012020013-HT).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Chen, Y., Yuan, Y., Tang, H. et al. Analysis and Design of an Efficient 8-Bit 2b/Cycle SAR ADC with Multiple Calibration Techniques. Circuits Syst Signal Process 41, 2541–2565 (2022). https://doi.org/10.1007/s00034-021-01924-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-021-01924-1