Abstract

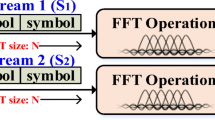

A fast Fourier transform (FFT) chip for IEEE 802.11ay wireless local area network (WLAN) standard has to stream at 20–40 Gbps with a continuous flow (CF). The earlier WLAN standard, IEEE 802.11ad, had a throughput of 7–10 Gbps. In order to double the throughput, the processing elements and memories would need to be increased, thus drastically increasing the area. The proposed 512-point radix 16 FFT architecture achieves 28-Gbps throughput occupying only 20% more chip area than the best existing 10–15-Gbps designs. Apart from that, it has all three capabilities: CF, conflict-free access (CFA), and normal order input–output. Most FFTs use two memories in a switched fashion for CF. This design uses an additional smaller input memory by exploiting the smaller wordlength of 4 bit (for 64 QAM) of OFDM. Three memories are dedicated individually to the three stages of the FFT. This architecture necessitates the development of a new technique of CF, which replaces data in memory rather than switching the memories. Substantial savings are realized by removing memory switching. Also, a simplified CFA is proposed, which further saves area. These innovations help to cut down area from switching circuits and lead to a lower complexity design. The design fabricated in SCL technology in a 120-pin package meets the 4.8 Gsps (28 Gbps) processing rate at a clock speed of 300 MHz.

Similar content being viewed by others

Availability of data and materials

Data sharing was not applicable to this article as no datasets were generated or analyzed during the current study.

References

S.-G. Chen, S.-J. Huang, M. Garrido, S.-J. Jou, Continuous-flow parallel bit-reversal circuit for MDF and MDC FFT architectures. IEEE Trans. Circuits Syst. I Regul. Pap. 61(10), 2869–2877 (2014)

Y. Chen, Y. Lin, Y. Tsao, C. Lee, A 2.4-Gsample/s DVFS FFT processor for MIMO OFDM communication systems. IEEE J. Solid State Circuits 43(5), 1260–1273 (2008)

T. Cho, H. Lee, J. Park, C. Park, A high-speed low-complexity modified radix-\(2^5\) FFT processor for gigabit WPAN applications. In: IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1259–1262 (2011)

H.L. Davila, C. Liu, W. Liu, S. Huang, S. Jou, S. Chen, A 802.15.3c/802.11ad compliant 24 Gb/s FFT processor for 60 GHz communication systems. In \(28^{th}\) IEEE International System-on-Chip Conference (SOCC), pp. 44–48 (2015)

C. Hsiao, Y. Chen, C. Lee, A generalized mixed-radix algorithm for memory-based FFT processors. IEEE Trans. Circuits Syst. II Express Briefs 57(1), 26–30 (2010)

S.-C. Hsu, S.-J. Huang, S.-G. Chen, S.-C. Lin, M. Garrido, A 128-point multi-path SC FFT architecture. In: 2020 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–5 (2020)

S.-J. Huang, S.-G. Chen, A high-throughput radix-16 FFT processor with parallel and normal input/output ordering for IEEE 802.15.3c systems. IEEE Trans. Circuits Syst. I Regul. Pap. 59(8), 1752–1765 (2012)

S.H.S. Jatana, N.M. Desai, SCL 180nm CMOS foundry: high reliability ASIC design for aerospace applications. In: 19th International Symposium on VLSI Design and Test, pp. 1–2 (2015)

B. Jo, M. Sunwoo, New continuous-flow mixed-radix (CFMR) FFT processor using novel in-place strategy. IEEE Trans. Circuits Syst. I Regul. Pap. 52(5), 911–919 (2005)

E.J. Kim, M.H. Sunwoo, High speed eight-parallel mixed-radix FFT processor for OFDM systems. In: IEEE International Symposium of Circuits and Systems (ISCAS) pp. 1684–1687 (2011)

N. Le Ba, T.T.-H. Kim, An area efficient 1024-point low power radix-\(2^2\) FFT processor with feed-forward multiple delay commutators. IEEE Trans. Circuits Syst. I Regul. Pap. 65(10), 3291–3299 (2018)

H. Lee, M. Shin, A high-speed low-complexity two-parallel radix-\(2^4\) FFT/IFFT processor for UWB applications. In: IEEE Asian Solid-State Circuits Conference, pp. 284–287 (2007)

S. Liu, D. Liu, A high-flexible low-latency memory-based FFT processor for 4G, WLAN, and future 5G. IEEE Trans. Very Large Scale Integr. Syst. 27(3), 511–523 (2018)

T.T.B. Nguyen, H. Lee, High-throughput low-complexity mixed-radix FFT processor using a dual-path shared complex constant multiplier. J. Semicond. Technol. Sci. 17(1), 101–109 (2017)

K. Parhi, VLSI Digital Signal Processing Systems: Design and Implementation (Wiley, New York, 2007)

R. Radhouane, P. Liu, C. Modlin, Minimizing the memory requirement for continuous flow FFT implementation: continuous flow mixed mode FFT (CFMM-FFT). In: IEEE International Symposium on Circuits and Systems (ISCAS), pp. 116–119 (2000)

S. Tang, J. Tsai, T. Chang, A 2.4-GS/s FFT processor for OFDM-based WPAN applications. IEEE Trans. Circuits Syst. II Express Briefs 57(6), 451–455 (2010)

Y. Tian, Y. Hei, Z. Liu, Z. Di, et al. A memory-based FFT processor using modified signal flow graph with novel conflict-free address schemes. J-STAGE IEICE Electron. Express 14(15), 20178005 (2017)

Y. Tian, Y. Hei, Z. Liu, Q. Shen, Z. Di, T. Chen, A modified signal flow graph and corresponding conflict-free strategy for memory-based FFT processor design. IEEE Trans. Circuits Syst. II Express Briefs 66(1), 106–110 (2019)

P.-Y. Tsai, C.-Y. Lin, A generalized conflict-free memory addressing scheme for continuous-flow parallel-processing FFT processors with rescheduling. IEEE Trans. Very Large Scale Integr. Syst. 19(12), 2290–2302 (2011)

C. Wang, Y. Yan, X. Fu, A high-throughput low-complexity radix - \(2^{4}\) - \(2^{2}\) - \(2^{3}\) FFT/IFFT processor with parallel and normal Input/Output order for IEEE 802.11ad systems. IEEE Trans. Very Large Scale Integr. Syst. (2014)

K. Xia, B. Wu, T. Xiong, T. Ye, A memory-based FFT processor design with generalized efficient conflict-free address schemes. IEEE Trans. Very Large Scale Integr. Syst. 25(6), 1919–1929 (2017)

H.E. Yantir, W. Guo, A. M. Eltawil, F.J. Kurdahi, K.N. Salama, An ultra-area-efficient 1024-point in-memory FFT processor. Micromachines 10(8), 509 (2019)

L. Yu Wei, L. Hsuan Yu, L. Chen Yi, A 1-GS/s FFT/IFFT processor for UWB applications. IEEE J. Solid State Circuits 40(8), 1726–1735 (2005)

Acknowledgements

The authors would like to thank Semi-conductor Laboratory, Chandigarh, for providing fabrication facilities.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Ethics Approval

Not applicable.

Consent to Participate

Not applicable.

Consent for Publication

Not applicable.

Code Availability

Code can be made available on request.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Agarwal, S., Ahamed, S.R., Gogoi, A. et al. A 28-Gbps Radix-16, 512-Point FFT Processor-Based Continuous Streaming OFDM for WiGig. Circuits Syst Signal Process 41, 2871–2897 (2022). https://doi.org/10.1007/s00034-021-01917-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-021-01917-0