Abstract

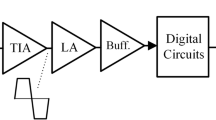

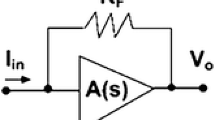

In this article, a wide-bandwidth, fully differential transimpedance amplifier (TIA) is implemented in Taiwan Semiconductor Manufacturing Company 90-nm complementary metal–oxide–semiconductor technology. The regulated cascode circuit has low input impedance and is used for the input stage of the TIA. The core amplifier is a fully differential amplifier circuit, paralleling with a differentiator that is capable of enhancing the bandwidth of the TIA. The inductorless TIA has a differential transimpedance gain of 40 dBΩ, a bandwidth of 25.85 GHz, and an average input-referred current noise density of 25 pA/√Hz. The TIA chip has a power consumption of 29 mW with a supply voltage of 1 V, and the chip area is 0.164 mm2. In the chip testing, the 32-Gb/s non-return-to-zero (NRZ) and the 40-Gb/s four-level pulse amplitude modulation (PAM-4) eye diagrams are measured and are sufficiently clear. Our TIA can be applied in a 32-Gb/s NRZ and a 40-Gb/s PAM-4 optical receiver.

Similar content being viewed by others

Data Availability

The measured data has been included in this article, and the parts of the design parameters of the circuit components are shown in this article. The structure and detail of the TIA circuit has been presented in this article, and the readers can refer to the content of this article to reproduce this circuit design. The DOI of the relevant references for this work has also been provided in this article.

References

S. Bhoja, PAM4 signaling for intra-data center and data center to data center connectivity, in DCI Optical Fiber Communication Conference (2017), pp. W4D-5. https://doi.org/10.1364/OFC.2017.W4D.5

C.F. Campbell, M.S. Heins, M.Y. Kao, M.E. Muir, J.M. Carroll A 0.15-μm GaAs MHEMT transimpedance amplifier IC for 40-Gb/s applications, in IEEE MTT-S International Microwave Symposium Digest (2002), pp. 79–82. https://doi.org/10.1109/MWSYM.2002.1011563

D. Caruth, S.C. Shen, D. Chan, M. Feng, J. Schutt-Aine, A 40 Gb/s integrated differential PIN+ TIA with DC offset control using InP SHBT technology, in 24th Annual Technical Digest GaAs IC Symposium (2002), pp. 59–62. https://doi.org/10.1109/10.1109/GAAS.2002.1049029

Q. Cheng, M. Bahadori, M. Glick, S. Rumley, K. Bergman, Recent advances in optical technologies for data centers: a review. Optica 5, 1354–1370 (2018). https://doi.org/10.1364/OPTICA.5.001354

R. Costanzo, S.M. Bowers, A current reuse regulated cascode CMOS transimpedance amplifier with 11-GHz bandwidth. IEEE Microw. Wirel. Compon. Lett. 28, 816–818 (2018). https://doi.org/10.1109/LMWC.2018.2854594

S. Facchin, S. Zhou, M. Power, A. Jain, C. Scarcella, C. Antony, P. Townsend, P. Ossieur, A 20Gbaud/s PAM-4 CMOS optical receiver using 3D solenoid based bandwidth enhancement, in IEEE 60th International Midwest Symposium on Circuits and Systems (2017), pp. 723–726. https://doi.org/10.1109/MWSCAS.2017.8053025

IEEE, P802.3bs 200GbE & 400GbE task force (2021). http://www.ieee802.org/3/bs/public/index.html. Accessed 27 Jan. 2021

J.D. Ingham, R.V. Penty, I.H. White, P. Westbergh, J.S. Gustavsson, Å. Haglund, A. Larsson, 32 Gb/s multilevel modulation of an 850 nm VCSEL for next-generation datacommunication standards, in CLEO: Laser Science and Photonic Applications (2011). https://doi.org/10.1364/CLEO_SI.2011.CWJ2

P. Kale, A. Tumma, H. Kshirsagar, O. Ramrakhyani, T. Vinode, Fibre channel over ethernet: a beginners perspective, in International Conference on Recent Trends in Information Technology (2011), pp. 438–443. https://doi.org/10.1109/ICRTIT.2011.5972328

J. Kim, J.F. Buckwalter, Bandwidth enhancement with low group-delay variation for a 40-Gb/s transimpedance amplifier. IEEE Trans. Circuits Syst. I-Regul. 57, 1964–1972 (2010). https://doi.org/10.1109/TCSI.2010.2041502

C. Knochenhauer, B. Sedighi, F. Ellinger, 40 Gbit/s transimpedance amplifier with high linearity range in 0.13 μm SiGe BiCMOS. Electron. Lett. 47, 605–606 (2011) doi: https://doi.org/10.1049/el.2011.0455

J. Lee, High-speed circuit designs for transmitters in broadband data links. IEEE J. Solid-State Circuits 41, 1004–1015 (2006). https://doi.org/10.1109/JSSC.2006.872871

C.F. Liao, S.I. Liu, A 40Gb/s transimpedance-AGC amplifier with 19dB DR in 90nm CMOS, in IEEE International Solid-State Circuits Conference (2007), pp. 54–586. https://doi.org/10.1109/ISSCC.2007.373584

Q. Pan, Y. Wang, C.P. Yue, A 42-dBΩ 25-Gb/s CMOS transimpedance amplifier with multiple-peaking scheme for optical communications. IEEE Trans. Circuits Syst. II-Express Briefs 67, 72–76 (2020). https://doi.org/10.1109/TCSII.2019.2901601

E. Säckinger, Broadband Circuits for Optical Fiber Communication (Wiley, New Jersey, 2005)

S. Saeedi, S. Menezo, G. Pares, A. Emami, A 25 Gb/s 3D-integrated CMOS/silicon-photonic receiver for low-power high-sensitivity optical communication. J. Lightwave Technol. 34, 2924–2933 (2015). https://doi.org/10.1109/JLT.2015.2494060

C.W. Seng, T.Y. Sern, Y.K. Seng, A low power wideband differential transimpedance amplifier for optical receivers in 0.18-μm CMOS, in IEEE 11th International New Circuits and Systems Conference (2013). https://doi.org/10.1109/NEWCAS.2013.6573594

Y. Xie, D. Li, Y. Liu, M. Liu, Y. Zhang, X. Wang, L. Geng, Low-noise high-linearity 56Gb/s PAM-4 optical receiver in 45nm SOI CMOS. IEEE Int. Sympos. Circuit Syst. (2018). https://doi.org/10.1109/ISCAS.2018.8351224

T.Y. Yao, D. Li, Y. Xie, P.Y. Chiang, Z.L. Hong, A low-noise 56Gbps PAM-4 linear optical receiver in 40nm CMOS, in 14th IEEE International Conference on Solid-State and Integrated-Circuit Technology (2018). https://doi.org/10.1109/ICSICT.2018.8565734

L. Zeng, X. Song, J. Man, W. Chen, W. Zhou, PAM4 transmission for short reach optical interconnection, in 14th international conference on communication systems and networks (2015). https://doi.org/10.1109/ICOCN.2015.7203720

Acknowledgements

This work was supported partly by the Taiwan Semiconductor Research Institute and the Taiwan Ministry of Science and Technology, under the contract MOST 109-2224-E-992-001.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Jou, JJ., Shih, TT. & Hsu, HW. 32-Gb/s NRZ and 40-Gb/s PAM-4 Transimpedance Amplifier Paralleling with a Differentiator for Bandwidth Enhancement in 90-nm CMOS Technology. Circuits Syst Signal Process 41, 621–635 (2022). https://doi.org/10.1007/s00034-021-01826-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-021-01826-2