Abstract

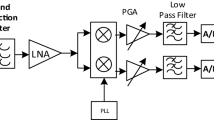

In this paper, an inverter-based true time delay (TTD) cell for timed array receivers is proposed. The proposed TTD cell is designed in TSMC 0.18 µm CMOS technology for multi-GHz operations. The delay cell is made from an all-pass filter by Padé approximation. The first-order all-pass filter is built by combining a constant gain stage and a low pass stage based on the approximation. The constant gain stage consists of two NMOS transistors. The low pass stage is created with an inverter cell, cascaded with a PMOS transistor. Active true time delay cells are used in delay lines (commonly in cascaded topology) to develop a timed array system. Because of that, size of the TTD cell is critical and is an important design factor. So in this paper, an inductorless inverter-based wideband TTD cell is proposed. The wideband input impedance matching is achieved without bulky inductors using the resistive feedback technique in the inverter cell. More than wideband input impedance matching, flat gain, and flat delay response for the TTD cell are obtained with this technique. With the inverter-based input and complementary output structure, the TTD cell is a self-biased circuit. So, additional bias circuit is not needed. The proposed TTD cell consumes 8.7 mW from a 1.8 V supply. The achieved wideband delay is 10.6pS. Only 3% delay deviation over the 1–5 GHz band is observed, and this shows the excellent quality of the provided delay. The insertion loss is − 3.9 dB and is tolerable for a TTD cell. The input and output wideband impedance matching is ensured, and the S11 and S22 parameters are lower than -14.7 dB and − 10.9 dB, respectively. At last, the proposed TTD cell shows good linear performance, and IIP3 is around + 11.7 dBm.

Similar content being viewed by others

Availability of Data and Materials

All data generated or analyzed during this study are included in this published article (and its Supplementary Information files).

References

S.R. Aghazadeh, H. Martinez, A. Saberkari, and E.J. Alarcon Cot, Tunable wide–band second-order all-pass filter–based time delay cell using active inductor. In 32nd Conference on Design of Circuits and Integrated Systems, (DCIS) (IEEE, 2018), pp. 1–5

S.R. Aghazadeh, H. Martinez, A. Saberkari, E.J. Alarcon Cot, Tunable active inductor-based second-order all-pass filter as a time delay cell for multi-GHz operation. Circuits, Syst Signal Proces 38, 1–17 (2019)

S.R. Aghazadeh, H. Martinez, A. Sssaberkari, and E.J. Alarcon Cot, 5GHz CMOS all-pass filter-based true time delay cell. Electronics, 8(1), 16 (2019)

P. Ahmadi, B. Maundy, A.S. Elwakil, L. Belostotski, A. Madanayake, A, new second-order all-pass filter in 130-nm CMOS. IEEE Trans Circuits Syst II: Express Briefs 63(3), 249–253 (2015)

P. Ahmadi, M.H. Taghavi, L. Belostotski, and A. Madanayake, A, 0.13 μm CMOS current-mode all-pass filter for multi-GHz operation. IEEE Trans Very Large Scale Integr (VLSI) Systems, 23(12), 2813–2818 (2015)

E. Brookner, Practical Phased-Array Antenna Systems (Artech House Inc., Boston, 1991).

Y.W. Chang, T.C. Yan, and C.N. Kuo, Wideband time-delay circuit. In 2011 6th European Microwave Integrated Circuit Conference (IEEE, 2011), pp 454–457

S.F. Chao, J.J. Kuo, C.L. Lin, M.D. Tsai, H. Wang, A DC-115 GHz low-power, wideband amplifier using splitting-load inductive peaking technique. IEEE Microwave Wirel Components Lett 18(7), 482–484 (2008)

Y. Chen, W. Li, An ultra-wideband pico-second true-time-delay circuit with differential tunable active inductor. Analog Integr Circuits Signal Process 91(1), 9–19 (2017)

Y. Chen, W. Li, Compact and broadband variable true-time delay line with DLL-based delay-time control. Circuits, Syst Signal Process 37(3), 1007–1027 (2018)

W. Chunhua, W. Qiuzhen, A 0.18 μm CMOS low noise amplifier using a current reuse technique for 3.1–10.6 GHz UWB receivers. J Semicond 32(8), 085002 (2011)

S.K. Garakoui, E.A. Klumperink, B. Nauta, F.E. van Vliet, Compact cascadable gm-C all-pass true time delay cell with reduced delay variation over frequency. IEEE J Solid-state Circuits 50(3), 693–703 (2015)

S.K. Garakoui, E.A. Klumperink, B. Nauta, and F.E. van Vliet, Phased-array antenna beam squinting related to frequency dependency of delay circuits. In: 2011 41st European Microwave Conference (IEEE, 2011), pp 1304–1307

J. Kim, J. Park, J.G. Kim, CMOS true-time delay IC for wideband phased-array antenna. ETRI J 40(6), 693–698 (2018)

D. Leenaerts, J. Van der Tang, C.S. Vaucher, Circuit Design for RF Transceivers (Springer, Berlin, 2007).

Q. Ma, D. Leenaerts, and R. Mahmoudi, A 10–50GHz true-time-delay phase shifter with max 3.9% delay variation. In 2014 IEEE Radio Frequency Integrated Circuits Symposium (IEEE, 2014), pp 83–86

R.J. Mailloux, Phased arrays in radar and communication systems. Phased Array Antenna Handbook, 44–60 (2005)

I. Mondal, N. Krishnapura, A 2-GHz bandwidth, 0.25–1.7 ns true-time-delay element using a variable-order all-pass filter architecture in 0.13 μm CMOS. IEEE J Solid-State Circuits 52(8), 2180–2193 (2017)

B. Nauta, Analog CMOS Filters for Very High Frequencies (Springer, Berlin, 2012).

B. Razavi, RF Microelectronics Second Edition. Pearson Education, Inc., (2012)

X. Sheng, and Z. Liu, L/S-Band 0.18 æm CMOS 6-bit Digital Phase Design. In 2016 6th International Conference on Mechatronics, Computer and Education Informationization (MCEI ,2016), Atlantis Press.

Users Guide Advanced Design System 1.5: Expressions, Measurements, and Simulation Data Processing, Agilent Technologies, (2000)

S. Voinigescu, High-Frequency Integrated Circuits (Cambridge University Press, Cambridge, 2013).

A. Yarahmadi, A. Jannesari, Two-path inverter-based low noise amplifier for 10–12 GHz applications. Microelectron J 50, 76–82 (2016)

A. Yarahmadi, A. Jannesari, Design of a highly linear gain stage with complementary derivative superposition technique. Wirel Personal Commun 106, 1–8 (2019)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Yarahmadi, A., Jannesari, A. Wideband Inductorless True Time Delay Cell Based on CMOS Inverter for Timed Array Receivers. Circuits Syst Signal Process 40, 3703–3726 (2021). https://doi.org/10.1007/s00034-021-01656-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-021-01656-2