Abstract

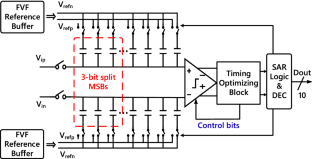

This paper presents a power-efficient successive-approximation register (SAR) analog-to-digital converter (ADC) with fast response reference buffer (RV-buffer). Several techniques are applied in the system design to improve the performance of the SAR ADC. A novel timing-redistribution SAR logic is proposed to balance the difference between required settling time for the most significant bit and the least significant bits (LSBs) in the digital-to-analog capacitor array, which reduces the incomplete settling error and releases the requirements on the RV-buffer to achieve lower power dissipation. The SAR ADC is fabricated in 40-nm CMOS technology occupying 0.13 mm\(^{2}\) area. At 1.1 V supply voltage and 80 MHz sampling frequency, the ADC achieves 50.7 dB SNDR, 69.5 dBc SFDR with a 1 MHz input at −8 dBFS. The total power consumption of the ADC is 2.99 mW, including the reference buffer power consumption of 2 mW. The Schreier FoM is 164.1 dB.

Similar content being viewed by others

References

Y. Cao, Y. Chen, Z. Ni, F. Ye, J. Ren, An 11b 80 ms/s SAR ADC with speed-enhanced SAR logic and high-linearity CDAC. In: 2018 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), pp. 18–21 (2018)

Y. Chen, J. Wang, H. Hu, F. Ye, J. Ren, A 200 ms/s, 11 bit SAR-assisted pipeline ADC with bias-enhanced ring amplifier. In: 2017 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–4 (2017)

Y. Chen, X. Zhu, H. Tamura, M. Kibune, Y. Tomita, T. Hamada, M. Yoshioka, K. Ishikawa, T. Takayama, J. Ogawa, S. Tsukamoto, T. Kuroda, Split capacitor DAC mismatch calibration in successive approximation ADC. In: 2009 IEEE Custom Integrated Circuits Conference, pp. 279–282 (2009)

Y. Chung, C. Yen, An 11-bit 100-ms/s subranged-SAR ADC in 65-nm cmos. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 25(12), 3434–3443 (2017)

Y. Chung, C. Yen, P. Tsai, B. Chen, A 12-bit 40-ms/s SAR ADC with a fast-binary-window DAC switching scheme. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 26(10), 1989–1998 (2018)

B.P. Ginsburg, A.P. Chandrakasan, 500-ms/s 5-bit ADC in 65-nm CMOS with split capacitor array DAC. IEEE J. Solid-State Circuits 42(4), 739–747 (2007)

P. Harikumar, J.J. Wikner, Design of a reference voltage buffer for a 10-bit 50 ms/s SAR ADC in 65 nm CMOS. In: 2015 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 249–252 (2015)

M. Hesener, T. Eicher, A. Hanneberg, D. Herbison, F. Kuttner, H. Wenske, A 14b 40 ms/s redundant SAR ADC with 480 mhz clock in 0.13 pm CMOS. In: 2007 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, pp. 248–600 (2007)

C. Hsu, S. Chang, C. Huang, L. Chang, Y. Shyu, C. Hou, H. Tseng, C. Kung, H. Hu, A 12-b 40-ms/s calibration-free SAR ADC. IEEE Trans. Circuits Syst. I: Regular Papers 65(3), 881–890 (2018)

Y. Hu, A. Liu, B. Li, Z. Wu, Closed-loop charge recycling switching scheme for SAR ADC. Electron. Lett. 53(2), 66–68 (2017)

G. Huang, S. Chang, Y. Lin, C. Liu, C. Huang, A 10b 200 ms/s 0.82 mw SAR ADC in 40 nm CMOS. In: 2013 IEEE Asian Solid-State Circuits Conference (A-SSCC), pp. 289–292 (2013)

J.E. Kim, T. Yoo, K. Baek, T.T. Kim, Balanced sampling switch for high linearity and a wide temperature range in low power SAR ADCs. Electron. Lett. 55(24), 1273–1275 (2019)

D. Li, Z. Zhu, R. Ding, Y. Yang, A 1.4-mw 10-bit 150-ms/s SAR ADC with nonbinary split capacitive DAC in 65-nm CMOS. IEEE Trans. Circuits and Syst. II: Exp. Br. 65(11), 1524–1528 (2018)

W. Li, F. Li, J. Liu, H. Li, Z. Wang, A 13-bit 160 ms/s pipelined subranging-SAR ADC with low-offset dynamic comparator. In: 2017 IEEE Asian Solid-State Circuits Conference (A-SSCC), pp. 225–228 (2017)

C. Liu, S. Chang, G. Huang, Y. Lin, A 10-bit 50-ms/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 45(4), 731–740 (2010)

C. Liu, S. Chang, G. Huang, Y. Lin, C. Huang, C. Huang, L. Bu, C. Tsai, A 10b 100 ms/s 1.13 mw SAR ADC with binary-scaled error compensation. In: 2010 IEEE International Solid-State Circuits Conference—(ISSCC), pp. 386–387 (2010)

C. Liu, C. Kuo, Y. Lin, A 10 bit 320 ms/s low-cost SAR ADC for IEEE 802.11ac applications in 20 nm CMOS. IEEE J. Solid-State Circuits 50(11), 2645–2654 (2015)

M. Liu, A. van Roermund, P. Harpe, A 7.1fj/conv.-step 88 db-sfdr 12b SAR ADC with energy-efficient swap-to-reset. In: ESSCIRC Conference 2016: 42nd European Solid-State Circuits Conference, pp. 409–412 (2016)

M. Liu, A.H.M. van Roermund, P. Harpe, A 7.1-fj/conversion-step 88-db SFDR SAR ADC with energy-free swap to reset. IEEE J Solid-State Circuits 52(11), 2979–2990 (2017)

W. Liu, P. Huang, Y. Chiu, A 12b 22.5/45 ms/s 3.0 mw 0.059 mm2 CMOS SAR ADC achieving over 90 db SFDR. In: 2010 IEEE International Solid-State Circuits Conference-(ISSCC), pp. 380–381 (2010)

M. Akbari, O. Hashemipour, F. Khateb, F. Moradi, An energy-efficient DAC switching algorithm based on charge recycling method for SAR ADCs. Microelectron. J. 82, 29–35 (2018)

M. Akbari, O. Hashemipour, M. Nazari, F. Moradi, A charge sharing-based switching scheme for SAR ADCs. Int. J. Circuit Theory Appl. 47(7), 1188–1198 (2019)

T. Miki, T. Morie, K. Matsukawa, Y. Bando, T. Okumoto, K. Obata, S. Sakiyama, S. Dosho, A 4.2 mw 50 ms/s 13 bit CMOS SAR ADC with SNR and SFDR enhancement techniques. IEEE J. Solid-State Circuits 50(6), 1372–1381 (2015)

C. Park, T. Chen, K. Noh, D. Zhou, S. Prakash, M.N. Alizadeh, A.I. Karsilayan, D. Chen, R.L. Geiger, J. Silva-Martinez, A 12-bit 125-ms/s 25-bit/cycle SAR-based pipeline ADC employing a self-biased gain boosting amplifier. IEEE Trans. Circuits Syst. I: Regular Pap. 67, 1–12 (2020)

J. Park, D. Kim, T. An, M. Kim, G. Ahn, S. Lee, 12 b 50 ms/s 0.18 \(\mu \)m CMOS SAR ADC based on highly linear C-R hybrid DAC. Electron. Lett. 56(3), 119–121 (2020)

Y. Roh, D. Chang, S. Ryu, A 40-nm cmos 12b 120-ms/s nonbinary SAR-assisted SAR ADC with double clock-rate coarse decision. IEEE Trans. Circuits Syst. II: Exp. Br. 67(12), 1 (2020)

Y. Shen, Z. Zhu, S. Liu, Y. Yang, A reconfigurable 10-to-12-b 80-to-20-ms/s bandwidth scalable SAR ADC. IEEE Trans. Circuits Syst. I: Regular Pap. 65(1), 51–60 (2018)

L. Sun, B. Li, A.K.Y. Wong, W.T. Ng, K.P. Pun, A charge recycling sar adc with a LSB-down switching scheme. IEEE Trans. Circuits Syst. I: Regular Pap. 62(2), 356–365 (2015)

W. Tseng, W. Lee, C. Huang, P. Chiu, A 12-bit 104 ms/s sar adc in 28 nm cmos for digitally-assisted wireless transmitters. IEEE J. Solid-State Circuits 51(10), 2222–2231 (2016)

W. Tung, S. Huang, An energy-efficient 11-bit 10-ms/s SAR ADC with monotonie switching split capacitor array. In: 2018 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–5 (2018)

D. Xu, H. Jiang, L. Qiu, X. Yu, J. Wang, Z. Zhang, C. Zhu, S. Xu, A linearity-enhanced 10-bit 160-ms/s SAR ADC with low-noise comparator technique. IEEE Trans Very Large Scale Integr (VLSI) Syst 27(9), 1990–1997 (2019)

J. Xue, H. Ghaedrahmati, J. Jin, A 10-bit 160ms/s SAR ADC with fast-response reference voltage buffer. In: 2018 14th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), pp. 1–3 (2018)

T. Yousefi, A. Dabbaghian, M. Yavari, An energy-efficient DAC switching method for SAR ADCs. IEEE Trans. Circuits Syst. II: Exp. Br. 65(1), 41–45 (2018)

H. Zhang, J. Sun, J. Zhang, R. Zhang, A. ChanCarusone, A low-power pipelined-SAR ADC using boosted bucket-brigade device for residue charge processing. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 26(9), 1763–1776 (2018)

M. Zhang, K. Noh, X. Fan, E. Sánchez-Sinencio, A 0.8–1.2 v 10–50 ms/s 13-bit subranging pipelined-sar adc using a temperature-insensitive time-based amplifier. IEEE J. Solid-State Circuits 52(11), 2991–3005 (2017)

Y. Zhu, C. Chan, U. Chio, S. Sin, U. Seng-Pan, R.P. Martins, F. Maloberti, A 10-bit 100-ms/s reference-free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits 45(6), 1111–1121 (2010)

Acknowledgements

We would like to thank the Chinese National Nature Science Foundation (No. 61974092) for funding this research.

Funding

Chinese National Nature Science Foundation (No. 61974092)

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflicts of interest/Competing interests

No conflicts or interests with any authorities or person

Availability of data and material

All data used in this essay are collected by the authors mentioned in the essay without other sources

Code availability

No software application or custom code are utilized in the research process

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Hu, M., Jin, J., Guo, Y. et al. A Power-Efficient SAR ADC with Optimized Timing-Redistribution Asynchronous SAR Logic in 40-nm CMOS. Circuits Syst Signal Process 40, 3125–3142 (2021). https://doi.org/10.1007/s00034-020-01643-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-020-01643-z