Abstract

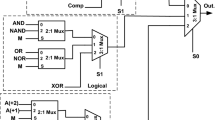

Gate diffusion input (GDI) method using a simple cell makes it possible to design low-power logic gates with reduced chip area and less complexity. In this work, a novel design of single-bit optimized reversible logic-based magnitude arithmetic unit (RMAU) circuit, using appropriate standard reversible gates with carbon nanotube (CNT) field-effect transistors (CNTFETs), based on modified-GDI (m-GDI) method for nanoscales is presented. In order to optimize the performance of the proposed circuit, and to achieve minimum power consumption and propagation delay, transistor sizes are adjusted using the non-dominated sorting genetic algorithm II (NSGA-II) in MATLAB tool. The simulation results show improvement in evaluating the figure of merits in worst-case delay and power consumption of the proposed optimized arithmetic unit, in comparison with a non-optimized RMAU circuit using a similar design method but counterpart structures. The effects of different process parameters (such as the diameter of CNTs) and voltage and temperature (PVT) variations are extensively evaluated by the Monte Carlo procedure in standard 32 nm technology utilizing the Synopsys HSPICE simulator. According to the outcomes obtained, the proposed optimized RMAU circuit is robust against PVT variations and noise-tolerable criterions, compared to those competitors with similar design in non-optimized conditions. The proposed optimized and non-optimized circuits were used in image processing as real environment assessments, and results depicted their excellent ability in being implemented in various large reversible-based applications, such as future generations of FPGA chips and CNTFET-based computers.

Similar content being viewed by others

References

E. Abiri, Z. Bezareh, A. Darabi, The optimum design of RAM cell based on the modified-GDI method using non-dominated sorting genetic algorithm II (NSGA-II). J. Intell. Fuzzy Syst. 32(6), 4095–4108 (2017)

E. Abiri, Z. Bezareh, A. Darabi, The Optimum Design of a Master-Slave D-Flip Flap (M/S-DFF) Based on the Modified GDI (m-GDI) Method Using Non-dominated Sorting Genetic Algorithm II (NSGA-II). 24th Iranian Conference on Electrical Engineering (ICEE) (2016), pp. 720–725

E. Abiri, A. Darabi, A novel modified GDI method-based clocked M/S-TFF for future generation microprocessor chips in nano schemes. Microprocess. Microsyst. J. 60, 122–137 (2018)

E. Abiri, A. Darabi, Design of low power and high read stability 8T-SRAM memory based on the modified gate diffusion input (m-GDI) in 32 nm CNTFET technology. Microelectron. J. 46(12), 1351–1363 (2015)

E. Abiri, A. Darabi, A novel design of low power and high read stability ternary SRAM (T-SRAM), memory based on the modified gate diffusion input (m-GDI) method in nanotechnology. Microelectron. J. 58, 44–59 (2016)

E. Abiri, A. Darabi, A. Sadeghi, Gate-diffusion input (GDI) method for designing energy-efficient circuits in analogue voltage-mode fuzzy and QCA systems. Microelectron. J. 87, 81–100 (2019)

E. Abiri, A. Darabi, S. Salem, Design of multiple-valued logic gates using gate-diffusion input for image processing applications. Comput. Electric. Eng. J. 69, 142–157 (2018)

E. Abiri, A. Darabi, Reversible logic-based magnitude comparator (RMC) circuit using modified-GDI technique for motion detection applications in image processing. Microprocess. Microsyst. J. 72, 102928 (2020)

M. Ahmadinejad, M.H. Moaiyeri, F. Sabetzadeh, Energy and area efficient imprecise compressors for approximate multiplication at nanoscale. AEU Int. J. Electron. Commun. 110, 1434–8411 (2019)

D. Akinwande, J. Liang, S. Chong, Y. Nishi, H.S. Wong, Analytical ballistic theory of carbon nanotube transistors: experimental validation, device physics, parameter extraction, and performance projection. J. Appl. Phys. 104(12), 124514 (2008)

D. Akinwande, Y. Nishi, H.-S. Philip Wong, An analytical derivation of the density of states, effective mass, and carrier density for achiral carbon nanotubes. IEEE Trans. Electron. Dev. 55(1), 289–297 (2008)

M. Ali, M. Ahmed, M. Chrzanowska-Jeske, in Proceedings of the 16th International Conference on Nanotechnology. Fast and accurate evaluation of delay in CNFET circuits (2016), pp. 659–662

Arizona State University, Tucson, AZ, USA. Predictive Technology Models. http://www.eas.asu.edu/~ptm (2019)

C.H. Bennett, Logical reversibility of computation. IBM J. Res. Dev. 17, 525–532 (1973)

Y. Chang, Z. Bouzarkouna, D. Devegowda, Multi-objective optimization for rapid and robust optimal oilfield development under geological uncertainty. Comput. Geosci. 19, 933 (2015)

K. Deb, A. Pratap, S. Agarwal, T. Meyarivan, A fast and elitist multiobjective genetic algorithm: NSGA-II. IEEE Trans. Evol. Comput. 6(2), 182–197 (2002)

K. Deb, M. Abouhawwash, An optimality theory-based proximity measure for set-based multiobjective optimization. IEEE Trans. Evolut. Comput. 20(4), 515–528 (2016)

J. Deng, Device Modeling and Circuit Performance Evaluation For Nanoscale Devices: Silicon Technology Beyond 45 nm Node and Carbon Nanotube Field Effect Transistors. Ph.D. Dissertation, Stanford University, Stanford, 2007

V. Dokania, R. Verma, M. Guduri, A. Islam, Design of 10T full adder cell for ultralow-power applications. Ain Shams Eng. J. 9(4), 2363–2372 (2018)

L. Gonzalez, J. Periuax, G. Bugeda, D. Lee, Design optimization using advanced artificial intelligent system coupled to hybrid-game strategies. In: Proceedings of the 3rd International Workshop on Artificial Intelligence in Science and Technology (AISAT), pp. 1–10 (2009)

H. Hashempour, F. Lombardi, Device model For ballistic CNFETs using the first conducting band. IEEE Des. Test Comput. 25, 178–186 (2008)

A.L. Jaimes, C.A. Coellooello, An introduction to multi objective evolutionary algorithms and some of their potential uses in biology. Appl. Comput. Intell. Biol. Part Stud. Comput. Intell. Book Ser. 122, 79–102 (2008)

P. Khatter, N. Pandey, K. Gupta, An Arithmetic and Logical Unit using Reversible Gates. International Conference on Computing, Power and Communication Technologies (GUCON) (2018), pp. 476–480

M.H. Moaiyeri, K. Navi, O. Hashemipour, Design and evaluation of CNFET-based quaternary circuits. Circuits Syst. Signal Process. 31(5), 1631–1652 (2012)

M.H. Moaiyeri, A. Rahi, F. Sharifi, K. Navi, Design and evaluation of energy efficient carbon nanotube FET-based quaternary minimum and maximum circuits. J. Appl. Res. Technol. 15(3), 233–241 (2017)

A. Morgenshtein, A. Fish, I.A. Wagner, Gate-diffusion input (GDI): a power-efficient method for digital combinatorial circuits. IEEE Trans. VLSI Syst. 10, 566–581 (2002)

H. Naseri, S. Timarchi, Low-power and fast full adder by exploring new XOR and XNOR gates. IEEE Trans. VLSI Syst. 26(8), 1481–1493 (2018)

V. Pareto, Cours D’Economie Politique, vol. I, II (F. Rouge, Lausanne, 1896)

B.C. Paul, S. Fujita, M. Okajima, T.H. Lee, H.S.P. Wong, Y. Nishi, Impact of a process variation on nanowire and nanotube device performance. IEEE Trans. Electron. Dev. 54(9), 2369–2376 (2007)

H.V. Ravish Aradhya, B.V. Praveen Kumar, K.N. Muralidhara, Design of control unit for low power AU using reversible logic. Int. Conf. Commun. Technol. Syst. Des. 30, 631–638 (2012)

Y. Safaei Mehrabani, M. Eshghi, Noise and process variation tolerant, low-power, high-speed, and low-energy full adders in CNFET technology. IEEE Trans. VLSI Syst. 24(11), 3268–3281 (2016)

M.S. Sankhwar, R. Khatri, Design of high speed low power reversible logic adder using HNG gate. Int. J. Eng. Res. Appl. 4(1), 152–159 (2014)

T.N. Sasamal, A. Mohan, Efficient design of reversible logic ALU using coplanar quantum-dot cellular automata. J. Circuits Syst. Comput. 27(2), 1850021 (2018)

H. Shahidipour, A. Ahmadi, K. Maharatna, in Proceedings of 12th International Symposium on Integrated Circuits. Effect of variability in SWCNT-based logic gates (2010), pp. 252–255

M. Shams, M. Haghparast, K. Navi, Novel reversible multiplier circuit in nanotechnology. World Appl. Sci. J 3, 806–810 (2008)

V. Shukla, O.P. Singh, G.R. Mishra, R.K. Tiwari, Reversible realization of N-bit arithmetic circuit for low power loss ALU applications. Proc. Comput. Sci. 125, 847–854 (2018)

Stanford University CNTFET Model. http://nano.stanford.edu/model.php? (2019)

N. Srinivas, K. Deb, Multiobjective optimization using non-dominated sorting in genetic algorithms. Evolut. Comput. 2(3), 221–248 (1994)

K.B.K. Teo, R.G. Lacerda, M.H. Yang, A.S. Teh, L.A.W. Robinson, S.H. Dalal, N.L. Rupesinghe, M. Chhowalla, S.B. Lee, D.A. Jefferson, D.G. Hasko, G.A.J. Amaratunga, W.L. Milne, P. Legagneux, L. Gangloff, E. Minoux, J.P. Schnell, D. Pribat, Carbon nanotube technology for solid state and vacuum electronics. IEEE Proc. Circuits Dev. Syst. 151(5), 443–451 (2004)

A. TorkzadehMahani, P. Keshavarzian, A novel energy-efficient and high speed full adder using CNTFET. Microelectron. J. 61, 79–88 (2017)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Abiri, E., Darabi, A., Salehi, M.R. et al. Optimized Gate Diffusion Input Method-Based Reversible Magnitude Arithmetic Unit Using Non-dominated Sorting Genetic Algorithm II. Circuits Syst Signal Process 39, 4516–4551 (2020). https://doi.org/10.1007/s00034-020-01382-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-020-01382-1