Abstract

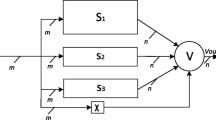

In this paper, we propose a new static fault-tolerant technique, viz. modulo-quad-transistor, combining redundancy at circuit level with that at functional level, which offers considerably lower failure rate over all the popular fault-tolerant methods. The new approach of compound redundancy also combines the benefits of the two, reducing the overall performance problems by decreasing area, delay and power overheads. The method is free from the complex interconnection problems of the newly proposed quadded logic with quadded transistor method and also offers higher reliability than it. Low design cost and high reliability of the proposed method have made it suitable for designing fault-tolerant systems for many critical practical applications. Extensive simulation results using some of the ISCAS 85 benchmark circuits along with the detailed theoretical analysis have also been provided to demonstrate the superiority of the proposed method.

Similar content being viewed by others

References

L. Anghel, M. Nicolaidis, Defects tolerant logic gates for unreliable future nanotechnologies, in Computational and Ambient Intelligence, vol. 4507, Lecture Notes in Computer Science, ed. by F. Sandoval, A. Prieto, J. Cabestany, M. Graña (Springer, Berlin, 2007), pp. 422–429

D. Bryan, The ISCAS’85 benchmark circuits and netlist format. Technischer Bericht, Microelectronics Center of North Carolina (1988)

H. Chen, J. Han, F. Lombardi, A transistor-level stochastic approach for evaluating the reliability of digital nanometric CMOS circuits, in Proceedings IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems, pp. 60–67 (2011)

J. Chen, G. Venkataramani, H.H. Huang, Exploring dynamic redundancy to resuscitate faulty PCM blocks. ACM J. Emerg. Technol. Comput. Syst. 10(4), 1–23 (2014)

Y. Cui, W. Li, X. Zhang, Memory controller design based on quadruple modular redundant architecture, in Proceedings International Conference on Computer Engineering and Networks, pp. 905–912 (2013)

A.H. El-Maleh, K. Daud, Simulation-based method for synthesizing soft error tolerant combinational circuits. IEEE Trans. Reliab. 64(3), 935–948 (2015)

A.H. El-Maleh, B.M. Al-Hashimi, A. Melouki, A. Al-Yamani, Transistor-level based defect-tolerance for reliable nanoelectronics, in Robust Computing with Nano-scale Devices, Lecture Notes in Electrical Engineering, ed. by C. Huang (Springer, Dordrecht, 2010), pp. 29–49

J. Han, H. Chen, J. Liang, P. Zhu, Z. Yang, F. Lombardi, A stochastic computational approach for accurate and efficient reliability evaluation. IEEE Trans. Comput. 63(6), 1336–1350 (2014)

J. Han, E. Leung, L. Leibo, F. Lombardi, A fault-tolerant technique using quadded logic and quadded transistors. IEEE Trans. Very Large Scale Integr. VLSI Syst. 23(8), 1562–1566 (2015)

E. Hatami, H. Salarieh, N. Vosoughi, Design of a fault tolerated intelligent control system for a nuclear reactor power control: using extended Kalman filter. J. Process Control 24(7), 1076–1084 (2014)

C. He, M.F. Jacome, G. de Veciana, A reconfiguration-based defect-tolerant design paradigm for nanotechnologies. IEEE Des. Test. Comput. 22(4), 316–326 (2005)

S. Hong, S. Kim, A low-cost mechanism exploiting narrow-width values for tolerating hard faults in ALU. IEEE Trans. Comput. 64(9), 2433–2446 (2015)

M.M. Ibrahim, K. Asami, M. Cho, Reconfigurable fault tolerant avionics system, in Proceedings IEEE Aerospace Conference, pp. 1–12 (2013)

P.A. Jensen, Quadded NOR logic. IEEE Trans. Reliab. 12(3), 22–31 (1963)

P. Jonker, J.A.B. Fortes, Toward hardware-redundant, fault-tolerant logic for nanoelectronics. IEEE Des. Test. Comput. 22(4), 328–339 (2005)

M. Juliato, C. Gebotys, A quantitative analysis of a novel SEU-resistant SHA-2 and HMAC architecture for space missions security. IEEE Trans. Aerosp. Electron. Syst. 49(3), 1536–1554 (2013)

F. Khan, Transistor-level defect-tolerant techniques for reliable design: at the nanoscale. Master of Science Thesis, King Fahd University of Petroleum and Minerals (2009)

E.P. Kim, N.R. Shanbhag, Soft N-modular redundancy. IEEE Trans. Comput. 61(3), 323–336 (2012)

F. Kocan, D.G. Saab, Dynamic fault diagnosis of combinational and sequential circuits on reconfigurable hardware. J. Electron. Test. 23(5), 405–420 (2007)

Z. Latifi, A. Karimi, A TMR genetic voting algorithm for fault-tolerant medical robot. Proc. Comput. Sci. 42, 301–307 (2014)

R.E. Lyions, W. Vanderkulk, The use of triple modular redundancy to improve computer reliability. IBM J. Res. Dev. 6(2), 200–209 (1962)

A. Mukherjee, A.S. Dhar, Real-time fault-tolerance with hot-standby topology for conditional sum adder. Microelectron. Reliab. 55(3–4), 704–712 (2015)

A. Mukherjee, A.S. Dhar, Fault tolerant architecture design using quad-gate-transistor redundancy. IET Circuits Dev. Syst. 9(3), 152–160 (2015)

A. Mukherjee, A.S. Dhar, New triple-transistor based defect-tolerant systems for reliable digital architectures, in Proceedings IEEE Int’l Symposium on Circuits and Systems (ISCAS), pp. 1917–1920 (2015)

K. Nikolic, A. Sadek, M. Forshaw, Architectures for reliable computing with unreliable nanodevices, in Proceedings IEEE Conference on Nanotechnology, pp. 254–259 (2001)

W.H. Pierce, Interwoven redundant logic. J. Frankl. Inst. 277(1), 55–85 (1964)

W. Qian, X. Li, M.D. Riedel, K. Bazargan, D.J. Lilja, An architecture for fault-tolerant computation with stochastic logic. IEEE Trans. Comput. 60(1), 93–105 (2011)

A.T. Sheikh, A.H. El-Maleh, M.E.S. Elrabaa, S.M. Sait, A. Fault, Tolerance technique for combinational circuits based on selective-transistor redundancy. IEEE Trans. Very Large Scale Integr. VLSI Syst. 25(1), 224–237 (2017)

J.G. Tryon, Redundant logic circuitry, U. S. Patent 2,942,193, June 21, 1960

J.G. Tryon, Quadded logic, in Redundancy Techniques for Computing Systems, ed. by R.H. Wilcox, W.C. Mann (Spartan Books, Washington, 1962), pp. 205–208

J. von Neumann, Probabilistic logic and the synthesis of reliable organisms from unreliable components, in Automata Studies: Annals of Mathematics Studies, vol. 34, ed. by C.E. Shannon, J. McCarthy (Princeton University Press, Princeton, 1956), pp. 43–98

H. Zhou, Y.H. Tang, J.F. Jiang, Design and implementation of scalable autonomous centralized fault-tolerant scheme for satellite system. Adv. Mater. Res. 532–533, 813–817 (2012)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Mukherjee, A., Dhar, A.S. Reliable VLSI Architecture Design Using Modulo-Quad-Transistor Redundancy Method. Circuits Syst Signal Process 37, 5595–5615 (2018). https://doi.org/10.1007/s00034-018-0837-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-018-0837-1