Abstract

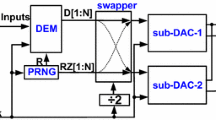

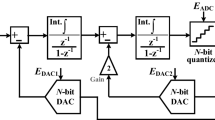

This paper presents a dynamic element matching (DEM) decoder incorporating both intersymbol interference (ISI) and mismatch error shaping. From the analysis of ISI error in multi-bit DACs, an algorithm is developed that deterministically controls the element transitions, such that on each conversion cycle the instantaneous number of on transitions is set to a constant value, while the instantaneous number of off transitions varies with the decoder input signal. The technique achieves greater ISI error mitigation than previous approaches using less hardware. To further reduce the logic area, a hierarchical DEM structure, whereby the DEM decoder is split into multiple sub-DEM decoders, is presented.

Similar content being viewed by others

Change history

01 December 2017

The original version of the article unfortunately contained an error in figure. The presentation of Fig. 2 is incorrect. Figure 1 was erroneously duplicated and published as Fig. 2 in the article.

References

J. De Maeyer, P. Rombouts, L. Weyten, Addressing static and dynamic errors in unit element multibit DACs. Electron. Lett. 39, 1038–1039 (2003)

I. Galton, Why dynamic-element-matching DACs work. IEEE Trans. Circuits Syst. II Express Briefs 57, 69–74 (2010)

I. Galton, Spectral shaping of circuit errors in digital-to-analog converters. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 44, 808–817 (1997)

W. Peijun, S. Nan, A random DEM technique with minimal element transition rate for high-speed DACs, in 2014 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1155–1158 (2014)

J. Remple, I. Galton, The effects of inter-symbol interference in dynamic element matching DACs. IEEE Trans. Circuits Syst. I Regul. Pap. 64, 14–23 (2017)

L. Risbo, R. Hezar, B. Kelleci, H. Kiper, M. Fares, Digital approaches to ISI-mitigation in high-resolution oversampled multi-level D/A converters. IEEE J. Solid State Circuits 46, 2892–2903 (2011)

A. Sanyal, L. Chen, N. Sun, Dynamic element matching with signal-independent element transition rates for multibit modulators. IEEE Trans. Circuits Syst. I Regul. Pap. 62, 1325–1334 (2015)

A. Sanyal, W. Peijun, S. Nan, A thermometer-like mismatch shaping technique with minimum element transition activity for multibit DACs. IEEE Trans. Circuits Syst. II Express Briefs 61, 461–465 (2014)

A. Sanyal, N. Sun, Dynamic element matching techniques for static and dynamic errors in continuous-time multi-bit modulators. IEEE J. Emerg. Sel. Top. Circuits Syst. 5(4), 598–611 (2015)

R. Schreier, B. Zhang, Noise-shaped multibit D/A convertor employing unit elements. Electron. Lett. 31, 1712–1713 (1995)

T. Shui, R. Schreier, F. Hudson, Mismatch shaping for a current-mode multibit delta-sigma DAC. IEEE J. Solid State Circuits 34, 331–338 (1999)

Acknowledgements

This work has been supported by Enterprise Ireland, Innovation Partnership Project IP/2013/0271 co-funded by the Irish Government and the EU European Regional Development Fund (ERDF). The authors are grateful to the funding agency Enterprise Ireland for enabling this research in collaboration with our partner Analog Devices, Limerick, Ireland.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

O’Brien, V., Scanlan, A.G. & Mullane, B. A Reduced Hardware ISI and Mismatch Shaping DEM Decoder. Circuits Syst Signal Process 37, 2299–2317 (2018). https://doi.org/10.1007/s00034-017-0681-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-017-0681-8