Abstract

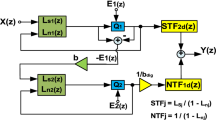

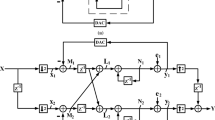

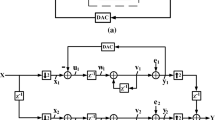

In this paper, a second-order asynchronous delta–sigma modulator is proposed based on the active-RC integrators. The operational transconductance amplifiers used in the integrators are improved by employing a class-AB structure with bulk-driven input drivers and quasi-floating gate method in subthreshold region. These circuitry approaches provide better linearity, signal-to-noise ratio and speed for the integrators and hence an overall improvement in the performance of the modulator. Mathematical analyses of the second-order modulator confirm a higher center frequency compared to a first-order one. The increased center frequency transfers redundancy distortions to higher frequencies, which results in wider input bandwidth and better linearity. The proposed ASDM designed in TSMC 130 nm CMOS Technology with a center frequency of 1.73 kHz at supply voltage of 250 mV with a signal-to-noise-plus-distortion ratio of 67.3 dB and the power consumption of 30 nW.

Similar content being viewed by others

References

M. Akbari, O. Hashemipour, A 0.6-V, 0.4-\(\upmu \)W bulk-driven operational amplifier with rail-to-rail input/output swing. Analog Integr. Circuits Signal Process. 86(2), 341–351 (2016). doi:10.1007/s10470-015-0686-9

R.S. Assaad, J. Silva-Martinez, The recycling folded cascode: a general enhancement of the folded cascode amplifier. IEEE J. Solid-State Circuits 44(9), 2535–2542 (2009)

M. Akbari, O. Hashemipour, A 63-dB gain OTA operating in subthreshold with 20-nW power consumption. Int. J. Circuit Theory Appl. 45(6), 843–850 (2017)

W. Bai, Z. Zhu, A 0.5-V 9.3-ENOB 68-nW 10-kS/s SAR ADC in 0.18-\(\upmu \)m CMOS for biomedical applications. Microelectron. J. 59, 40–46 (2017)

A. Babaie-Fishani, B. Van Keymeulen, P. Rombouts, Analytical expressions for the distortion of asynchronous sigma–delta modulators. IEEE Trans. Circuits Syst. II Express Briefs 60(8), 472–476 (2013)

S. Baswa, A.J. Lopez-Martin, J. Ramirez-Angulo, R.G. Carvajal, Low-voltage micropower super class AB CMOS OTA. Electron. Lett. 40(4), 216–217 (2004)

F. Colodro, A. Torralba, M. Laguna, Continuous-time sigma-delta modulator with an embedded pulsewidth modulation. IEEE Trans. Circuits Syst. I Regul. Pap. 55(3), 775–785 (2008)

F. Colodro, A. Torralba, J.L. Mora, J.M. Martinez-Heredia, An analog squaring technique based on asynchronous sigma-delta modulation. IEEE Trans. Circuits Syst. II Express Briefs 56(8), 629–633 (2009)

P.K. Chan, Y. Chen, Gain-enhanced feedforward path compensation technique for pole-zero cancellation at heavy capacitive loads. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 50(12), 933–941 (2003)

J.M. Carrillo, G. Torelli, R.P.-A. Valverde, J.F. Duque-Carrillo, 1-V rail-to-rail CMOS opamp with improved bulk-driven input stage. IEEE J. Solid-State Circuits 42(3), 508–517 (2007)

J. Daniels, W. Dehaene, M.S. Steyaert, A. Wiesbauer, A/D conversion using asynchronous delta-sigma modulation and time-to-digital conversion. IEEE Trans. Circuits Syst. I Regul. Pap. 57(9), 2404–2412 (2010)

L.H. Ferreira, S.R. Sonkusale, A 0.25-V 28-nW 58-dB dynamic range asynchronous delta sigma modulator in 130-nm digital CMOS process. IEEE Trans. Very Large Scale Integr. VLSI Syst. 23(5), 926–934 (2015)

L.H. Ferreira, S.R. Sonkusale, A 60-dB gain OTA operating at 0.25-V power supply in 130-nm digital CMOS process. IEEE Trans. Circuits Syst. I Regul. Pap. 61(6), 1609–1617 (2014)

F. Gerfers, Continuous-Time Sigma-Delta A/D Conversion: Fundamentals, Performance Limits and Robust Implementations, vol. 21 (Springer, Nww York, 2006)

W. Hussain, H. Fakhoury, P. Desgreys, Y. Blaquière, Y. Savaria, An asynchronous delta-modulator based A/D converter for an electronic system prototyping platform. IEEE Trans. Circuits Syst. I Regul. Pap. 63(6), 751–762 (2016)

T. Kulej, F. Khateb, 0.4-V bulk-driven differential-difference amplifier. Microelectron. J. 46(5), 362–369 (2015)

F. Khateb, Bulk-driven floating-gate and bulk-driven quasi-floating-gate techniques for low-voltage low-power analog circuits design. AEU Int. J. Electron. Commun. 68(1), 64–72 (2014)

M. Kumngern, F. Khateb, 0.5 V fully differential current conveyor using bulk-driven quasi-floating-gate technique. IET Circuits Devices Syst. 10(1), 78–86 (2016)

F. Khateb, W. Jaikla, M. Kumngern, P. Prommee, Comparative study of sub-volt differential difference current conveyors. Microelectron. J. 44(12), 1278–1284 (2013)

F. Khateb, The experimental results of the bulk-driven quasi-floating-gate MOS transistor. AEU Int. J. Electron. Commun. 69(1), 462–466 (2015)

E. Lopez-Morillo, R.G. Carvajal, F. Munoz, H. El Gmili, A. Lopez-Martin, J. Ramirez-Angulo, E. Rodriguez-Villegas, A 1.2-V 140-nW 10-bit sigma-delta modulator for electroencephalogram applications. IEEE Trans. Biomed. Circuits Syst. 2(3), 223–230 (2008)

M. Liu, K. Pelzers, R. van Dommele, A. van Roermund, P. Harpe, A106nW 10 b 80 kS/s SAR ADC with duty-cycled reference generation in 65 nm CMOS. IEEE J. Solid-State Circuits 51(10), 2435–2445 (2016)

A.J. López-Martín, S. Baswa, J. Ramirez-Angulo, R.G. Carvajal, Low-voltage super class AB CMOS OTA cells with very high slew rate and power efficiency. IEEE J. Solid-State Circuits 40(5), 1068–1077 (2005)

N. Mirzaie, H. Shamsi, G.-S. Byun, Resilient design of current steering DACs using a transistor level approach. Analog Integr. Circuits Signal Process. 90(1), 29–41 (2017)

S. Ouzounov, E. Roza, J.A. Hegt, G. van der Weide, A.H. van Roermund, Analysis and design of high-performance asynchronous sigma-delta modulators with a binary quantizer. IEEE J. Solid-State Circuits 41(3), 588–596 (2006)

E. Roza, Analog-to-digital conversion via duty-cycle modulation. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 44(11), 907–914 (1997)

J. Ramirez-Angulo, R.G. Carvajal, J.A. Galán, A. López-Martín, A free but efficient low-voltage class-AB two-stage operational amplifier. IEEE Trans. Circuits Syst. II Express Briefs 53(7), 568–571 (2006)

A. Sarkar, S.S. Panda, Design of a power efficient, high slew rate and gain boosted improved recycling folded cascode amplifier with adaptive biasing technique. Microsyst. Technol. 23(9), 4255–4262 (2017). doi:10.1007/s00542-016-2969-1

V. Singh, N. Krishnapura, S. Pavan, Compensating for quantizer delay in excess of one clock cycle in continuous-time \(\Delta \Sigma \) modulators. IEEE Trans. Circuits Syst. II Express Briefs 57(9), 676–680 (2010)

W. Sansen, Distortion in elementary transistor circuits. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 46(3), 315–325 (1999)

I. Seo, R.M. Fox, Comparison of quasi-/pseudo-floating gate techniques and low-voltage applications. Analog Integr. Circuits Signal Process. 47(2), 183–192 (2006)

T. Sánchez-Rodríguez, J.A. Gomez-Galan, R.G. Carvajal, M. Sánchez-Raya, F. Muñoz, J. Ramírez-Angulo, A 1.2-V 450-\(\upmu \)W \(G_m\)-\(C\) bluetooth channel filter using a novel gain-boosted tunable transconductor. IEEE Trans. Very Large Scale Integr. VLSI Syst. 23(8), 1572–1576 (2015)

Y. Yang, C. Li, D.M. Binkley, Continuous-time sigma–delta modulator design for wireless biomedical sensing applications, in 2010 IEEE 11th Annual Wireless and Microwave Technology Conference (WAMICON) (2010), pp. 1–4

A.F. Yeknami, F. Qazi, A. Alvandpour, Low-power DT \(\Delta \Sigma \) modulators using SC passive filters in 65 nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 61(2), 358–370 (2014)

X. Zhao, H. Fang, T. Ling, J. Xu, Transconductance improvement technique for bulk-driven OTA in nanometre CMOS process. Electron. Lett. 51(22), 1758–1759 (2015)

X. Zhao, Q. Zhang, M. Deng, Super class-AB bulk-driven OTAs with improved slew rate. Electron. Lett. 51(19), 1488–1489 (2015)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Akbari, M., Hashemipour, O. & Moradi, F. Design and Analysis of an Ultra-Low-Power Second-Order Asynchronous Delta–Sigma Modulator. Circuits Syst Signal Process 36, 4919–4936 (2017). https://doi.org/10.1007/s00034-017-0658-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-017-0658-7