Abstract

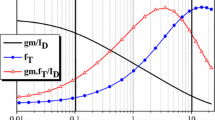

The purpose of this paper is to introduce a methodology for multi-objective radio frequency (RF) low-noise amplifier (LNA) optimization using an analytical model of the MOS transistor in combination with genetic computation. The optimum performance is defined by a figure of merit (FoM) that considers both the power efficiency and the RF performance of the system. Using a short-channel EKV model, the analysis of this FoM suggests that the optimum MOS inversion level lies in the moderate inversion. This knowledge can be used as a strong starting point for the design and optimization procedures. Initially, the LNA component values are extracted using the analytical model. The model does not fully take into consideration the parasitic behaviour of the components in a real design; thus, it produces an approximation of the optimum design. The final circuit fine tuning is achieved with the use of a genetic algorithm that takes advantage of the aforementioned approximation as an initialization aiming at faster convergence. To demonstrate the effectiveness and the operation of this methodology, a 5 GHz common source LNA with inductive degeneration has been designed using the proposed design and optimization methodology. The same design has been statistically investigated using Monte Carlo simulations to address process variability as well as temperature and supply voltage variations. Finally, the optimization procedure is demonstrated also on different topologies including cascode or common gate structures, as well as multi-stage distributed and resistive shunt feedback amplifiers.

Similar content being viewed by others

References

A. Antonopoulos, Nanoscale RF CMOS Transceiver Design, PhD Thesis (Technical University of Crete, Chania, Greece, 2013)

A. Antonopoulos, M. Bucher, K. Papathanasiou, N. Makris, R.K. Sharma, P. Sakalas, M. Schroter, CMOS RF noise, scaling and compact modeling for RFIC design, in IEEE Radio Frequency Integrated Circuits (RFIC) Symposium (USA, 2013), pp. 53–56

A. Antonopoulos, M. Bucher, K. Papathanasiou, N. Makris, N. Mavredakis, R.K. Sharma, P. Sakalas, M. Schroter, Modeling of high-frequency noise of silicon CMOS transistors for RFIC design. Int. J. Numer. Model. Electron. Netw. Devices Fields 27(5–6), 802–811 (2014)

A. Antonopoulos, M. Bucher, K. Papathanasiou, N. Mavredakis, N. Makris, R.K. Sharma, P. Sakalas, M. Schroter, CMOS small-signal and thermal noise modeling at high frequencies. IEEE Trans. Electron Devices 60(11), 3726–3733 (2013)

V.H.V. Baroncini, O.C. Gouveia-Filho, Design of RF CMOS low noise amplifiers using a current based MOSFET model, in Symposium on Integrated Circuits and Systems Design (SBCCI) (Brazil, 2004), pp. 81–87

M.-A. Chalkiadaki, Characterization and Modeling of Nanoscale MOSFET for Ultra-Low Power RF IC Design, PhD Thesis (EPFL, Lausanne, Switzerland, 2016)

M.-A. Chalkiadaki, C.C. Enz, RF small-signal and noise modeling including parameter extraction of nanoscale MOSFET from weak to strong inversion. IEEE Trans. Microw. Theory Tech. 63(7), 2173–2184 (2015)

H.-H. Chen, M.-H. Chen, C.-Y. Tsai, Optimization of low noise amplifier designs by genetic algorithms, in International Symposium on Electromagnetic Theory (EMTS) (Japan, 2013), pp. 493–496

H.-S. Chen, H.-Y. Tsai, L.-X. Chuo, Y.-K. Tsai, L.-H. Lu, A 5.2 GHz full-integrated RF front-end by T/R switch, LNA, and PA co-design with 3.2-dB NF and +25.9-dBm output power, in IEEE Solid-State Circuits Conference (A-SSCC), (China, 2015), pp. 1–4

C.-C. Chen, Y.-C. Wang, A 2.4/5.2/5.8 triple-band common-gate cascode CMOS low-noise amplifier. Circuits Syst. Signal Process. 39(9), 3477–3489 (2016)

C.-C. Chen, Y.-C. Wang, A dual-wideband CMOS LNA using gain-bandwidth product optimization technique. Circuits Syst. Signal Process. 36(2), 495–510 (2016)

C.C. Enz, M.-A. Chalkiadaki, M. Mangla, Low-power analog/RF circuit design based on the inversion coefficient, in IEEE European Solid-State Circuits Conference (ESSCIRC) (Austria, 2015), pp. 202–208

C.C. Enz, Y. Cheng, MOS transistor modeling for RF IC design. IEEE J. Solid-State Circuits 35(2), 186–201 (2000)

C.C. Enz, E.A. Vittoz, Charge-Based MOS Transistor Modeling: The EKV Compact Model for EKV Model for Low-Power and RF IC Design (Wiley, Chichester, 2006)

C.T. Fu, H. Lakdawala, S.S. Taylor, K. Soumyanath, A 2.5 GHz 32 nm 0.35 \(\text{mm}^2\) 3.5 dB NF-5 dBm \({P}_{1\,{\rm db}}\) fully differential CMOS push-pull LNA with integrated 34dBm T/R switch and ESD protection, in IEEE International Conference on Solid-State Circuits Digest of Technical Papers (ISSCC), (USA, 2011), pp. 56–58

J.C. Guo, I.-M. Lin, A compact RF CMOS modeling for accurate high-frequency noise simulation in sub-100-nm MOSFETS. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 27(9), 1684–1688 (2008)

J.C. Guo, Y.-H. Tsai, A broadband and scalable lossy substrate model for RF noise simulation and analysis in nanoscale MOSFETs with various pad structures. IEEE Trans. Microw. Theory Tech. 57(2), 271–281 (2009)

C.-L. Hsieh, M.-H. Wu, J.-H. Cheng, J.-H. Tsai, T.-W. Huang, A 0.6 V 336\(\mu \)W 5-GHz LNA using a low-voltage and gain-enhancement architecture, in IEEE Microwave Symposium Digest (IMS), (USA, 2013), pp. 1–3

G. Konstantopoulos, K. Papathanasiou, A. Samelis, Optimization of RF circuits by expert monitored genetic computation, in IEEE International Symposium on Circuits and Systems (ISCAS) (Greece, 2006), pp. 5247–5250

P.I. Mak, R. Martins, A 0.46 \(\text{ mm }^2\) 4 dB-NF unified receiver front-end for full-band mobile TV in 65 nm CMOS, in IEEE International Conference on Solid-State Circuits Digest of Technical Papers (ISSCC), (USA, 2011), pp. 172–174

A. Mangla, C.C. Enz, J.-M Sallese, Figure-of-merit for optimizing the current efficiency of low-power RF circuits, in International Conference on Mixed Design of Integrated Circuits and Systems (MIXDES) (Poland, 2011), pp. 85–89

N. Mavredakis, M. Bucher, Inversion-level based design of an RF CMOS low-noise amplifier, in IEEE International Conference on Electronics, Circuits and Systems (ICECS) (France, 2006), pp. 74–77

M.Y. Mukadam, O.G. Filho, X. Zhang, A.B. Apsel, Process variation compensation of a 4.6 GHz LNA in 65 nm CMOS, in IEEE International Symposium on Circuits and Systems (ISCAS) (France, 2010), pp. 2490–2493

A. Nieuwoudt, T. Ragheb, H. Nejati, Y. Massoud, Increasing manufacturing yield for wideband RF CMOS LNAs in the presence of process variations, in International Symposium on Quality Electronic Design (ISQED) (USA, 2007), pp. 801–806

K.B. Östman, M. Englund, O. Viitala, M. Kaltiokallio, K. Stadius, K. Koli, J. Ryynanen, A 2.5-GHz receiver front end with Q-boosted post LNA N-path filtering in 40-nm CMOS. IEEE Trans. Microw. Theory Tech. 62(9), 2071–2083 (2014)

A. Papadimitriou, M. Bucher, Optimization of RF low noise amplifier design using analytical model and genetic computation, in Mixed Design of Integrated Circuits and Systems (MIXDES) (Poland, 2017), pp. 302–307

V. Papageorgiou, S. Vlassis, CMOS LNA optimization techniques: comparative study, in IEEE International Conference on Electronics, Circuits and Systems (ICECS) (Greece, 2010), pp. 82–84

M. Rezvani, S. Ardalan, K. Raahemifar, High gain, low power, CMOS current reused LNA with noise optimization, in IEEE Electrical and Computer Engineering Annual Canadian Conference (CCECE), (Canada, 2013), pp. 1–6

J.-M. Sallese, M. Bucher, F. Krummenacher, P. Fazan, Inversion charge linearization in MOSFET modeling and rigorous derivation of the EKV compact model. Solid-State Electron. 57(4), 677–683 (2003)

D.K. Shaeffer, T.H. Lee, A 1.5-V 1.5-GHz CMOS low noise amplifier. IEEE J. Solid-State Circuits 32(5), 745–759 (1997)

A. Shameli, P. Heydari, A novel optimization technique for ultra-low power RFICs, in International Symposium on Low Power Electronics and Design (ISLPED) (Germany, 2006), pp. 274–279

A. Shameli, P. Heydari, Ultra-low power RFIC design using moderately inverted MOSFETs: an analytical/experimental study, in IEEE Radio Frequency Integrated Circuits (RFIC) Symposium (USA, 2006), pp. 470–473

I. Song, J. Jeon, H.-S. John, J. Kim, B.G. Park, J.D. Lee, H. Shin, A simple figure of merit for RF MOSFET for low noise amplifier design. IEEE Electron Device Lett. 29(12), 1380–1382 (2008)

T. Stücke, Energieeffiziente HF-Front-End-Schaltungsarchitekturen am Beispiel von ZigBee-Empfängern, PhD Thesis (Universität Duisburg-Essen, Duisburg, Germany, 2007)

T. Stücke, N. Christoffers, R. Kokozinski, S. Kolnsberg, B.J. Hosticka, The impact of technology parameters on the performance of common-gate LNAs, in International Conference on Mixed Design of Integrated Circuits and Systems (MIXDES) (Poland, 2006), pp. 74–77

T. Taris, J.B. Begueret, Y. Deval, A 60 \(\mu \)W LNA for 2.4 GHz wireless sensors network applications, in IEEE Radio Frequency Integrated Circuits (RFIC) Symposium (USA, 2011), pp. 23–28

S. Thijs, M.I. Natarajan, D. Linten, V. Vassilev, T. Daenen, A. Scholten, R. Degraeve, P. Wambacq, G. Groesenken, ESD protection for a 5.5 GHz LNA in 90 nm RF CMOS-Implementation concepts, constraints and solutions, in IEEE Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD 2004), (USA, 2004), pp. 1–10

S. Toofan, A. Abrishamifar, A. Razhmati, M. Graziano, G.R. Lahiji, S.A. Moniri, A 5.5-GHz 3 mW LNA with inductive degenerative CMOS LNA noise figure calculation in IEEE International Conference on Microelectronics (ICM) (UAE, 2008), pp. 308–312

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Papadimitriou, A., Bucher, M. Multi-objective Low-Noise Amplifier Optimization Using Analytical Model and Genetic Computation. Circuits Syst Signal Process 36, 4963–4993 (2017). https://doi.org/10.1007/s00034-017-0634-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-017-0634-2