Abstract

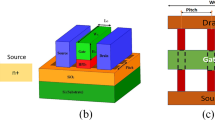

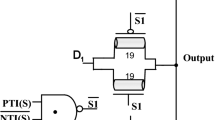

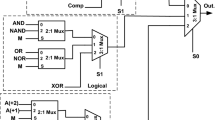

Nowadays, portable multimedia devices have been widely used in low-power structures. Additionally, using approximate computing and multiple-valued logic (MVL) can lead to lower power consumption. Carbon nanotube field effect transistor (CNTFET), with a determinable threshold voltage, is an appropriate choice for designing MVL circuits. In this study, a new approximate ternary full adder is presented based on CNTFET switching logic with the aim of reducing area and energy consumption. The results obtained by the Synopsys HSPICE simulator with the Stanford 32 nm CNTFET technology show that the average power consumption, delay, and energy consumption of the proposed designs are significantly lower than the other conventional and state-of-the-art CNTFET-based ternary circuits. In addition, the proposed ternary full adder is applied to reduce the steps of a ternary multiplier structure and some important metrics such as normalized error distance and energy-error trade-off are calculated to evaluate the efficiency of the proposed circuits. The layout of the proposed design is also plotted to estimate area consumption. Moreover, the approximate design is used for image processing applications such as image multiplying and image blending and the results are accordingly compared with the exact outputs. Similarly, the evaluated peak signal-to-noise ratio and mean structural similarity index metric indicate that the proposed approximate full adder has a proper accuracy for image processing applications.

Similar content being viewed by others

References

G. Balamurugan, N.R. Shanbhag, The twin-transistor noise-tolerant dynamic circuit technique. JSSC 36(2), 273–280 (2001)

N.H. Bastani, M.H. Moaiyeri, K. Navi, Carbon nanotube field effect transistor switching logic for designing efficient ternary arithmetic circuits. J. Nanoelectron. Optoelectron. 12(2), 118–129 (2017)

G. Cho, F. Lombardi, Design and process variation analysis of CNTFET-based ternary memory cells. Integr. VLSI J. 54(c), 97–108 (2016)

J. Deng, H.-S. Wong, A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application–Part I: model of the intrinsic channel region. IEEE Trans. Electron Devices 54(12), 3186–3194 (2007)

J. Deng, H.-S. Wong, A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application–Part II: full device model and circuit performance benchmarking. IEEE Trans. Electron Devices 54(12), 3195–3205 (2007)

E. Dubrova, Multiple-valued logic in VLSI: challenges and opportunities, in Proceedings of NORCHIP (1999), pp. 340–350

S.A. Ebrahimi, P. Keshavarzian, S. Sorouri, M. Shahsavari, Low power CNTFET-based ternary full adder cell for nanoelectronics. IJSCE 2(2), 291–295 (2012)

J. Huang, M. Zhu, S. Yang, P. Gupta, W. Zhang, S.M. Rubin, G. Garreton, A physical design tool for carbon nanotube field-effect. JETC 8(3), 25 (2012)

S.L. Hurst, Multiple-valued logic—its status and future. IEEE Trans. Comput. 33(12), 1160–1179 (1984)

P. Keshavarzian, R. Sarikhani, A novel CNTFET-based ternary full adder. Circuits Syst. Signal Process. 33(3), 665–679 (2014)

J. Liang, L. Chen, J. Han, F. Lombardi, Design and evaluation of multiple valued logic gates using pseudo N-type carbon nanotube FETs. IEEE Trans. Nanotechnol. 13(4), 695–708 (2014)

J. Liang, J. Han, F. Lombardi, New metrics for the reliability of approximate and probabilistic adders. IEEE Trans. Comput. 62(9), 1760–1771 (2013)

S. Lin, Y.B. Kim, F. Lombardi, CNTFET-based design of ternary logic gates and arithmetic circuits. IEEE Trans. Nanotechnol. 10(2), 217–225 (2011)

P.L. McEuen, M. Fuhrer, H. Park, Single-walled carbon nanotube electronics. IEEE Trans. Nanotechnol. 1(1), 78–85 (2002)

M.H. Moaiyeri, A. Doostaregan, K. Navi, Design of energy-efficient and robust ternary circuits for nanotechnology. IET Circuits Devices Syst. 5(4), 285–296 (2011)

M. Moghaddam, M.H. Moaiyeri, M. Eshghi, Design and evaluation of an efficient schmitt trigger-based hardened latch in CNTFET technology. IEEE Trans. Device Mater. Reliab. 17(1), 267–277 (2017)

A. Momeni, J. Han, P. Montuschi, F. Lombardi, Design and analysis of approximate compressors for multiplication. IEEE Trans. Comput. 64(4), 984–994 (2015)

M. Orshansky, Approximate computing: an emerging paradigm for energy-efficient design, in 18th IEEE European Test Symposium (ETS) (2013), pp. 1-6

A. Panahi, F. Sharifi, M.H. Moaiyeri, K. Navi, CNFET-based approximate ternary adders for energy-efficient image processing applications. Microprocessors. 47(Part B), 454–465 (2016)

M. Pedram, X. Wu, A new description of MOS circuits at switch-level with applications. IEICE Trans. Fundam. 80(10), 1892–1901 (1997)

A. Raychowdhury, K. Roy, Carbon nanotube electronics: design of high-performance and low-power digital circuits. IEEE Trans. Circuits Syst. 54(11), 2391–2401 (2007)

M. Rezaeikhezeli, M.H. Moaiyeri, A. Jalali, Analysis of crosstalk effects for multiwalled carbon nanotube bundle interconnects in ternary logic and comparison with cu interconnects. IEEE Trans. Nanotechnol. 16(1), 107–117 (2017)

J.N Roy, T. Chattopadhyay, All-optical quaternary logic based information processing: challenges and opportunities, in Design and Architectures for Digital Signal Processing (InTech, Croatia, 2013) pp. 81–109

K. Roy, S. Mukhopadhyay, H. Meirmandi, Leakage current mechanisms and leakage reduction technologies in deep-submicron CMOS circuits. Proc. IEEE 91(2), 305–327 (2003)

S. Tabrizchi, H. Sharifi, F. Sharifi, K. Navi, Design of ultra low power ternary half adder and multiplier for nanotechnology. J. Nanoelectron. Optoelectron. 11(6), 730–737 (2016)

R. Venkastesan, A. Agarwal, K. Roy, A. Raghunathan, MACACO: modeling and analysis of circuits for approximate computing, in Proceedings of the International Conference on Computer-Aided Design (2011), pp. 667–673

Z. Wang, A.C. Bovik, H.R. Sheikh, E.P. Simoncelli, Image quality assessment: from error visibility to structural similarity. IEEE Trans. Image Process. 13(4), 600–612 (2004)

Z. Yang, A. Jain, J. Liang, J. Han, F. Lombardi, Approximate XOR/XNOR-based adders for inexact computing, in 13th IEEE Conference on Nanotechnology (IEEE-NANO) (2013), pp. 690–693

F. Yang, X. Wang, D. Zhang, J. Yang, D. Luo, Z. Xu et al., Chirality-specific growth of single-walled carbon nanotubes on solid alloy catalysts. Nature 510(7506), 522–524 (2014)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Bastani, N.H., Moaiyeri, M.H. & Navi, K. An Energy- and Area-Efficient Approximate Ternary Adder Based on CNTFET Switching Logic. Circuits Syst Signal Process 37, 1863–1883 (2018). https://doi.org/10.1007/s00034-017-0627-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-017-0627-1