Abstract

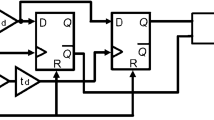

A new phase detector for high-speed applications is proposed in this paper. Due to their long reset path, conventional phase detectors can work in lower frequencies. However, the proposed phase detector has lower reset path delay in which makes it suitable for high-speed phase locked loops (PLL) and delay locked loops (DLL). Moreover, this new phase detector uses a few transistors. The proposed circuit is designed based on TSMC 0.13 \(\upmu \hbox {m}\) CMOS Technology. Simulations show lower reset path delay, blind zone and power consumption for proposed architecture in comparison with pervious related works. In addition, the circuit is able to detect phase offsets in about 80 ps and to work properly in frequencies near 3 GHz. Its blind zone is about 120 ps, while its reset path delay is about 80 ps. Furthermore, the power consumption of the proposed circuit at 128 MHz is found to be about \(134\,\upmu \hbox {W}\).

Similar content being viewed by others

References

C.T. Charles, D.J. Allstot, A calibrated phase/frequency detector for reference spur reduction in charge-pump PLLs. IEEE Trans. Circuits Syst II: Express Br. 53(9), 6–822 (2006)

R.Y. Chen, Z.Y. Yang, Modeling the high-frequency degradation of phase/frequency detectors. IEEE Trans. Circuits Syst II: Express Br. 57(5), 8–394 (2010)

W.H. Chen, M.E. Inerowicz, B. Jung, Phase frequency detector with minimal blind zone for fast frequency acquisition. IEEE Trans. Circuits Syst II: Express Br. 57(12), 40–936 (2010)

M. Gholami, Phase frequency detector using transmission gates for high speed applications. Int. J. Eng. Trans. A: Basics 29(7), 916 (2016)

M. Gholami, Total jitter of delay-locked loops due to four main jitter sources. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 24(6), 9–2040 (2016)

M. Gholami, A novel low power architecture for DLL-based frequency synthesizers. Circuits Syst Signal Process. 32(2), 781–801 (2013)

M. Gholami, G. Ardeshir, Analysis of DLL jitter due to voltage-controlled delay line. Circuits Syst Signal Process. 32(5), 35–2119 (2013)

W.H. Lee ,J.D. Cho, S.D. Lee. A high speed and low power phase-frequency detector and charge-pump, in Design Automation Conference, 1999. Proceedings of the ASP-DAC’99. Asia and South Pacific (IEEE, 1999) pp. 269–272

M. Mansuri , D. Liu , C.K. Yang . Fast frequency acquisition phase-frequency detectors for GSa/s phase-locked loops, in Solid-State Circuits Conference, 2001. ESSCIRC 2001. Proceedings of the 27th European (IEEE, 2001), pp. 333–336)

M. Soyuer, R.G. Meyer, Frequency limitations of a conventional phase-frequency detector. IEEE J. Solid-State Circuits 25(4), 22–1019 (1990)

J. Strzelecki, S. Ren, Near-zero dead zone phase frequency detector with wide input frequency difference. Electron. Lett. 51(14), 61–1059 (2015)

G.Y. Tak, S.B. Hyun, T.Y. Kang, B.G. Choi, S.S. Park, A, 6.3-9-ghz cmos fast settling pll for mb-ofdm uwb applications. IEEE J. Solid-State Circuits 40(8), 9–1671 (2005)

W.J. Yun, H.W. Lee, D. Shin, S. Kim, A, 3.57 Gb/s/pin low jitter all-digital DLL with dual DCC circuit for GDDR3 DRAM in 54-nm CMOS technology. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 19(9), 22–1718 (2011)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Gholami, M. Phase Detector with Minimal Blind Zone and Reset Time for GSamples/s DLLs. Circuits Syst Signal Process 36, 3549–3563 (2017). https://doi.org/10.1007/s00034-016-0485-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-016-0485-2