Abstract

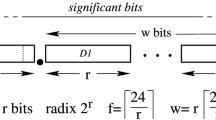

In today’s world, high-power computing applications such as image processing, digital signal processing, graphics, robotics require enormous computing power. These applications use matrix operations, especially matrix multiplication. Multiplication operations require a lot of computational time and are also complex in design. We can use field-programmable gate arrays as low-cost hardware accelerators along with a low-cost general-purpose processor instead of a high-cost application-specific processor for such applications. In this work, we employ an efficient Strassen’s algorithm for matrix multiplication and a highly efficient run-time-reconfigurable floating-point multiplier for matrix element multiplication. The run-time-reconfigurable floating-point multiplier is implemented with custom floating-point format for variable-precision applications. A very efficient combination of Karatsuba algorithm and Urdhva Tiryagbhyam algorithm is used to implement the binary multiplier. This design can effectively adjust the power and delay requirements according to different accuracy requirements by reconfiguring itself during run time.

Similar content being viewed by others

References

A. Amira, A. Bouridane, P. Milligan, P. Sage, A high throughput FPGA implementation of a bit-levelmatrix-matrix product, in Proceedings of the 43rd IEEE Midwest Symposium on Circuits and Systems, (2000), pp. 396–399

N. Anane, H. Bessalah, M. Issad, K. Messaoudi, Hardware implementation of variable precision multiplication on FPGA, in 4th International Conference on Design & Technology of Integrated Systems in Nanoscale Era, (2009), pp. 77–81

R.K. Bathija, R.S. Meena, S. Sarkar, R. Sahu, Low power high speed \(16\times 16\) bit multiplier using Vedic mathematics. Int. J. Comput. Appl. 59(6), 41–44 (2012)

F. Bensaali, A. Amira, A. Bouridane, An FPGA based coprocessor for large matrix product implementation, in IEEE International Conference on Field-Programmable Technology (FPT), (2003), pp. 292–295

F. Bensaali, A. Amira, R. Sotudeh, Floating-point matrix product on FPGA, in IEEE/ACS International Conference on Computer Systems and Applications (AICCSA), (2007), pp. 466–473

I. Bravo, P. Jime’nez, M. Mazo, J.L. Lazaro, J.J. de las Heras, A.Gardel, Different proposals to matrix multiplication based on FPGAs, in IEEE International Symposium on Industrial Electronics (ISIE), (2007), pp. 1709–1714

C. Brunelli, P. Salmela, J. Takala, J. Nurmi, A flexible multiplier for media processing, in IEEE Workshop on Signal processing System Design and Implementation, (2005), pp. 70–74

P. Corsonello, S. Perri, P. Zicari, A matrix product coprocessor for FPGA embedded soft processors, in International Symposium on Signals, Circuits and Systems (ISSCS), (2005), pp. 489–492

H.S. Dhillon, A. Mitra, A reduced-bit multiplication algorithm for digital arithmetic. World Acad. Sci. Eng. Technol. 19, 719–724 (2008)

IEEE 754-2008, IEEE Standard for Floating-Point Arithmetic (2008)

A. Jain, B. Dash, A.K. Panda, M. Suresh, FPGA design of a fast 32-bit floating point multiplier unit, in International Conference on Devices, Circuits and Systems (ICDCS), (2012), pp. 545–547

B. Jeevan, S. Narender, C.V. Krishna Reddy, K. Sivani, A high speed binary floating point multiplier using Dadda algorithm, in International Multi-Conference on Automation, Computing, Communication, Control and Compressed Sensing, (2013), pp. 455–460

T.-C. Lee, M. White, M. Gubody, Matrix multiplication on FPGA-based platform, in Proceedings of the World Congress on Engineering and Computer Science (WCECS), vol. 1 (2013)

K. Manolopoulos, D. Reisis, V.A. Chouliaras, An efficient multiple precision floating-point multiplier, in 18th IEEE International Conference on Electronics, Circuits and Systems (ICECS), (2011), pp. 153–156

A. Mehta, C.B. Bidhul, S. Joseph, P, Jayakrishnan, Implementation of single precision floating point multiplier using Karatsuba algorithm, in 2013 International Conference on Green Computing, Communication and Conservation of Energy (ICGCE), (2013), pp. 254–256

B. Parhami, Computer Arithmetic (Oxford University Press, Oxford, 2000)

M. Poornima, S.K. Patil, S.K. Shivukumar, H. Sanjay, Implementation of multiplier using Vedic algorithm. Int. J. Innov. Technol. Explor. Eng. 2(6), 219–223 (2013), ISSN: 2278-3075

B.S. Premananda, S. Samarth, S.S. Pai, B. Shashank, S.S. Bhat, Design and implementation of 8-bit Vedic multiplier. Int. J. Adv. Res. Electr. Electron. Instrum. Eng. 2(12), 5877–5882 (2013)

M.J. Rao, S. Dubey, A high speed and area efficient Booth recoded wallace tree multiplier for fast arithmetic circuits, in 2012 Asia Pacific Conference on Postgraduate Research in Microelectronics & Electronics (PRIMEASIA), (2012), pp. 220–223

D.N. Sonawane, M.S. Sutaone, I. Malek, Resource efficient 64-bit floating point matrix multiplication algorithm using FPGA, in TENCON, (2009), pp. 1–5

R.S.S. Teja, A. Madhusudhan, FPGA implementation of low-area floating point multiplier using Vedic mathematics. Int. J. Emerg. Technol. Adv. Eng. 3(12), 362–366 (2013), ISSN 2250-2459

“Vedic mathematics”, Swami Sri Bharati Krsna Thirthaji Maharaja, Motilal Banarasidass Indological publishers and Book Sellers, (1965)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Arish, S., Sharma, R.K. Run-Time-Reconfigurable Multi-Precision Floating-Point Matrix Multiplier Intellectual Property Core on FPGA. Circuits Syst Signal Process 36, 998–1026 (2017). https://doi.org/10.1007/s00034-016-0335-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-016-0335-2