Abstract

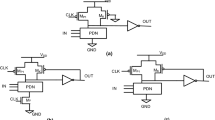

Leakage power consumption is a major technical problem faced in nanometer or deep submicron CMOS circuit technology. A new circuit technique based on “lector stacking” is proposed in this paper for reducing the subthreshold and gate oxide leakage currents in the idle and non-idle modes of operation for domino circuits. In this technique a p-type and an n-type leakage control transistor (LCT) are introduced between the pull-up and pull-down network, and the gate of one is controlled by the source of the other. For any combination of inputs, one of the LCTs will operate near its cut-off region and will increase the resistance between supply voltage and ground, resulting in reduced leakage current. Lector stacking retains the logic state during the idle mode as in the conventional footerless domino logic. Furthermore, the leakage current is suppressed at the output inverter circuit by adding a diode-footed transistor below the n-type transistor of the inverter, offering a more resistive path between supply voltage and ground.The proposed circuit technique for AND2, OR2, OR4, and OR8 circuits reduces the active power consumption by 13.66 % to 44.45 % and by 12 % to 33 % at the low and high die temperatures, respectively, compared to the standard footerless domino logic circuits. During idle mode for the same logic gates, 1.64 % to 79.39 % and 1.2 % to 35.19 % reduction of leakage current is observed with low and high inputs at 25 °C and 110 °C respectively. Similarly, during non-idle mode 0.94 % to 99.3 % and 1.57 % to 98.58 % is observed with low and high inputs at 25 to 110 °C, respectively, when compared to standard footerless domino logic circuits.

Similar content being viewed by others

References

M.W. Allam, M.H. Anis, M.I. Elmasry, High-speed dynamic logic styles for scaled-down CMOS and MTCMOS technologies, in Proc. of the IEEE/ACM International Symposium on Low Power Electronics and Design, (2000), pp. 145–160

Berkeley predictive technology model (BPTM). Univ. California, Berkeley, 2007. Available online: http://www.device.eecs.berkley.edu/ptm/dowmload.html

F. Moradi, A. Peiravi, An improved noise-tolerant domino logic circuit for high fan-in gates, in Proc. IEEE (2005), pp. 116–121

N. Hanchate, N. Ranganathan, LECTOR: a technique for leakage reduction in CMOS circuits. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 12(2), 196–205 (2004)

M.C. Johnson, D. Somasekhar, L.Y. Chiou, K. Roy, Leakage control with efficient use of transistor stacks in single threshold CMOS. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 10, 1–5 (2002)

J. Kao, Dual threshold voltage domino logic, in Proc. of the European Solid-State Circuits Conference (1999), pp. 118–121

J.T. Kao, A.P. Chandrakasan, Dual-threshold voltage techniques for low-power digital circuits. IEEE J. Solid-State Circuits 35(7), 1009–1018 (2000)

V. Kursun, E.G. Friedman, Domino logic with variable threshold voltage keeper. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 11(6), 1080–1093 (2003)

V. Kursun, E.G. Friedman, Sleep switch dual threshold voltage domino logic with reduced standby leakage current. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 12(5), 485–496 (2004)

V. Kursun, E.G. Friedman, Node voltage dependent subthreshold leakage current characteristics of dynamic circuits, in Proc. of the IEEE/ACM International Symposium of Quality Electronic Design (2004), pp. 104–109

Z. Liu, V. Kursun, Leakage power characteristics of dynamic circuits in nanometer CMOS technologies. IEEE Trans. Circuits Syst. II, Express Briefs 53(8), 692–696 (2006)

Z. Liu, V. Kursun, Leakage biased PMOS sleep switch dynamic circuits. IEEE Trans. Circuits Syst. II, Express Briefs 53(10), 1093–1097 (2006)

Z. Liu, V. Kursun, PMOS-only sleep dual-threshold voltage domino logic in sub-65-nm CMOS technology. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 15(12), 1311–1319 (2007)

S. Narendra, S. Borkar, V. De, D. Antoniadis, A.P. Chandrakasan, Scaling of stack effect and its application for leakage reduction, in Proc. IEEE ISLPLED (2001), pp. 195–200

H. Sasaki, M. Ono, T. Ohguro, S. Nakamura, M. Satio, Iwai, 1.5 nm direct-tunneling gate oxide Si MOSFETs’. IEEE Trans. Electron Devices 43(8), 1233–1242 (1996)

S. Shingematsu, S. Mutoh, Y. Matsuya, J. Yamada, A 1 V high-speed MTCMOS circuit scheme for power-down application, in Proc. IEEE International Symposium VLSI Circuits (1995), pp. 125–126

S. Sirichotiyakul, T. Edwards, C. Oh, R. Panda, D. Blaauw, Duet: an accurate leakage estimation and optimization tool for dual-V t circuits. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 10, 79–90 (2002)

J. Wang, N. Gong, L. Hou et al., Low power and high performance dynamic CMOSXOR/XNOR gate design. Microelectron. Eng. 88(8), 2781–2784 (2008)

J. Wang, N. Gong, L. Zuo et al., Performance estimation for dual threshold domino OR and the analysis for its availability under process variation. Chin. J. Electron. 38, 2611–2615 (2010)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Gupta, T.K., Khare, K. Lector with Footed-Diode Inverter: A Technique for Leakage Reduction in Domino Circuits. Circuits Syst Signal Process 32, 2707–2722 (2013). https://doi.org/10.1007/s00034-013-9615-2

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-013-9615-2