Abstract

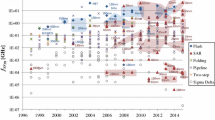

Data converter linearization has been a subject of some interest for most of the past decade. New methods of linearizing analog-to-digital converters (ADCs) continue to be developed. Various linearization methods are available but their comparative strengths and weaknesses are not easily recognizable, making it somewhat difficult to determine which compensator would provide maximum benefit for a specific device. This paper provides a novel performance comparison of two promising real-time linearization methods for flash ADCs: the in-device DEM method, and the peripherally-implemented BEET method using SFDR, SINAD, ENOB, and THD as performance metrics. It is found that BEET is the superior compensator for devices with INL values larger than 0.25 LSB and DNL values larger than 0.25 LSB for optimal SFDR. Results from SINAD, ENOB, and THD metrics indicate that BEET is superior compared to DEM for all devices that have INL>0.05 LSB.

Similar content being viewed by others

References

F. Adamo, F. Attivissimo, N. Giaquinto, A. Trotta, A/D converters nonlinearity measurement and correction by frequency analysis and dither. IEEE Trans. Instrum. Meas. 52(4), 1200–1205 (2003)

M. Alink, A. Kokkeler, E. Klumperink, K. Rovers, G. Smit, B. Nauta, Spurious-free dynamic range of a uniform quantizer. IEEE Trans. Circuits Syst. II, Express Briefs 56(6), 434–438 (2009)

R. Baird, T. Fiez, Linearity enhancement of multibit ΔΣ A/D and D/A converters using data weighted averaging. IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process. 41(12), 753–762 (1995)

E. Balestrieri, P. Daponte, S. Rapuano, A state of the Art on ADC error compensation, methods. IEEE Trans. Instrum. Meas. 54(4), 1388–1394 (2005)

K. El-Sankary, A. Assi, M. Sawan, A new time-interleaved architecture for high-speed A/D converters, in Proceedings of the Third International Workshop on Digital and Computational Video (2002), pp. 93–99

P. Handel, M. Skoglund, A calibration scheme for imperfect quantizers. IEEE Trans. Instrum. Meas. 49, 1063–1068 (2000)

C. Huang, J. Wu, A background comparator calibration technique for flash analog-to-digital converters. IEEE Trans. Circuits Syst. 52(9), 1732–1740 (2005)

IEEE Standard for Terminology and Test Methods for Analog-to-Digital Converters, December (2000)

W. Kester, Mixed-Signal and DSP Design Techniques (Newnes Press, 2003)

H. Lundin, Characterization and correction of analog-to-digital converters. Doctoral Thesis, Royal Inst. Technology (2003)

F. Maloberti, Data Converters (Springer, Berlin, 2008)

E. Sall, K. Andersson, M. Vesterbacka, A dynamic element matching technique for flash analog-to-digital converters, in Proceedings of the 6th Nordic Signal Processing Symposium (2004), pp. 137–140

E. Sall, M. Vesterbacka, 6-bit flash ADC with dynamic element matching, in Proceedings of the 24th Norchip Conference (2006), pp. 159–162

P. Stubberud, J.W. Bruce, An analysis of flash dynamic element matching analog to digital converters, in Proceedings of the 43rd IEEE Midwest Symposium on Circuits and Systems (2000), pp. 684–687

J. Tsimbinos, Identification and compensation of nonlinear distortion. Doctoral Thesis, University of South Australia, Adelai, Australia (1995)

J. Tsimbinos, K.V. Lever, Improved error-table compensation of A/D converters. IEE Proc., Circuits Devices Syst. 144(6), 343–349 (1997)

S. Weaver, B. Hershberg, D. Knierim, U. Moon, Stochastic flash analog-to-digital conversion. IEEE Trans. Circuits Syst. 57(11), 2825–2833 (2010)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

McGuinness, C.D., Balster, E.J. & Scarpino, F.A. Comparison of DEM and BEET Linearization Techniques for Flash Analog-to-Digital Converters. Circuits Syst Signal Process 32, 2639–2652 (2013). https://doi.org/10.1007/s00034-013-9603-6

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-013-9603-6