Abstract

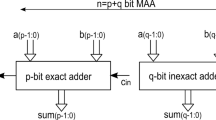

This paper presents a new 8-bit adder circuit, called discrepant low PDP 8-bit adder (DLPA) based on three new full adder cells, which have been designed based on requirements of different positions in each 8-bit adder circuit. In order to design the full adder cells, a new and general method has been proposed aiming to achieve full-swing output and low number of transistors. The proposed adder along with several state-of-the-art adders from the literature have been extensively analyzed and compared together. The results revealed that the power-delay product of DLPA is almost more than 20 % less than that of other compared circuits.

Similar content being viewed by others

References

Z. Abid, H. El-Razouk, D.A. El-Dib, Low power multipliers based on new hybrid full adders. Microelectron. J. 39(12), 1509–1515 (2008)

M. Alioto, G.D. Cataldo, G. Palumbo, Mixed full adder topologies for high-performance low-power arithmetic circuits. Microelectron. J. 38, 130–139 (2007)

H.T. Bui, Y. Wang, Y. Jiang, Design and analysis of low-power 10-transistor full adders using novel XOR–XNOR gates. IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process. 49(1), 25–30 (2002)

C. Chip-Hong, G. Jiangmin, Z. Mingyan, A review of 0.18-μm full adder performances for tree structured arithmetic circuits. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 13(6), 686–695 (2005)

Y. Egami, Theoretical study on electron transport through graphene strip with defects. J. Comput. Theor. Nanosci. 6(2009), 2662–2667 (2009)

V. Foroutan, K. Navi, M. Haghparast, A new low power dynamic full adder cell based on majority function. World Appl. Sci. J. 4(1), 133–141 (2008)

M.H. Ghadiry, M. Nadisenejani, M. Miryahyaei, A new full swing full adder based on a new logic approach. World Appl. Sci. J. 11(7), 808–811 (2010)

M.H. Ghadiry, A.K. A’Ain, M. Nadisenejani, Design and analysis of a novel low PDP full adder cell. J. Circuits Syst. Comput. 20(3), 439–445 (2011)

M.H. Ghadiry, Asrulnizam Abd Manaf, M.T. Ahmadi, H. Sadeghi, M. Nadisenejani, Design and analysis of a new carbon nanotube full adder cell. J. Nanomater. 2011(2011), 906237 (2011)

S.A.K. Goel, M.A. Bayoumi, Design of robust, energy-efficient full adders for deep-submicrometer design using hybrid-CMOS logic style. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 14(12), 1309–1321 (2006)

W. Hang-Sheng, Z. Xinping, P. Li-Shiuan, M. Sharad, Orion: a power-performance simulator for interconnection networks, in ACM/IEEE International Symposium on Microarchitecture (IEEE Press, New York, 2002)

J.-F. Lin, Y.-T. Hwang, M.-H. Sheu, C.-C. Ho, A novel high-speed and energy efficient 10-transistor full adder design. IEEE Trans. Circuits Syst. I, Regul. Pap. 54, 1050–1059 (2007)

M. Nadi, M.H. Ghadiry, M.K. Dermany, The effect of number of virtual channel on NOC EDP. J. Appl. Math. Inform. 2010(1), 539–551 (2010)

V. Navarro-Botello, J.A. Montiel-Nelson, S. Nooshabadi, High performance low power CMOS dynamic logic for arithmetic circuits. Microelectron. J. 38(1), 482–488 (2007)

K. Navi, V. Foroutan, B. Mazloomnejad, S. Bahrololoumi, O. Hashempour, M. Haghparast, A six transistors full adder. World Appl. Sci. J. 4(1), 142–149 (2008)

K. Navi, N. Khanadel, The design of a high-performance full adder cell by combining common digital gates and majority function. Eur. J. Sci. Res. 23, 626–638 (2008)

K. Navi, M.M.V. Foroutan, S. Timarchi, O. Kavei, A novel low power full-adder cell for low voltage. Integration 42(4), 457–467 (2009)

K. Navi, M. Maeen, V. Foroutan, S. Timarchi, O. Kavehei, A novel low-power full-adder cell for low voltage. Integration 42(4), 457–467 (2009)

K. Navi, M.H. Moaiyeri, R.F. Mirzaee, O. Hashemipour, B.M. Nezhad, Two new low-power full adders based on majority-not gates. Microelectron. J. 40(1), 126–130 (2009)

K. Navi, M. Saatchi, O. Daei, A high-speed hybrid full adder. Eur. J. Sci. Res. 26, 29–33 (2009)

R.M.P. Pedram (ed.), Low Power Design Methodologies (Kluwer Academic, Norwell, 1996)

D.A. Pucknell, K. Eshraghian, Basic VLSI Design, 3rd edn. (Prentice-Hall, Englewood Cliffs, 1994)

M.N. Senejani, M.H. Ghadiry, M. Miryahyaei, Low dynamic power high performance full adder, in Proc. of ICFCC (2009), pp. 482–486

R. Shalem, E. John, L.K. John, A novel low-power energy recovery full adder cell, in Proc. Great Lakes Symp. VLSI (1999), pp. 380–383

A.M. Shams, M.A. Bayoumi, A novel high-performance CMOS 1-bit full-adder cell. IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process. 47(5), 478–481 (2000)

A.M. Shams, T.K. Darwish, M.A. Bayoumi, Performance analysis of low-power 1-bit CMOS full adder cells. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 10(1), 20–29 (2002)

A.M. Shams, G.M. Zhang, A review of 0.18 μm full adder performances for tree structure arithmetic circuits. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 13(6), 686–695 (2005)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ghadiry, M., Nadi, M. & A’Ain, A.K. DLPA: Discrepant Low PDP 8-Bit Adder. Circuits Syst Signal Process 32, 1–14 (2013). https://doi.org/10.1007/s00034-012-9438-6

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-012-9438-6