Abstract

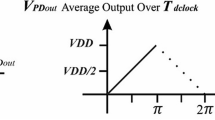

A complementary metal oxide semiconductor (CMOS) phase/frequency detector (PFD) is presented. An improved CMOS D-type master-slave flip-flop is described and adopted in the PFD. Higher speed and lower power operation is attributed to the reduced node capacitance. Charge-sharing phenomena are circumvented in the proposed flip-flop and PFD. The maximum frequency of operation of the PFD is analytically studied. Device-sizing equations, based upon a first-order approximation, for the PFD are derived. The proposed PFD shows improvements in both phase and frequency sensitivities at high operating frequencies. HSPICE simulations of a phase-locked loop (PLL) employing the improved PFD demonstrate a faster frequency acquisition. The PLL simulations also verify that the maximum operating frequency of the PFD is in agreement with our analytical results.

Similar content being viewed by others

Author information

Authors and Affiliations

Corresponding authors

Rights and permissions

About this article

Cite this article

Chen, R., Huang, HY. & Hsieh, MY. Design of an Improved CMOS Phase/Frequency Detector. Circuits Syst Signal Process 25, 539–557 (2006). https://doi.org/10.1007/s00034-005-0819-y

Received:

Issue Date:

DOI: https://doi.org/10.1007/s00034-005-0819-y