Abstract

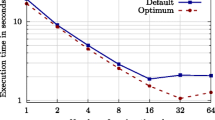

The paper describes a simple compiler analysis method for determining the “weight” of procedures in parallel logic programming languages. Using Flat Guarded Horn Clauses (FGHC) as an example, the analysis algorithm is described. Consideration of weights has been incorporated in the scheduler of a real-parallel FGHC emulator running on the Sequent Symmetry multiprocessor. Alternative demand-distribution methods are discussed, includingoldest-first andheaviest-first distributions. Performance measurements, collected from a group of non-trivial benchmarks on eight processors, show that the new schemes donot perform significantly faster than conventional distribution methods. This result is attributed to a combination of factors overshadowing the benefits of the new method: high system overheads, the low cost of spawning a goal on a shared memory multiprocessor, and the increase in synchronization caused by the new methods. Directions of further research are discussed, indicating where further speedup can be attained.

Similar content being viewed by others

References

Butler, R. et al., “Scheduling OR-Parallelism: an Argonne Perspective,” inFifth International Conference and Symposium on Logic Programming, University of Washington, MIT Press, pp. 1565–1577, August, 1988.

Calderwood, A. and Szeredi, P., “Scheduling Or-Parallelism in Aurora,” inSixth International Conference on Logic Programming, Lisbon, MIT Press, pp. 419–435 June, 1989.

Debray, S. K., “A Remark on Tick’s Algorithm for Compile-Time Granularity Analysis,”Logic Programming Newsletter,Vol. 3, No. 1, August, 1989.

Goto, A., “Parallel Inference Machine Research in FGCS Project,” inFirst Japan-U. S. AI Symposium, pp. 21–36, December, 1987.

Hermenegildo, M. V., “Relating Goal Scheduling, Precedence, and Memory Management in AND-Parallel Execution of Logic Programs,” inFourth International Conference on Logic Programming, University of Melbourne, MIT Press, pp. 556–575, May, 1987.

Ichiyoshi, N.,Personal communication, April, 1988.

Kimura, Y. and Chikayama, T., “An Abstract KL1 Machine and its Instruction Set,” inInternational Symposium on Logic Programming, San Francisco, IEEE Computer Society, pp. 468–477, August, 1987.

Lusk, E. et al., “The Aurora Or-Parallel Prolog System,” inInternational Conference on Fifth Generation Computer Systems, Tokyo, pp. 819–830, November, 1988.

Okumura, A. and Matsumoto, Y., “Parallel Programming with Lavered Streams,” inInternational Symposium on Logic Programming, San Francisco, IEEE Computer Society, pp. 224–233, August, 1987.

Sato, M. et al., “KL1 Execution Model for PIM Cluster with Shared Memory,” inFourth International Conference on Logic Programming, University of Melbourne, MIT Press, pp. 338–355, May, 1987.

Sato, M. and Goto, A., “Evaluation of the KL1 Parallel System on a Shared Memory Multiprocessor,” inIFIP Working Conference on Parallel Processing, Pisa, North Holland, pp. 305–318 May, 1988.

Sugie, M. et al., “Load-Dispatching Strategies on Parallel Inference Machines,” inInternational Conference on Fifth Generation Computer Systems, Tokyo, pp. 987–993, November, 1988.

Taki, K., “Measurements and Evaluation for the Multi-PSI/V1 System,” inFrance-Japan Artificial Intelligence and Computer Science Symposium, Cannes, pp. 359–384, November, 1987.

Tick, E., “Performance of Parallel Logic Programming Architectures,”ICOT Technical Report, TR-421, Tokyo, Japan, September, 1988.

Ueda, K., “Guarded Horn Clauses,”Ph.D. Thesis, University of Tokyo, March, 1986.

Ueda, K., “Making Exhaustive Search Programs Deterministic: Prat II,” inFourth International Conference on Logic Programming, University of Melbourne, MIT Press, pp. 356–375, May, 1987.

Warren, D. H. D., “The SRI Model for OR-Parallel Execution of Prolog—Abstract Design and Implementation,” inInternational Symposium on Logic Programming, San Francisco, IEEE Computer Society, pp. 92–102, August, 1987.

Debray, S. K., Lin, N. and Hermenegildo, M. V., “Task Granularity Analysis in Logic Programs,”SIGPLAN-90 Conference on Programming Language Design and Implementation, submitted for publication.

Author information

Authors and Affiliations

About this article

Cite this article

Tick, E. Compile-time granularity analysis for parallel logic programming languages. NGCO 7, 325–337 (1990). https://doi.org/10.1007/BF03037210

Received:

Issue Date:

DOI: https://doi.org/10.1007/BF03037210