Abstract

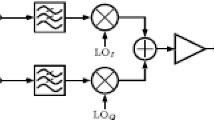

An ideal radio communication receiver places the analog to digital conversion just after the antenna. It is an objective in a “software radio” perspective. The available silicon technologies do not provide the performance required by this application. We are able to evaluate the present limits and the gap between these limits and the ideal solution proposed. In this paper, we describe the present possibilities in terms of receiver architectures and we deduce theAdc specifications. Then we analyse differentAdc architectures adapted to this application. The choice is mainly between pipeline and sigma- deltaAdc. We compare them in terms of power consumption and we introduce a factor of merit. The future technologies will have an impact onAdc performance. Superconductor technology applied toAdc may be a solution and it is analysed at the end of this paper.

Résumé

Pour la radio logicielle, la place idéale de la conversion analogique numérique est située juste après l’antenne de réception. Les technologies silicium disponibles ne permettent pas d’atteindre les performances imposées par une telle application. Nous pouvons évaluer les limites actuelles et avoir une idée du chemin qu’il reste à parcourir pour atteindre cette solution idéale. Dans cet article, nous présentons les possibilités offertes aujourd’hui par les architectures de récepteur et nous déduisons les spécifications duCan. Puis les diffé -rentes architectures de convertisseur adaptées à cette application sont analysées. Le choix doit se faire principalement entre les convertisseurs pipeline et sigma- delta. II est intéressant de les comparer en terme de puissance consommée. Connaître l’impact des technologies futures sur les performances de convertisseurs permet de montrer leur évolution dans les années à venir. La technologie des supraconducteurs appliquée à la conversion sera peut- être une solution et est envisagée à la fin de cet article.

Similar content being viewed by others

References

Mitola (J.), “The software radio architecture”,Ieee Communications Magazine, vol.33, no.5, pp. 26–38, May 1995.

Mitola (J.),“Technical challenges in the globalization of software radio”,Ieee Communications Magazine,37, n° 2, pp. 84–89, Feb. 1999.

Tuttlebee (W.H.W.), “Software radio technology: A European perspective”,Ieee Communications Magazine,37, n° 2, pp. 118–123, Feb. 1999.

Wepman (J.A.), “Analog-to-Digital converters and Their Applications in Radio Receivers”,Ieee Communications Magazine,33, n° 5, pp. 39–45, May 1995.

Shinagawa (M.), Akazawa (Y.), Wakimoto (T.), “Jitter Analysis of High-Speed Sampling Systems”,Ieee J. of Solid-State Circuits,25, n° 1, pp. 220–4, Feb. 1990.

Laker (K.R.), Sansen (W.), “Design of Analog Integrated Circuits and Systems”, McGraw-Hill, Inc. 1994.

Van De Plassche (R.J.), “Integrated Analog-to-Digital and Digital-to-Analog Converters”,Kluwer Academic Publishers, Boston, MA, USA, 1994.

Walden (R.H.), “Analog-to Digital Converter Survey and Analysis”,Ieee Journal on Selected Areas in Communications,17, n° 4, pp. 539–550, Apr. 1999.

Stetzler (T.),et al. “A 2.7 V to 4.5 V Single-ChipGsm Transceiver RF Integrated Circuit”, Digest of Technical Papers,International Solid-State Circuits Conference, pp. 150–151, February 1995.

Mirabbasi (S.), Martin (K.) “Classical and Modern Receiver Architectures”,Ieee Communications Magazine, pp. 132–139, November 2000.

Sato (H.),et al. “A 1.9Ghz Single-Chip IF Transceiver for Digital Cordless Phones”, Digest of Technical Papers,International Solid-State Circuits Conference, pp. 342–343, February 1996.

Irie (K.) et al. “A 2.7 VGsm rf TransceiverIc,” 1997Ieee International Solid-State Circuits Conference, Digest of Technical Papers, pp. 302–303, February 1997.

Weigandt (T.), “Low-Phase-Noise Low-Timing-Jitter Design Techniques for Delay Cell Based vcos and Frequency Synthesizers,” Ph.D. Thesis, Electronics Research Laboratory, University of California at Berkeley, December 1997.

Hull (C.) et al. “A Direct-Conversion Receiver for 900Mhz (ISM Band) Spread-Spectrum Digital Cordless Telephone,”Digest of Technical Papers,International Solid-State Circuits Conference, pp. 344–345, February 1996.

Crols (J.), Steyaert (M.),“A Single-Chip 900Mhz Cmos Receiver Front-End with a High Performance Low- IF Topology,”,Ieee Journal of Solid-State Circuits,30, n° 12, pp. 1483–1492, December 1995.

Rudell (J.),et al. “A 1.9Ghz Wide Band IF Double ConversionCmos Integrated Receiver for Cordless Telephone Applications,”,Ieee Journal of Solid-State Circuits,32, n° 12, pp. 2071–2088, December 1997.

Naviner (L.), Loumeau (P.), “A Method to Specify SD Converters in Radio Receivers”, Proceedings Mixed Design of Integrated Circuits and Systems, June 2001.

ETSI, UMTS, “ue Radio Transmission and Reception (Fdd )”, ETSI TS 125.101 version 3.5.0, Dec. 2000.

Manaï (B.), Loumeau (P.), “ACmos Switched Capacitor Channel Select Filter For Direct Conversion UMTS Receiver”,Ieee International Conference on Electronics, Circuits and Systems, pp. 1541–1544, September 2001.

Colin (E.), Loumeau (P.), Naviner (L.), Naviner (J.-E), “Antialiasing Filtering Influences onAdc Specifications for Radio Receivers”,Ieee International Conference on Electronics, Circuits and Systems, pp. 1469–1472, September 2001.

Lewis (S.H.), Gray (P.R.), “A Pipelined 5-Msample/s 9-bit Analog-to-Digital Converter”,Ieee Journal of Solid-State Circuits,22, n°6, pp. 954–961, Dec. 1987.

Ginetti (B.), Jespers (P.G.A.), Vandemeulebroecke (A.),“ACmos 13-b Cyclic RSD a/d Converter”,Ieee Journal of Solid-State Circuits, vol. 27, n° 7, pp. 957–964, July 1992.

Lewis (S.H.), Scott Fetterman (H.), Gross(G.F.), Ramachandran (R.), Viswanathan (T.R.), “A 10-b 20- Msample/s Analog-to-Digital Converter”,Ieee Journal of Solid-State Circuits,27,n° 3, March 1992.

Lewis (S.H.), “Optimizing the Stage Resolution in Pipelined, Multistage, Analog-to-Digital Converters for Video-rate Applications”,Ieee Transactions on Circuits and Systems-II,39, n° 8, pp.516–523, August 1992.

Goes (J.), Franca (J.), Paulino (N.), Grilo (J.), Temes (G.), “High-Linearity Calibration of Low-Resolution Digital-to-Analog Converters”,Ieee Int. Symposium on Circuits and Systems, pp.345–348, 1994.

Lee (S.H.), Song (B.S.),“Digital-Domain Calibration of Multistep Analog-to-Digital Converters”,Ieee Journal of Solid-State Circuits,27, n° 12, pp.1679–1688, Dec.1992.

Ming (J.), Lewis (S.H.), “An 8b 80MSample/s pipelinedAdc with background calibration”Ieee International Solid-State Circuits Conference, Digest of Technical Papers, pp. 42–43, 446, February 2000.

Soenen (E.G.), Geiger (R.), “An Architecture and An Algorithm for Fully Digital Correction of Monolithic PipelinedAdc’s”,Ieee Transactions On Circuits and Systems-II,42, no.3, pp.143–153, March 1995.

Gustavsson (M.), Wikner (J.J.), Tan (N.N.), “Cmos Data Converters for Communications”,Kluwer Academic Publishers, ISBN 0-7923-7780-X, 2000.

Goes (J.), Vital (J.C.), Franca (J.E.), “Systematic Design for Optimization of High-Speed Self-Calibrated Pipelined A/D Converters”,Ieee Transactions On Circuits and Systems-II,45, n° 12, pp. 1513–1526, Dec. 1998.

Norsworthy (S.R.), Schreier (R.), Temes (G.C.), “Delta-Sigma Data Converters - Theory, Design, and Simulation”,Ieee Press, ISBN 0-7803-1045-4, 1997.

Braz (F.T.), “Conversion analogique numérique de type SD pour applications en radiocommunications”, Ph.D Thesis (in French), January 2000.

Sarhang-Nejad (M.), Temes (G.C.): “A high-Resolution SDAdc with Digital Correction and Relaxed Amplifiers Requirements”,Ieee Journal of Solid-State Circuits,28, pp. 648–660, June 1993.

Baird (R.T.), Fiez (T.S.), “A Low Oversampling Ratio 14-b 500-kHz sdAdc with a Self-Calibrated Multibit DAC”,Ieee Journal of Solid-State Circuits,31, pp. 312–320, March 1996.

Kiaei (S.) et al., “Adaptative Digital Correction for Dual-Quantization SD Modulators”,Ieee Int. Symposium on Circuits and Systems, pp. 1228–1230, May 1993.

Aziz (P.M.), Sorensen (H.V.), Van Der Spiegel (J.), “An Overview of Sigma-Delta Converters”,Ieee Signal Processing Magazine, pp. 61–84, January 1996.

Cherry (J.A.), Snelgrove (W.M.), “Continuous-Time Delta-Sigma Modulators for High-Speed A/D Conversion - Theory, Practice and Fundamental Performance Limits”,Kluwer Academic Publishers, ISBN 0- 7923-8625-6, 2000.

Crochiere (R.E.), Rabiner (L.R.), “Multirate Digital Signal Processing”,Prentice-Hall, 1983.

Chu (S.), Sidney Burrus (C), “Multirate filter designs using comb filters”,Ieee Trans. Circuits and Systems, CAS-31, pp. 913–924, Nov. 1984.

Gao (Y.), Jia (L.), Isoaho (J.), Tenhunen (H.), “A comparison design of comb decimators for sigma-delta analog-to-digital converters,”InternationalJournal: Analog Integrated Circuits and Signal Processing, pp. 51–60, 1999.

Gao (Y.) Tenhunen (H.), “A fifth-order comb decimation filter for multi-standard transceiver applications”,Ieee Int. Symposium on Circuits and Systems, May 28–31, 2000, Geneva, Switzerland.

Hogenauer (E.), “An economical class of digital filters for decimation and interpolation”,Ieee Trans, on Acoustics, Speech, and Signal Processing, April 1981.

Lawson (S.S.), “On Design Techniques for Approximately Linear Phase Recursive Digital Filters”,Ieee Int. Symposium on Circuits and Systems, Hong Kong, June 1997.

Krukowski (A.), Kale (I.) “Almost Linear-Phase Polyphase iir Lowpass/highpass Filter Approach”,International Symposium on Signal Processing and its Applications (ISSPA’99), Brisbane Australia, August 1999.

Gratti (K.), Ghazel (A.), Naviner (L.), Tabbane (S.), “Comparison of fir and iir Structures for Decimation Filtering in Radio Communications”,Proc. of the 5th Multi-Conf. on Systemics, Cyb. and Informatics,SCI’2001, Orlando, USA, July, 2001.

Barret (C.), “Low Power Decimation Filter Design for Multi-Standard Transceiver Applications”, MSC. Thesis, University of California, Berkeley, 1995.

Lampinen (H.), Vainio (O.), “Design and implementation of application specific sigma-delta converters”,Ieee Int. Symposium on Circuits and Systems, Switzerland, May 2000.

Naviner (L.), Naviner (J.-F), “On efficient cascade implementation of narrow band decimator filter for sigma delta modulators”,Proceedings of the Ieee Midwest Symposium on Circuits and Systems, MWSCAS2000, Lansing, MI, USA, Aug. 2000.

Brandt (B.P.), Wooley (B.A.), “A low-power, area-efficient digital filter for decimation and interpolation”,Ieee Journal of Solid-State Circuits,29, pp. 679–687, 1994.

Seo (D.), Shanbhag (N.R.), Feng (M.), “Low-power decimation filters for oversamplingAdcs via the decor- relating (decor) transform”,Ieee Int. Symposium on Circuits and Systems, May 28–31, 2000, Geneva, Switzerland.

Chen (H.S.), Bacrania (K.), Song (B-S), “A 14 b 20 MSample/sCmos pipelinedAdc”,Ieee International Solid-State Circuits Conference, Digest of Technical Papers, pp. 46–47, February 2000.

Waltari (M.), Halonen (K.A.I.), “1-V 9-Bit Pipelined Switched-OpampAdc”,Ieee Journal of Solid-State Circuits,36, n° n1, January 2001.

Mehr (I.), Singer (L.), “A 55-mW, 10-bit, 40-Msample/s Nyquist-RateCmos Adc”,Ieee Journal of Solid-State Circuits,35, n° 3, March 2000.

Park (Y-I), Karthikeyan (S.), Tsay (F.), Bartolome (E.), “A 10 b 100 MSample/sCmos pipelinedAdc with 1.8 V power supply”,Ieee International Solid-State Circuits Conference, Digest of Technical Papers, pp. pp130–131, 439, February 2001.

Lauwers (E.), Gielen (G.), “A power estimation model for high-speedCmos a/d converters”,Design,Automation and Test in Europe Conference and Exhibition Proceedings, 1999, pp. 401–405.

Vleugels (K.), Rabii (S.), Wooley (B.A.), “A 2.5 V broadband multi-bit Sigma Delta modulator with 95 dB dynamic range”,Ieee International Solid-State Circuits Conference, Digest of Technical Papers, pp. 50–51, 428, February 2001.

Geerts (Y), Steyaert (M.), Sansen (W.), “A 12-bit 12.5 MS/s multi-bit Delta SigmaCmos adc”,Proceedings of the Ieee Custom Integrated Circuits Conference, pp.21–24, 2000.

Brooks (T.L.), Robertson (D.H.), Kelly (D.F.), Del Muro (A.), Hartson (S.W.), “A Cascaded Sigma-Delta Pipeline A/D Converter with 1.25Mhz Signal Bandwidth and 89 dB snr”,Ieee Journal of Solid-State Circuits,32, n° 12, pp. 1896–1906, Dec. 1997.

Steyaert (M.) et al., “Custom Analog Low Power Design: The problem of low-voltage and mismatch”, inProceedings Ieee-Custom Int. Cire. Conf., CICC97, pp. 285–292, 1997.

Bult (K.), “Analog design in deep sub-micron CMOS”, inProceedings European Solid-State Circuits Conference, pp. 11–17, Sept. 2000.

Kinget (P.), Steyaert (M.), “Impact of transistor mismatch on the speed-accuracy-power trade-off of analogCmos circuits”, inProceedings Custom Integrated Circuits Conference, pp. 333–336, May 1996.

Pelgrom (M.J.M.), Duinmaijer (A.C.J.), Welbers (A.P.G.), “Matching properties of mos transistors”, inIeee Journal of Solid-State Circuits, SC-24, n° 3, pp. 1433–1439, Oct. 1989.

Uyttenhove (K.), Steyaert (M.), “Design of High-Speed Analog-to-Digital Interface in Digital technologies”, inIeee International Conference on Electronics, Circuits, pp. 493–496, Sept. 2001.

Ohguro (T.) et al., “0.18 mm low voltage / low power rfCmos with zero Vth analog mosfet’s made by undo- ped epitaxial channel technique”,Ieee iedm Tech. Dig., pp. 837–840, 1997.

Sansen (W.), Steyaert (M.), Peluso (V.), Peeters (E.), “Toward Sub IV Analog Integrated Circuits in Submicron StandardCmos Technologies”, inIeee International Solid-State Circuits Conference, pp. 186–187 and 435, 1998.

Crols (J.), Steyaert (M), “Switched-OpAmp: An Approach to Realize FullCmos Switched-Capacitor Circuits at Very Low Power Supply Voltages”,Ieee J. Of Solid-State Circ,29, n° 12, pp. 936–942, Aug. 1994.

Peluso (V.) et al, “A 900-mV Low-Power SD A/D Converter with 77-dB Dynamic Range”,Ieee J. of Solid- State Circ,33, no 12, pp. 1887–1897, Dec. 1998.

Bult (K.), Buchwald (A.), “An embedded 240-mW 10-bit 50-MS/sCmos Adc in 1 mm2”,Ieee J. of Solid- State Circ, 32, n° 12, pp. 1887–1895, Dec. 1997.

Ali (A.A.), Nagaraj (K.), “Correction of operational amplifier gain error in pipelined a/d converters”, inIeee International Symposium on Circuits and Systems, May 2001.

Frank (D.J.) et al., “Device Scaling Limits of Si mosfets and Their Application Dependencies”,in Proceeding of the Ieee Special Issue on The Limits of Semiconductor Technology, pp. 259–288, March 2001.

http://www.hypres.com

Mukhanov (O.A.); Semenov (V.K.), Li (W.), Filippov (T.V.), Gupta (D.), Kadin (A.M.), Brock (D.K.), Kirichenko (A.F.), Polyakov (Y.A.), Vernik (I.V.), “A superconductor high-resolution.Adc”,Ieee Transactions on Applied Superconductivity, 11 Issue: 1 Part: 1, pp. 601–606, March 2001.

Fujimaki (A.), Nakazono (K.), Hasegawa (H.), Sato (T.), Akahori (A.), Takeuchi (N.), Furuta (E), Katayama (M.), Hayakawa (H.), “Broad Band Software-Defined Radio Receivers Based on Superconductive Devices”,Ieee Transaction on applied superconductivity,11, no 1, March 2001.

Alan Kadin (M.), Cesar Mancini (A.), Marc Feldman (J.), Darren Brock (K.), “Can rsfq logic circuits be scaled to deep submicron junctions ?”Applied Superconductivity,Ieee Transactions on applied superconduc- tivity,11 Issue: 1 Part: 1, pp.1050–1055, March 2001,

Cline (D.W.), Gray (P.R.), “A Power Optimized 13-bit 5 Msamples/s Pipelined Analog to Digital Converter in 1.2 μmCmos”,Ieee Custom Integrated Circuits Conference, pp. 219–222, May 1995.

Medeiro (F), Pérez-VerdÜ (A.), Rodriguez-Vazquez (A.), “Top-down design of high-performance sigma- delta modulators”,Kluwer Academic Publishers, 1999.

Bright (W.), “8b 75MSample/s 70mW Parallel PipelinedAdc Incorporating Double Sampling”,Solid-State Circuits Conference, Feb. 1998.

Sumanen (L.), Waltari (M.), Halonen (K.), “A pipeline a/d converter for wcdma applications”,Proceedings of International Conference on Electronics, Circuits and Systems, 1999.

Abo (A.M.), Gray (P.R.), “A 1.5 V, 10-bit, 14.3-ms/sCmos Pipeline Analog-to-Digital Converter”,kee jour- nal of solid-state circuits,34, n° 5, 1999.

Choi (H.C.), Park (H.J.), Bae (S-K), Kim (J-W), “A 1.4 V 10-bit 20 Msps pipelined A/D converter”,International Symposium on Circuits and Systems, 2000.

Nairn (D.G.), “A 10-bit, 3 V, 100ms/s pipelinedAdc”,Ieee Custom Integrated Circuits Conference, May 21–24, 2000.

Hamedi_Hagh (S.), Salama (C.A.T.), “A 10-bit, 50 Msample/s, low power pipelined A/D converter for cable modem application”,Ieee International Symposium on Circuits and Systems, May 6–9, 2001.

Pan (H.) et al, “A 3.3V, 12b, 50Msample/s A/D converter in 0.6 mmCmos with over 80dBSfdr”,Ieee International Solid-State Circuits Conference, 2000.

Singer (L.) et al, “A 12b 65Msample/sCmos Adc with 82dBSfdr at 120Mhz”,Ieee International Solid-State Circuits Conference, 2000.

Jeon (Y-D) et al, “A 12b 50Mhz 3.3VCmos acquisition time minimized A/D converter”,Asia South Pasific Design Automation Conference, 2000.

Ingijo (J.M.), Wooley (B.A.), “A Continuously Calibrated 12-b, 10-MS/s, 3.3-V A/D Converter”,Ieee journal of solid-state circuits,33, no 12, december 1998.

Choe (M-J), “A 13b 40Msample/sCmos pipelined foldingAdc with background offset trimming”,Ieee International Solid-State Circuits Conference, 2000.

You (S-B) et al, “A 3.3V 14-bit lOMsps calibration-freeCmos pipelined a/d converter”,Ieee International Symposium on Circuits and Systems, May 28-May 31, 2000.

Guilherme (J.) et al, “A pipeline 15-b 10-Msample/s Analog-to-digital converter for adsl applications”,Ieee International Symposium on Circuits and Systems, 2001.

Feldman (A.R.) et al, “A 13-Bit, 1.4-ms/s sigma-delta modulator for rf baseband channel applications”,Ieee journal of solid-state circuits,33, no 10, 1998.

Morizio (J.C.) et al, “14-bit 2.2-MS/s Sigma-DeltaAdcs”,Ieee journal of solid-state circuits,33, no 7, July 2000.

Marques (A.) et al, “A 15-b Resolution 2-Mhz Nyquist Rate Sigma DeltaAdc in a 1 umCmos Technology”,Ieee journal of solid-state circuits,33, no 7, July 1998.

Geerts (Y.) et al, “A 3.3-V, 15-bit, delta-sigmaAdc with a signal bandwidth of 1.1Mhz for adsl applications”,Ieee journal of solid-state circuits,34, n° 7, July 1999.

Fujimori (I.) et al, “A 90 dB snr, 2.5Mhz output rateAdc using cascaded multibit delta-sigma modulation at 8x oversampling ratio”,Ieee International Solid-State Circuits Conference, 2000.

Author information

Authors and Affiliations

Corresponding authors

Rights and permissions

About this article

Cite this article

Loumeau, P., Naviner, JF., Petit, H. et al. Analog to digital conversion: technical aspects. Ann. Télécommun. 57, 338–385 (2002). https://doi.org/10.1007/BF02995168

Received:

Accepted:

Issue Date:

DOI: https://doi.org/10.1007/BF02995168

Key words

- AD converter

- Technical aspect

- Radiocommunication

- Receiver

- Software radio

- System architecture

- Pipeline architecture

- Sigma delta modulation

- Energy consumption

- Submission process

- Superconductor device