Abstract

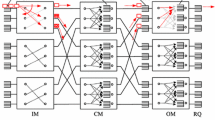

A multicast replication algorithm is proposed for shared memory switches. It uses a dedicated FIFO to multicast by replicating cells at receiver and the FIFO is operating with shared memory in parallel. Speedup is used to promote loss and delay performance. A new queueing analytical model is developed based on a sub-timeslot approach. The system performance in terms of cell loss and delay is analyzed and verified by simulation.

Similar content being viewed by others

References

F. M. Chiussi, Y. Xia, V. P. Kumar, Performance of shared-memory switches under multicast bursty traffic, IEEE Journal on Selected Areas in Communications, 15(1997)3, 473–487.

S. Kumar, D. P. Agrawal, On multicast support for shared-memory-based ATM switch architecture, IEEE Network, 10(1996)1, 34–39.

J. A. Schormans, C. I. Phillips, R. Smith, L. G. Cuthbert, Analysis of a finite shared buffer, Electronics Letters, 30(1994)1, 8–9.

M. Saleh, M. Atiquzzaman, An accurate performance model of shared buffer ATM switches under hot spot traffic, Computer Communications, 22(1999)6, 516–522.

M. Saleh, M. Atiquzzaman, Accurate modeling of the queueing behavior of shared buffer ATM switches, International Journal of Communication Systems, 12(1999)4, 297–308.

S. H. Kang, C. Oh, D. K. Sung, Performance evaluation of a high-speed ATM switch with multiple common memories, IEEE Trans. on Commun., 50(2002)2, 332–340.

H. Bruneel, B. G. Kim, Discrete-time Models for Communication Systems Including ATM, Boston, Kluwer Academic Publishers, 1993.

N. K. Sharma, Review of recent shared memory based ATM switches, Computer Communications, 22(1999)4, 297–316.

H. Akimaru, K. Kawashima, Teletraffic: Theory and Applications, New York, Springer Publishers, 1999.

Author information

Authors and Affiliations

About this article

Cite this article

Wang, W., Ge, N. & Feng, C. Performance analysis of multicast replication mechanism in shared-memory switch with speedup. J. of Electron.(China) 21, 198–205 (2004). https://doi.org/10.1007/BF02687872

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF02687872