Abstract

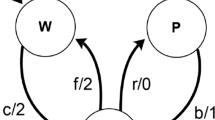

This paper presents the techniques of verification and Test Generation(TG) for sequential machines (Finite State Machines, FSMs) based on state traversing of State Transition Graph(STG). The problems of traversing, redundancy and transition fault model are identified. In order to achieve high fault coverage collapsing testing is proposed. Further, the heuristic knowledge for speeding up verification and TG are described.

Similar content being viewed by others

References

H. Cho, G. D. Hachtel, F. Somenzi, “Fast Sequential ATPG Based on Implicit State Enumeration”, ITC, 1991, 67–74.

H. Cho, G. Hachtel, S. W. Jeong, B. Pessier, “ATPG Aspect of FSM Verification”, ICCAD, 1990, 134–137.

O. Coudert, C. Berthet, J. C. Madre, “Verification of Sequential Machines Using Boolean Functional Vector”, L. J. M. Clasen Editor, Published in Formal VLSI Correctness Verification, 1991, 179–196.

Author information

Authors and Affiliations

Additional information

Supported by the National Natural Science Foundation of China(No.69576038)

About this article

Cite this article

Xinhua, H., Yunzhan, G. & Daozheng, W. STG-based verification and test generation. J. of Electron.(China) 13, 68–73 (1996). https://doi.org/10.1007/BF02684717

Issue Date:

DOI: https://doi.org/10.1007/BF02684717