Abstract

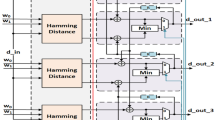

During the last years decoding algorithms that make not only use of soft quantized inputs but also deliver soft decision outputs have attracted considerable attention because additional coding gains are obtainable in concatenated systems. A prominent member of this class of algorithms is the Soft-Output Viterbi Algorithm. In this paper two architectures for high speed VLSI implementations of the Soft-Output Viterbi-Algorithm are proposed and area estimates are given for both architectures. The well known trade-off between computational complexity and storage requirements is played to obtain new VLSI architectures with increased implementation efficiency. Area savings of up to 40% in comparison to straightforward solutions are reported.

Similar content being viewed by others

References

A.J. Viterbi, “Wireless digital communication: A view based on three lessons learned,”IEEE Communications Magazine, pp. 33–36, September 1991.

C.E. Shannon, “A Mathematical Theory of Communication,”Bell System Technical Journal, 27:379–423 and 623–656, June and October 1948.

G.D. Forney, “The Viterbi Algorithm,”Proceedings of the IEEE, 61:268–278, 1973.

J. Hagenauer and P. Höher, “A Viterbi Algorithm with Soft Outputs and It's Application,”Proceedings of the IEEE Global Telecommunications Conference GLOBECOM, pp. 47.1.1–47.1.7, Nov. 1989.

J. Hagenauer and P. Höher, “Verfahren zur Verallgemeinerung des Viterbi Algorithmus, Feb. 1989,” German Pat. pend., no. P 39 10 739.6-31, subm.

J. Huber and A. Rüppel, “Zuverlässigkeitsschätzung für die Ausgangssymbole von Trellis-Decodern,”Archiv für Elektronik und Übertragung (AEÜ), 44:8–21, Jan. 1990. in German.

J. Hagenauer and P. Höher, “Concatenated Viterbidecoding,”Fourth Swedish-Soviet International Workshop on Information Theory, pp. 29–33, Gotland, Sweden, Aug. 1989, Lund: Studentenliteratur.

P. Höher, “TCM on Frequency-Selective Fading Channels: a Comparison of Soft-Output Probabilistic Equalizers,”Proceedings of the IEEE Global Telecommunications Conference GLOBECOM, pp. 401.4.1–401.4.6, 1990.

W. Koch and A. Baier, “Optimum and Sub-Optimum Detection of Coded Data Disturbed by Time-Varying ISI,”Proceedings of the IEEE Global Telecommunications Conference GLOBECOM, pp. 807.5.1–807.5.6, Dec. 1990.

C.M. Rader, “Memory Management in a Viterbi Decoder,”IEEE Transactions on Communications, COM-29: 1399–1401, 1981.

D.J. Coggins, D.J. Skellern, R.A. Keaney, and J.J. Nicolas, “A Comparison of Path Memory Techniques for VLSI Viterbi Decoders,” in G. Musgrave and U. Laughter, editors,VLSI 89, pp. 379–388, IFIP, Elsevier Science Publishers B.V. (North-Holland), 1990.

O.J. Joeressen, M. Vaupel, and H. Meyr, “Soft-Output Viterbi Decoding: VLSI Implementation Issues,”Proceedings of the IEEE International Conference on Vehicular Technology, pp. 941–944, Secaucus, NJ, May 1993. IEEE.

G. Fettweis and H. Meyr, “Parallel Viterbi decoding: Algorithm and VLSI architecture,”IEEE Communications Magazine, 29(5):46–55, May 1991.

G.C. Clark and J.B. Cain,Error-Correction Coding for Digital Communications, New York: Plenum, 1981.

R. Cypher and C.B. Shung, “Generalized Trace Back Techniques for Survivor Memory Management in the Viterbi Algorithm,”Proceedings of the IEEE Global Telecommunications Conference GLOBECOM, pp. 707A.1.1–707A.1.5, San Diego, California, Dec. 1990. IEEE.

E. Paaske, S. Pedersen and J. Sparsø, “An area-efficient path memory structure for VLSI implementation of high speed Viterbi decoders,”INTEGRATION, the VLSI Journal, 12:79–91, 1991.

F Hemmati and D.J. Costello, “Truncation Error Probability in Viterbi Decoding,”IEEE Transactions on Communications, COM-25, pp. 530–532, 1977.

I.M. Onyszchuk, “Truncation Length for Viterbi Decoding,”IEEE Transactions on Communications, 39:1023–1026, 1991.

J. Hagenauer and P. Höher, “Private communication,” spring 1992.

O.J. Joeressen, M. Vaupel, and H. Meyr, “VLSI Architectures for Soft-Output Viterbi Decoding,”Proceedings of the Int. Conf. on Application Specific Array Processors, pp. 373–384, Oakland, August 1992. IEEE Computer Society Press.

Keshab K. Parhi, “Pipeline interleaving and parallelism in recursive digital filters—parts 1 & 2,”IEEE Transactions on Acoustics, Speech and Signal Processing, 37:1099–1134, 1989.

P. Zepter and K. ten Hagen, “Using VHDL with stream driven simulators for digital signal processing applications,”EURO-VHDL'91 Proceedings, pp. 196–203, Stockholm, Sweden, September 8–11 1991.

Glenn E. Dukes,dc-shell Scripts for Synthesis, in S. Carlson, editor,Synopsys Methodology Notes, pp. 411–477. Synopsys Inc., August 1992.

T. Ishitani, K. Tansho, N. Miyahara, S. Kubota, and S. Kato, “A Scarce-State-Transition Viterbi-Decoder VLSI for Bit Error Correction,”IEEE Journal of Solid-State Circuits, SC-22:575–581, 1987.

J. Sparsø, S. Pedersen, and E. Paaske, “Design of a fully parallel Viterbi decoder,” In A. Halaas and P. B. Denyer, editors,VLSI91, Proceedings of the IFIP TC10/WG10.5 International Conference on Very Large Scale Integration, Edinburgh, Scotland, pp. 2.2.1–2.2.10. Elsevier, August 1991.

Author information

Authors and Affiliations

Additional information

This work was supported by the Deutsche Forschungsgemeinschaft (DFG) under contract Me 651/12-1.

Rights and permissions

About this article

Cite this article

Joeressen, O.J., Vaupel, M. & Meyr, H. High-speed VLSI architectures for soft-output viterbi decoding. Journal of VLSI Signal Processing 8, 169–181 (1994). https://doi.org/10.1007/BF02109383

Received:

Published:

Issue Date:

DOI: https://doi.org/10.1007/BF02109383