Abstract

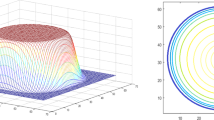

A systematic method for the mapping of digital filter algorithms onto systolic hardware is presented. The method is based on thez-domain characterization of the required filter. It yields filter structures that are modular, pipelined, and hierarchical, and can be used to obtain multidimensional structures. All the structures discussed have a latency of one sampling period and some have maximum concurrency. The paper also deals with the problems of line and frame wrap-around that are inherent in raster-scanned images and ways are suggested for their elimination.

Similar content being viewed by others

References

A. Antoniou,Digital Filters: Analysis and Design, McGraw-Hill: New York, p. 88, 1979.

D.E. Dudgeon and R.M. Mersereau,Multidimensional Digital Signal Processing, Prentice Hall: Englewood Cliffs, New Jersey, 1984.

C. Eswaran, T. Venkateswarlu, and A. Antoniou, “Realization of multidimensional GIC digital filters,”IEEE Trans. Circuits Syst., vol. CAS-37, pp. 685–694, June 1990.

R. Gnanasekaran, “2-D filter implementations for real-time signal processing,”IEEE Trans. Circuits Syst., vol. CAS-35, pp. 587–590, May 1988.

H.T. Kung and W.T. Lin, “An algebra for VLSI algorithm design,”Proc. Conf. Elliptic Problem Solvers, Monterey, CA, 1983.

H.T. Kung, “Why systolic architectures?”IEEE Computer, vol. 25, pp. 37–46, Jan. 1982.

H.T. Kung, L.M. Ruane, and D.W.L. Yen, “A two-level pipelined systolic array for convolutions,” inVLSI Systems and Computations, (H.T. Kung, B. Sproull, and G. Steele, eds.) Computer Science Press: Maryland, pp. 255–264, 1981.

S.Y. Kung,VLSI Array Processors, Prentice Hall: Englewood Cliffs, New Jersey 1988.

P.S. Liu and T.Y. Young, “VLSI array design under constraint of limited I/O bandwidth,”IEEE Trans. Comput. vol. C-32, pp. 1160–1170, Dec. 1983.

P.S. Liu and T.Y. Young, “VLSI array architecture for picture processing,” inPicture Engineering, (K.S. Fu and T. Kunii, eds.) Springer Verlag: New York, pp. 171–186, 1982.

C. Mead and L. Conway,Introduction to VLSI Systems, Addison-Wesley: Reading, MA pp. 271–292, 1980.

S.K. Rao,Regular Iterative Algorithms and their Implementations on Processor Arrays, Ph.D. thesis, Stanford University, Stanford, California, 1985.

M.A. Sid-Ahmed, “A systolic realization of 2-D filters,”IEEE Trans. Acoust., Speech, Signal Processing, vol. ASSP-37, pp. 560–565, Apr. 1989.

S. Sunder, F. El-Guibaly, and A. Antoniou, “Systolic implementation of two-dimensional recursive digital filters,”Proc. IEEE Sym. Circuits and Syst., New Orleans, LA, pp. 1034–1037, May 1990.

E.E. Swartzlander, Jr., “VLSI Signal Processing Systems, Kluwer Academic Publishers: Boston, 1986.

T. Venkateswarlu, C. Eswaran, and A. Antoniou, “Realization of multidimensional digital transfer functions,”Multidimensional Systems and Signal Processing, Vol. 1, pp. 179–198, 1990.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Sunder, S., El-Guibaly, F. & Antoniou, A. Systolic implementation of digital filters. Multidim Syst Sign Process 3, 63–78 (1992). https://doi.org/10.1007/BF01941018

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF01941018