Abstract

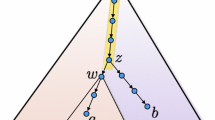

We derive here a lower bound on the number of edgesf(c, d) that one must remove from a depth-d complete binary tree in order to partition the tree intoc equal size pieces (to within rounding). We show that for the sequence of integersc l = def 3× 2l

.

We then apply this bound to a graph-embedding problem related to the design of fault-tolerant VLSI processor arrays. An earlier study has exhibited a fault-tolerant implementation of arbitrary binary trees, using a particular design strategy. We show here that that implementation is optimal in area consumption (to within constant factors) among designs using that strategy, even when the array to be simulated must have the structure of acomplete binary tree.

Similar content being viewed by others

References

S. N. Bhatt and C. E. Leiserson (1984), How to assemble tree machines. InAdvances in Computing Research 2, (F. P. Preparata, ed.) JAI Press, Greenwich, CT, pp. 95–114.

B. Bollobas, F. R. K. Chung, R. L. Graham (1983), On complete bipartite subgraphs contained in spanning tree complements. InStudies in Pure Mathematics, Akademiai Kiado, Budapest, pp. 83–90.

J. P. Hayes (1976), A graph model for fault-tolerant computing systems.IEEE Trans. Comp. C-25, 875–883.

J.-W. Hong, K. Mehlhorn, A. L. Rosenberg (1983), Cost tradeoffs in graph embeddings, with applications.J. ACM 30, 709–728.

A. L. Rosenberg (1984), On designing fault-tolerant VLSI processor arrays. InAdvances in Computing Research 2, (F. P. Preparata, ed.) JAI Press, Greenwich, CT, pp. 181–204.

A. L. Rosenberg (1985), A hypergraph model for fault-tolerant VLSI processor arrays.IEEE Trans. Comp., C-34, 578–584.

Author information

Authors and Affiliations

Additional information

The research of the second author was supported in part by NSF Grant MCS-83-01213 and in part by Bell Communications Research.

Rights and permissions

About this article

Cite this article

Chung, F.R.K., Rosenberg, A.L. Minced trees, with applications to fault-tolerant VLSI processor arrays. Math. Systems Theory 19, 1–12 (1986). https://doi.org/10.1007/BF01704902

Revised:

Accepted:

Issue Date:

DOI: https://doi.org/10.1007/BF01704902