Abstract

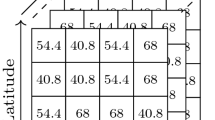

In this paper we examine the usefulness of a simple memory array architecture to several image processing tasks. This architecture, called theAccess Constrained Memory Array Architecture (ACMAA) has a linear array of processors which concurrently access distinct rows or columns of an array of memory modules. We have developed several parallel image processing algorithms for this architecture. All the algorithms presented in this paper achieve a linear speed-up over the corresponding fast sequential algorithms. This was made possible by exploiting the efficient local as well as global communication capabilities of the ACMAA.

Similar content being viewed by others

References

D. Ballard and C. Brown,Computer Vision. Englewood Cliffs, New Jersey: Prentice-Hall, 1982.

R. Buehrer, H. Brundiers, H. Benz, B. Bron, H. Friess, W. Haelg, H. Halin, A. Isacson and M. Tadian. “The ETH-Multiprocessor EMPRESS: A Dynamically Configurable MIMD System,”IEEE Transactions on Computers, C-31(11), 1982, pp. 1035–1044.

P. Danielsson and S. Levialdi, “Computer Architectures for Pictorial Information Systems,”IEEE Computer, 1981, pp. 53–67.

T.J. Fountain, K.N. Matthews, and M.J.B. Duff, “The CLIP7A Image Processor,”IEEE Transactions on Pattern Analysis and Machine Intelligence, 10(3), 1988, pp. 310–318.

R. Gonzalez and P. Wintz,Digital Image Processing. Reading, MA: Addison-Wesley 1977.

K. Hwang and K. Fu, “Integrated Computer Architectures for Image Processing and Database Management,”IEEE Computer, Vol. 16, No. 1, 1983, pp. 51–60.

B. Horn,Robot Vision. Cambridge, MA: MIT Press, 1986.

K. Hwang, P.S. Tseng, and D. Kim, “An Orthogonal Multiprocessor for Large-Grain Scientific Computations,”IEEE Transactions on Computer, 38(1), 1989, pp. 47–61.

H.A.H. Ibrahim, “Image Understanding Algorithms on Finegrained Tree-structured SIMD Machines.” Ph.D. thesis, Computer Science Dept., Columbia University, 1984.

J. Kennedy, “Simulator for a Memory Array Architecture,” M.S. Paper, Dept. of Computer Science, Penn State University, University Park, PA 16802 1989.

H.T. Kung, “Systolic Algorithms for the CMU Warp Processor,” inSeventh International Conference on Pattern Recognition, 1984, pp. 570–577.

S.-Y. Lee and J.K. Aggarwal, “Parallel 2-D Convolution on a Mesh Connected Array Processor,” inIEEE Conference on Computer Vision and Pattern Recognition, 1986, pp. 305–310.

I. Scherson and Y. Ma, “Vector Computations on an Orthogonal Memory Access Multiprocessing System,” in8th IEEE Symposium on Computer Arithmetic, 1987, pp. 28–37.

I. Scherson and Y. Ma, “Analysis and Applications of the Orthogonal Access Multiprocessor,”Journal of Parallel and Distributed Computing, 7(2), 1989, pp. 232–255.

S.R. Sternberg, “Biomedical Image Processing.”IEEE Computer, 16(1), 1983, pp. 22–34.

C. Weems, “Image Processing on a Content Addressable Array Parallel Processor.” Technical Report COINS Tech Report 84-14, University of Massachusetts, Amherst, MA, 1984.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Balsara, P.T., Irwin, M.J. Image processing on a memory array architecture. J VLSI Sign Process Syst Sign Image Video Technol 2, 313–324 (1991). https://doi.org/10.1007/BF00925473

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/BF00925473