Abstract

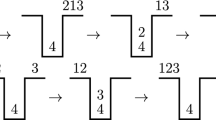

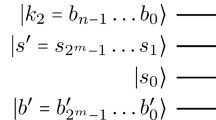

A critical problem in building long systolic arrays lies in efficient and reliable synchronization. We address this problem in the context of synchronous systems by introducing probabilistic models for two alternative clock distribution schemes: tree and straight-line clocking. We present analytic bounds for the Probability of Failure and the Mean Time to Failure, and examine the trade-offs between reliability and throughput in both schemes. Our basic conclusion is that as the one-dimensional systolic array gets very long, tree clocking becomes more reliable than straight-line clocking.

Similar content being viewed by others

References

M. Abramowitz and I. Stegun.Handbook of Mathematical Functions With Formulas, Graphs, and Mathematical Tables. Applied Mathematics Series 55, National Bureau of Standards. 1964.

M.D. Dikaiakos and K. Steiglitz, “Comparison of Tree and Straight-Line Clocking for Long Systolic Arrays”, Technical report, CS-TR-271-90, Dept. of Computer Science, Princeton University, 1990.

W. Feller,An Introduction to Probability Theory and Its Applications, volume I, New York: John Wiley, 1968.

A.L. Fisher, “Scan Line Array Processors for Image Computation,” In13th Annual Symposium on Computer Architectures, 1986, pp. 338–344.

A.L. Fisher and H.T. Kung, “Synchronizing Large VLSI Processor Arrays,”IEEE Transactions on Computers, C-34, 1984, pp. 734–740.

E. Friedman and S. Powell, “Design and Implementation of a Hierarchical Clock Distribution System for Synchronous Standard Cell/Macrocell VLSI,”IEEE Journal of Solid-State Circuits, vol. SC-21, No. 2, 1986, pp. 240–246.

Robert Gallager,Information Theory and Reliable Communication, New York: Wiley, 1960.

M.R. Greenstreet and K. Steiglitz, “Throughput of Long Self-Timed Pipelines,” Technical report, CS-TR-190-88, Dept. of Computer Science, Princeton University, 1988.

M. Greenstreet and K. Steiglitz, “Bubbles Can Make Self-Timed Pipelines Fast,”Journal of VLSI Signal Processing, vol. 2, 1990, pp. 139–148.

Mehdi Hatamian and Glenn L. Cash, “Parallel Bit-Level Pipelined VLSI Design for High-Speed Signal Processing,” InProceedings of the IEEE, vol. 75, no. 9, 1987, pp. 1192–1202.

S.Y. Kung and R.J. Gal-Ezer, “Synchronous versus Asynchronous Computation in Very Large Scale Integrated Array Processor,” InProc. SPIE, Real Time Signal Processing V, vol. 341, 1982, pp. 53–64.

S. Kugelmass and K. Steiglitz, “A Scalable Architecture for Lattice-Gas Simulations,”Journal of Computational Physics, vol. 84, 1989, pp. 311–325.

S. Kugelmass and K. Steiglitz, “An Upper Bound on Expected Clock Skew in Synchronous Systems,”IEEE Transactions on Computers, vol. 39, no. 12, 1990, pp. 1475–1477.

S. Karlin and H. Taylor,A First Course in Stochastic Processes, New York: Academic Press, 1975.

Steven D. Kugelmass, “Architectures for Two-Dimensional Lattice Computations with Linear Speedup,” Ph.D. thesis, Princeton University, 1988.

H.T. Kung, “Why Systolic Architectures?”IEEE Computer Magazine, vol. 15, 1982.

R. Maini, J. McDonald and L. Spangler, “A Clock Distribution Circuit with a 100ps Skew Window,” InProceedings of Bipolar Circuits and Technology Meeting, 1987, pp. 41–43.

Sheldon M. Ross,Introduction to Probability Models, New York: Academic Press, 1985.

Texas Instruments,The TTL Data Book for Design Engineers, 1976.

Kenneth Wagner, “Clock System Design,”IEEE Design and Test of Computers, 1988, pp. 9–21.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Dikaiakos, M.D., Steiglitz, K. Comparison of tree and straight-line clocking for long systolic arrays. J VLSI Sign Process Syst Sign Image Video Technol 2, 287–299 (1991). https://doi.org/10.1007/BF00925471

Received:

Published:

Issue Date:

DOI: https://doi.org/10.1007/BF00925471