Abstract

In this paper, a non-isolated stacked bidirectional DC-DC converter with zero-voltage-switching (ZVS) is introduced for the high step-up/step-down conversion systems. The extremely narrow turn-on and/or turn-off duty cycle existing in the conventional bidirectional buck-boost converters can be extended due to the stacked module configuration for large voltage conversion ratio applications. Furthermore, the switch voltage stress is halved because of the series connection of half bridge modules. The PWM plus phase-shift control strategy is employed, where the duty cycle is adopted to regulate the voltages between the input and output sides and the phase-shift angle is applied to achieve the power flow regulation. This decoupled control scheme can not only realize seam-less bidirectional transition operation, but also achieve adaptive voltage balance for the power switches. In addition, ZVS soft-switching operation for all active switches is realized to minimize the switching losses. Finally, a prototype of 1 kW operating at 100 kHz is built and tested to demonstrate the effectiveness of the proposed converter and the control strategy.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Energy storage systems (ESS) with bidirectional DC-DC converters are essential in renewable energy based micro-grids, electric vehicles (EVs), transportations, et al [1–5]. Bidirectional DC-DC converters play the role of converting and transferring the electrical energy of the storage elements, which conduct both charge and discharge operation. As a result, the bidirectional DC-DC converters are the key interfaces for efficient energy management. Generally, the voltage of the storage elements is relatively low due to safety issues. Meanwhile, the bus voltage of the DC-based micro-grid, electric EVs and plug-in hybrid EVs (PHEVs) is relatively high in order to improve the system power level. Consequently, a step-up and step-down bidirectional converter is required to link the low voltage storage elements and high voltage bus. How to derive high efficiency DC-DC converters with large conversion ratio is still challengeable in the power electronics community.

Isolated bidirectional DC-DC converters with high-frequency transformer, such as the Flyback-based [6, 7], Forward-Flyback based [8], boost integrated Flyback rectifier/energy (BIFRED) based [9], dual half-bridge based [10, 11], dual active bridge (DAB) based converters [12–15] and their counterparts [16–22], can easily achieve high step-up/step-down conversion because the turns ratio of the transformer provides another control freedom for the voltage regulation. However, the conduction losses and transformer losses are a little high because the whole delivered energy will flow through the power switches and windings of primary and secondary sides.

If the passive diodes in buck or boost converters are replaced by active switches, the conventional bidirectional Buck-Boost converters are formed. They suffer from large switching losses due to the hard switching operation. In order to solve this problem, some active and/or passive components are inserted to achieve zero-voltage-switching (ZVS) or zero-current-switching (ZCS) performance [12, 23–26]. However, the additional active switches may increase the control complexity and the passive components may bring extra voltage or current stress on the power switches. More importantly, extreme duty cycle and high voltage stress for the power switches are inevitable in large conversion ratio and high voltage applications, which would limit the converter efficiency and dynamic response.

In order to avoid the extreme duty cycle operation, multi-level converters are attractive candidates [27, 28]. Three level bi-directional converters are proposed by introducing the three-level tank into the conventional bidirectional converters. The switch voltage stress is only half of the high-side voltage [29]. And the inductor is reduced to improve the dynamic response due to the reduced voltage step.

An advanced non-isolated stack bidirectional DC-DC converter is proposed in [30], which has a high step-up/step-down conversion ratios. This converter is controlled by an optimized PWM method, which is divided into forward and reverse modes according to the power flow. Seamless mode change is realized by introducing an intermediate switching pattern. However, the PWM plus phase-shift control (PPS) control scheme, which is widely adopted in the isolated converters [31–33], can be employed in this non-isolated stack converter to improve the circuit performance. The duty cycle and phase shift angle of the PPS control strategy can not only balance the voltage of the high and low voltage side sources, but also regulate the power flow independently and smoothly, which eliminates the requirement of switching pattern change. Furthermore, due to the stack structure and PPS control method, the voltage stress of power switches is reduced to half of the high-side voltage and the extreme duty cycle operation is avoided in high step-up/step-down conversion systems. Moreover, ZVS soft switching operation is achieved for all the power switches without any additional active or passive components.

The outline of this paper is highlighted as follows. The brief introduction of the non-isolated stack converter with PPS control and the steady-state operation analysis are illustrated in Section 2. The performance characteristics of the converter are specified in Section 3. Besides, the phase-shift angle selection analysis is implied in Section 4. The performance of the introduced converter is verified by a 1 kW prototype in Section 5. The main contributions of this paper are summarized in the last section.

2 Bidirectional converter with PPS control and its steady-state operation analysis

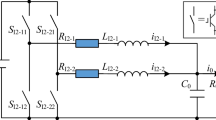

The stacked bidirectional converter in [30] is redrawn in Fig. 1. In Fig. 1, V H and V L are the high and low side voltage sources; C H1 and C H2 are the series capacitors to perform as a voltage divider in the high voltage side; S1 ~ S4 are the active switches with their parasitic capacitors C s1 ~ C s4; L r is the resonant inductor; C r is the resonant capacitor; L f and C L are the filter inductor and capacitor in the low voltage side; \(i_{{L_{\text{r}} }}\) and \(i_{{L_{\text{f}} }}\) are the currents of L r and L f; i x is the neutral current of the series capacitors; \(V_{{C_{\text{H1}} }} ,\;V_{{C_{\text{H2}} }} ,\;V_{{C_{\text{r}} }}\) are the voltages of C H1, C H2 and C r with the defined polarities; f s is the switching frequency.

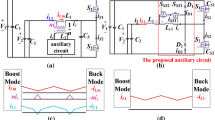

PPS control strategy is applied to the stacked converter to balance the voltage and regulate the power flow between the high and low voltage terminals. S2 is driven complementarily with S1, while S4 works complementarily with S3. S1 and S3 act with the same duty cycle D, and D is regulated to balance the high-side and low-side voltages. The phase-shift angle between S1 and S3 is indicated as φ. The range of φ is limited from −DT s to DT s. The key waveforms of the stacked converter at the steady-state operation are plotted in Fig. 2. There are two operation modes corresponding to the power flow directions. One is the buck mode, where the energy is delivered from the high side to low side, and the other is the boost mode, where the energy flows reversely. Due to the symmetrical operation of the introduced converter, the buck mode is taken as an example to analyze its steady-state operation.

In order to simplify the analysis, the following assumptions are made: ① the voltage ripples on the capacitors C H1, C H2 and C r are small and ignored; ② the voltages \(V_{{C_{\text{H1}} }} ,\;V_{{C_{\text{H2}} }}\) are balanced. There are 8 operation stages in one switching period analyzed as follows and the equivalent operation circuits are illustrated in Fig. 3.

-

1)

Stage 1: [t 0 ~ t 1]

Before t 0, S2 and S4 are both in the turn-on state and the current \(i_{{L_{\text{r}} }}\) i Lr flows through L r negatively. At t 0, S2 is turned off. Due to the capacitor C s2, ZVS turn-off for S2 is ensured. The current \(i_{{L_{\text{r}} }}\) keeps unchanged as the operation interval is short. Consequently, C s2 is charged while C s1 is discharged linearly.

-

2)

Stage 2: [t 1 ~ t 2]

At t 1, the voltage of C s1 is reduced to zero. As a result, the resonant current \(i_{{L_{\text{r}} }}\) flows through the anti-parallel diode of S1 before its turn-on gate signal comes. S1 is turned on with ZVS during this stage. \(i_{{L_{\text{r}} }}\) increases and \(i_{{L_{\text{f}} }}\) decreases linearly, and the neutral current i x is zero. The currents are derived by

-

3)

Stage 3: [t 2 ~ t 3]

At t 2, S4 is turned off. The resonant current \(i_{{L_{\text{r}} }}\) remains unchanged due to the short interval and the capacitor C s4 is charged while C s3 is discharged in a linear way, and the ZVS turn-off of S4 is achieved.

-

4)

Stage 4: [t 3 ~ t 4]

At t 3, the voltage of S3 reduces to zero and the difference of the currents \(i_{{L_{\text{r}} }}\) and \(i_{{L_{\text{f}} }}\) flows through the anti-parallel diode of S3. S3 is turned on with ZVS during this stage. Resonant capacitor C r is in parallel with C H1 through inductor L r, and \(i_{{L_{\text{r}} }}\) changes with a small slope. \(i_{{L_{\text{f}} }}\) increases linearly. The neutral current i x equals to the difference of \(i_{{L_{\text{r}} }}\) and \(i_{{L_{\text{f}} }} .\)

-

5)

Stage 5: [t 4 ~ t 5]

At t 4, S1 is turned off with ZVS. The resonant current \(i_{{L_{\text{r}} }}\) remains unchanged due to the short interval and C s1 is charged while C s2 is discharged in a linear way.

-

6)

Stage 6: [t 5 ~ t 6]

At t 5, the switching voltage of S2 reduces to zero and \(i_{{L_{\text{r}} }}\) flows through the anti-parallel diode of S2, to guarantee the ZVS turn-on for S2 during this stage. L r is in parallel with C r. As a result, \(i_{{L_{\text{r}} }}\) decreases linearly. \(i_{{L_{\text{f}} }}\) increases with the same slope as that in stage4. i x is equal to \(i_{{L_{\text{f}} }}\), and the currents are given by

-

7)

Stage 7: [t 6 ~ t 7]

At t 6, S3 is turned off with ZVS and C s3 is charged while C s4 is discharged in a linear way.

-

8)

Stage 8: [t 7 ~ t 8]

At t 7, the voltage of C s4 reduces to zero and \(i_{{L_{\text{f}} }}\) flows through the anti-parallel diode of S4. ZVS turn-on for S4 is ensured in this stage. Resonant capacitor C r is parallel connected with C H2 through inductor L r, and \(i_{{L_{\text{r}} }}\) changes with a small slope. \(i_{{L_{\text{f}} }}\) decreases with the same slope as that in stage1 and i x equals to \(i_{{L_{\text{r}} }} .\)

3 Converter performance analysis

3.1 Voltage conversion ratio

By applying the voltage-second balance principle to the filter inductor L f, it can be derived that

Which is to say, the voltage of C H2 is proportional to the output voltage V L. Then with phase-shift (PS) control of a fixed 50% duty cycle, the proposed converter will operate under an unbalanced condition for \(V_{{C_{\text{H1}} }}\) and \(V_{{C_{\text{H2}} }}\) for most input and output combinations. But with the PWM PPS control method, the duty cycle D can be set by control loop to be

So that

Equation (15) indicates that it is possible for the stacked converter to work in balanced condition for \(V_{{C_{\text{H1}} }}\) and \(V_{{C_{\text{H2}} }}\) when PPS control is employed. Thus the voltage stress of the power switches S1 ~ S4 is half of the high-side voltage due to the stack structure and voltage balance mechanism. As a result, low-voltage rated power devices can be used to reduce the conduction losses compared with conventional buck-boost bidirectional converters.

The voltage conversion ratio can be derived by

From (16), it can be concluded that a high step-down or step-up voltage conversion ratio is achieved due to the stack configuration.

3.2 Power transfer characteristics

The phase-shift angle between S1 and S3 is defined as φ, which can be employed to control the delivered power and direction. As plotted in Fig. 2a, when S1 is leading to S3, φ is defined as positive, which means the power is delivered from the high side to the low side as the buck mode. When φ is negative, the power flow reversely and the converter works at the boost mode.

When the proposed converter works under the balanced condition with PPS control, by applying the voltage-second balance to the resonant inductor L r, the voltage on the resonant capacitor can be obtained by

As the range of φ is limited from −DT s to DT s, in order to simplify the expression, α is defined as

According to the charging and discharging balance of the series capacitors in one switching cycle, the expression of i x is obtained by

From (19) and the analysis in Section 2, the equation of φ is calculated as follows.

where I o is the average current of the low side.

The delivered power is defined as

From (18)~(21), the delivered power in the buck mode can be expressed as

The expression of the delivered power in the boost mode can be calculated in a similar way. Therefore, in terms of different ranges of the phase-shift angel φ, the delivered power can be calculated by

The relationship of the delivered power and the coefficient α is illustrated in Fig. 4, according to (23) where V L = 40~56 V, V H = 400 V, f S = 100 kHz, L r = 12.8 μH.

From Fig. 4, the delivered power curves are totally symmetrical to φ = 0. The higher the low-side voltage is, the larger the maximum delivered power is. Therefore, the phase-shift angle can be a control freedom to regulate the power flow accurately.

3.3 ZVS soft-switching condition

From the operation analysis in Section 2, during the dead time interval between the turn-off of S1 and turn-on of S2, the parasitic capacitors of S1 and S2 are charged and discharged by the resonant current as shown in Fig. 3 (Stage 5). C s1 is charged by the current of L r. Due to the very short interval of the stage, it is reasonable to take the current of L r as a constant value to simplify the analysis. \(I_{{L_{\text{r}} }} (t_{ 4} )\) is the current of L r at t 4, which is derived by

The drain-source voltage increasing rate of S1 is limited by its parallel capacitor, and the ZVS turn-off operation for S1 can be achieved once the following is satisfied

where t r is the rise time of S1, which can be found in the datasheet.

In order to realize ZVS turn-on for S1, the voltage of C s1 should be discharged totally before the turn-on signal of S1 comes during Stage 1. As given in Fig. 3 (Stage 1), C s1 is charged by \(I_{{L_{\text{r}} }} (t_{ 0} ),\) which is the current of L r at t 0. \(I_{{L_{\text{r}} }} (t_{ 0} )\) is calculated as follows.

Once the falling time t f of S1 is smaller than the dead time t d, ZVS turn-on of S1 can be achieved by satisfying the following

Similar to S1, ZVS turn-off for S2, S3 and S4 can be achieved by their parallel capacitors when the following are satisfied

C s2 , C s3 and C s4 are charged by \(I_{{L_{\text{r}} }} (t_{ 0} ),\,I_{{L_{\text{f}} }} (t_{6} ) - I_{{L_{\text{r}} }} (t_{6} ),\) and \(I_{{L_{\text{f}} }} (t_{2} ) - I_{{L_{\text{r}} }} (t_{2} )\) respectively.

For the ZVS turn-on, C s2 , C s3 and C s4 are discharged by \(I_{{L_{\text{r}} }} (t_{ 4} ),\,I_{{L_{\text{f}} }} (t_{2} ) - I_{{L_{\text{r}} }} (t_{2} ),\) and \(I_{{L_{\text{f}} }} (t_{6} ) - I_{{L_{\text{r}} }} (t_{6} )\) respectively. The following expressions should be satisfied

In summary, with the PPS control strategy, ZVS soft switching performance can be achieved without adding extra power switches, which simplifies the circuit configuration.

4 Phase shift angle selection analysis

According to the charging and discharging balance of the series capacitors in one switching cycle, the equation of φ has been obtained in (20). The value of φ can be calculated by

Both φ 1 and φ 2 can be employed to achieve the required delivered power, but with different current performance of the circuit. According the analysis in Sections 2 and 3, the RMS currents of the resonant inductor can be calculated by

The curves of \(I_{{{\text{RMS}}\_L_{\text{r}} }}\)under φ 1 and φ 2 are illustrated in Fig. 5, where \(I_{{{\text{RMS}}\_L_{\text{r}} }}\) is larger with φ 1 compared with that with φ 2. Furthermore, with the decreasing of L r, the current difference is significant. A large \(I_{{{\text{RMS}}\_L_{\text{r}} }}\) means high conduction losses, and the size of the inductor would be larger. Therefore, it is preferred to select φ 2 as the phase-shift angle to regulate the power flow.

5 Experimental verifications

A 1 kW prototype is built and tested to verify the effectiveness of the introduced bidirectional converter. The circuit parameters are listed in Table 1.

Due to the stacked construction and voltage balance mechanism, 300 V rated MOSFETs can be used to realize 400 V input voltage operation. The filter parameters of L f and C L can be calculated exactly the same as that in a buck/boost converter. The resonant inductor is determined by the maximum delivered power illustrated in (23). Generally, the resonant capacitor C r should be relatively large to suppress its ripple voltage, 5% is a practical value for the voltage ripple and C r is selected to be 4.7 µF for this design.

The control block diagram of the proposed converter is introduced in Fig. 6. The PWM control loop is employed to balance \(V_{{C_{\text{H1}} }}\) and \(V_{{C_{\text{H2}} }}\) voltage. Moreover, the output filter inductor current i L is adopted for the phase shift control loop to achieve the charge/discharge current management. The digital voltage controlled oscillator (DVCO) is used to generate the phase-shift angle φ 2. With this solution, the duty cycle regulation and the phase shift control are decoupled and easy for implementation by digital signal processors (DSP).

The experimental results of the proposed converter in the buck mode at 1 kW load are shown in Fig. 7. The driving signals of the power switches are illustrated in Fig. 7a, where S1, S2 and S3, S4 operate complementarily respectively. The signal of S1 is leading of that of S3, which shows the circuit works at buck mode as analyzed in Section 2. The voltage and current waveforms of L r are implied in Fig. 7b. When S1 and S3 turn on/off synchronously, the slope of \(i_{{L_{\text{r}} }}\) is small because \(V_{{L_{\text{r}} }}\) equals to the difference between \(V_{{C_{\text{r}} }}\) and the voltage of the series capacitors, while the value of \(V_{{C_{\text{r}} }}\) is almost the same as \(V_{{C_{\text{H1}} }}\) or \(V_{{C_{\text{H2}} }}\). Meanwhile, \(i_{{L_{\text{r}} }}\) increases linearly when S1 and S4 are turned on and L r is charged by the voltage difference between the high voltage source and C r. L r is discharged by C r when S2 and S3 are turned on, leading to the decreasing of \(i_{{L_{\text{r}} }}\) with the same slope. In addition, the waveforms of \(V_{{L_{\text{f}} }}\) and \(i_{{L_{\text{f}} }}\) are shown in Fig. 7c. L f is discharged when S4 is in the turn-off state, and charged by the low voltage source when S4 is ON. The voltage balance of the series capacitors are proved in Fig. 7d, where both of \(V_{{C_{\text{H1}} }}\) and \(V_{{C_{\text{H2}} }}\) are half of the high-side voltage. \(V_{{L_{\text{r}} }}\) also equals to half of the high-side voltage, which is consistent with the previous analysis.

ZVS soft switching performance of the power switches in buck mode at full load are given in Fig. 8. From Fig. 8, ZVS turn-on and turn-off for all of the switches are implemented. Moreover, the voltage stress is only half of the high-side voltage, promoting the utilization of switches with low conduction losses.

Figures 9 and 10 demonstrate the circuit performance in the boost mode at full load. The driving signals of the power switches in the boost mode is almost the same as those in the buck mode, expect for that S3 has the leading phase. Consequently, the phase-shift angle is verified to be a control freedom for the power regulation. The voltage and current waveforms of L r and L f are illustrated in Figs. 8b, c, where the current waveforms are reversed compared with that in the buck mode. Figure 9d implies that the high-side voltage is halved equally by the voltage balance mechanism. Moreover, ZVS soft switching operations are achieved in the boost mode as shown in Fig. 10.

The measured efficiency of the proposed converter at different load conditions is plotted in Fig. 11. In the buck mode, the maximum efficiency is about 96%, and the full load efficiency is about 94.5% when V H = 400 V and V L = 48 V. When the low-side voltage increases to 56 V, the maximum efficiency is about 96.3%. In the boost mode, when V L = 48 V and V H = 400 V, the efficiency is 91.3% at full load, and the maximum efficiency is 94.7%. The efficiency reaches 95% when V L = 56 V in the boost mode. The efficiency in the buck or boost modes decreased a little when V L = 40 V due to the relatively larger conduction losses.

6 Conclusion

A stacked bidirectional DC-DC converter with PPS control has been introduced to provide an advanced solution for the large voltage conversion ratio applications. By employing PPS control scheme, high and low sides voltages are matched, the divider capacitors voltages are balanced, and flexible power flow regulation is achieved. Furthermore, ZVS soft switching is ensured to reduce the switching losses, and the stacked structure suppresses the switch voltage stress to only half of the high-side voltage. In addition, the extremely narrow duty cycle is extended compared with the conventional buck-boost converters. At last, a 1 kW prototype converter has been built to verify the effectiveness of the stacked converter, where the experimental results have illustrated that the proposed converter is a competitive candidate for the non-isolated high step-up/step-down bidirectional DC-DC conversion systems.

References

Ding G, Cao F, Zhang S et al (2014) Control of hybrid AC/DC microgrid under islanding operational conditions. J Mod Power Syst Clean Energy 14(3):223–232

Gu Y, Xiang X, Li W et al (2014) Mode-adaptive decentralized control for renewable DC microgrid with enhanced reliability and flexibility. IEEE Trans Power Electron 14(9):5072–5080

Ibanez FM, Echeverria JM, Vadillo J et al (2015) A step-up bidirectional series resonant DC/DC converter using a continuous current mode. IEEE Trans Power Electron 15(3):1393–1402

Gu Y, Li W, He X (2015) Frequency coordinating virtual impedance for autonomous power management of DC microgrid. IEEE Trans Power Electron 15(4):2328–2337

Hajian M, Robinson J, Jovcic D et al (2014) 30 kW, 200 V/900 V, thyristor LCL DC/DC converter laboratory prototype design and testing. IEEE Trans Power Electron 14(3):1094–1102

Chen G, Lee YS, Hui SY et al (2000) Actively clamped bidirectional flyback converter. IEEE Trans Power Electron 47(4):770–779

Chung HS, Cheung WL, Tang KS (2004) A ZCS bidirectional flyback DC/DC converter. IEEE Trans Power Electron 4(6):1426–1434

Zhang F, Yan Y (2009) Novel forward–flyback hybrid bidirectional DC–DC converter. IEEE Trans Ind Electron 9(5):1578–1584

Nasiri A, Nie Z, Bekiarov SB et al (2008) An on-line UPS system with power factor correction and electric isolation using BIFRED converter. IEEE Trans Ind Electron 8(2):722–730

Peng FZ, Li H, Su GJ et al (2004) A new ZVS bidirectional DC-DC converter for fuel cell and battery application. IEEE Trans Power Electron 4(1):54–65

Ma G, Qu W, Yu G et al (2009) A zero-voltage-switching bidirectional DC–DC converter with state analysis and soft-switching-oriented design consideration. IEEE Trans Ind Electron 9(1):2174–2184

Huang R, Mazumder SK (2009) A soft-switching scheme for an isolated DC/DC converter with pulsating DC output for a three-phase high-frequency-link PWM converter. IEEE Trans Power Electron 9(10):2276–2288

Bai H, Nie Z, Mi C (2010) Experimental comparison of traditional phase-shift, dual-phase-shift, and model-based control of isolated bidirectional DC–DC converters. IEEE Trans Power Electron 10(6):1444–1449

Zhou H, Khambadkone AM (2009) Hybrid modulation for dual-active-bridge bidirectional converter with extended power range for ultracapacitor application. IEEE Trans Ind Appl 9(4):1434–1442

Tao H, Duarte JL, Hendrix MAM (2008) Line-interactive UPS using a fuel cell as the primary source. IEEE Trans Ind Electron 8(8):3012–3021

Pan X, Rathore AK (2014) Novel bidirectional snubberless naturally commutated soft-switching current-fed full-bridge isolated DC/DC converter for fuel cell vehicles. IEEE Trans Ind Electron 14(5):2307–2315

Pan X, Rathore AK, Prasanna UR (2014) Novel soft-switching snubberless naturally clamped current-fed full-bridge front-end-converter-based bidirectional inverter for renewables, microgrid, and UPS applications. IEEE Trans Ind Electron 14(6):4132–4141

Kan J, Xie S, Tang Y et al (2014) Voltage-fed dual active bridge bidirectional DC/DC converter with an immittance network. IEEE Trans Power Electron 14(7):3582–3590

Kwang-Min Y, Jun-Young L (2013) A 10-kW two-stage isolated/bidirectional DC/DC converter with hybrid-switching technique. IEEE Trans Ind Electron 13(6):2205–2213

Rathore AK, Prasanna UR (2013) Analysis, design, and experimental results of novel snubberless bidirectional naturally clamped ZCS/ZVS current-fed half-bridge DC/DC converter for fuel cell vehicles. IEEE Trans Ind Electron 13(10):4482–4491

Pan X, Rathore AK (2013) Novel interleaved bidirectional snubberless soft-switching current-fed full-bridge voltage doubler for fuel-cell vehicles. IEEE Trans Power Electron 13(12):5535–5546

Prasanna UR, Rathore AK, Mazumder SK (2013) Novel zero-current-switching current-fed half-bridge isolated DC/DC converter for fuel-cell-based applications. IEEE Trans Ind Electron 13(4):1658–1668

López VM, Navarro-Crespin A, Schnell R et al (2012) Current phase surveillance in resonant converters for electric discharge applications to assure operation in zero- voltage-switching mode. IEEE Trans Power Electron 12(6):2925–2935

Zhang X, Yao C, Li C et al (2014) A wide bandgap device-based isolated quasi-switched-capacitor DC/DC converter. IEEE Trans Power Electron 14(5):2500–2510

Wu H, Lu J, Shi W et al (2012) Nonisolated bidirectional DC–DC converters with negative-coupled inductor. IEEE Trans Power Electron 12(5):2231–2235

Jung DY, Hwang SH, Ji YK et al (2013) Soft-switching bidirectional DC/DC converter with a LC series resonant circuit. IEEE Trans Power Electron 13(4):1680–1690

Kish GJ, Ranjram M, Lehn PW (2015) A modular multilevel DC/DC converter with fault blocking capability for HVDC interconnects. IEEE Trans Power Electron 15(1):148–162

Kenzelmann S, Rufer A, Dujic D et al (2015) Isolated DC/DC structure based on modular multilevel converter. IEEE Trans Power Electron 15(1):89–98

Jin K, Yang M, Ruan X et al (2010) Three-level bidirectional converter for fuel-cell/battery hybrid power system. IEEE Trans Ind Electron 10(6):1976–1986

Kwon M, Oh S, Choi S (2014) High gain soft-switching bidirectional DC-DC converter for eco-friendly vehicles. IEEE Trans Power Electron 14(4):1659–1666

Xu DH, Zhao CH, Fan HF (2004) A PWM plus phase-shift control bidirectional DC-DC converter. IEEE Trans Power Electron 4(3):666–675

Li W, Wu H, Yu H et al (2011) Isolated winding-coupled bidirectional ZVS converters with PWM plus phase shift (PPS) control strategy. IEEE Trans Power Electron 11(12):3560–3570

Li W, Xu C, Yu H et al (2014) Analysis, design and implementation of isolated bidirectional converter with winding-cross-coupled inductors for high step-up and high step-down conversion system. Proc IET Power Electron 14(1):67–77

Acknowledgements

This work was supported by National Natural Science Foundation of China (No. 51277195).

Author information

Authors and Affiliations

Corresponding author

Additional information

CrossCheck date: 10 November 2016

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

MEI, Y., JIANG, Q., YANG, H. et al. Non-isolated stacked bidirectional soft-switching DC-DC converter with PWM plus phase-shift control scheme. J. Mod. Power Syst. Clean Energy 5, 631–641 (2017). https://doi.org/10.1007/s40565-017-0266-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40565-017-0266-3