Abstract

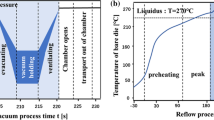

The effects of solder volume and reaction time between molten solder and a metal pad at the peak temperature of reflow on the self-alignment effect have been investigated in flip chip bonding. A glass die with two different pad designs and a flame retardant-4 (FR-4) organic substrate were used. Sn-3.0Ag-0.5Cu and Sn-3.5Ag solders were formed on Cu-organic solderability preservation (Cu-OSP) and electroless nickel electroless palladium immersion gold (ENEPIG) pads on FR-4 substrates using the stencil printing method. To assess the effect of solder volume, the thickness and opening size of the stencil mask were controlled. Reflow experiments were performed at 250°C with wetting times of 40 s, 55 s, 65 s, and 75 s. After flip chip reflow soldering, the bonding areas were cross-sectioned to inspect the shape of the interconnected solder using scanning electron microscopy. The results revealed that using an insufficient solder volume on the pad was responsible for die shifts larger than 1 μm, while a sufficient solder volume on the pad and a stable solder joint shape could ensure misalignment less than 1 μm. The Sn-3.0Ag-0.5Cu solder showed a lower die shift value than the Sn-3.5Ag solder because the Sn-3.0Ag-0.5Cu solder has stronger surface tension than the Sn-3.5Ag solder. Using a longer wetting time between the solder and the pad at the peak temperature also improved the die shift value because the increased reaction time changed the interconnected solder shape between the die and substrate from concave to convex, moving the die to a more accurate position. Furthermore, the restoring forces on die self-alignment influenced the die shift value. A stronger solder surface tension and a larger volume of solder on the pad produced stronger restoring forces for die self-alignment, thereby improving the die shift value.

Similar content being viewed by others

References

C.F. Tseng, C.S. Liu, C.H. Wu, and Douglas Yu, Proc. of Electronic Components and Technology Conference (2016), p. 1.

J.Y. Baraton, Proc. of Electronic Components and Technology Conference (2010), p. 520.

P. Liu, J. Wang, L. Tong, and Y. Tao, J. Electron. Packag. 136, 02400-1 (2014).

G. Sharma, A. Kumar, V.S. Rao, S.W. Ho, and V. Kripesh, IEEE Trans. Compon. Packag. Manuf. Technol. 1, 502 (2011).

C.H. Khong, A. Kumar, X. Zhang, G. Sharma, S.R. Vempati, and K. Vaidyanathan Proc. of Electronic Components and Technology Conference (2009), p. 535.

C. Bishop, B. Rogers, C. Scanlan, and T. Olson, Proc. of Electronic Components and Technology Conference (2016), p. 7.

F. Liu, A. Kubo, C. Nair, T. Ando, R. Furuya, S. Dwarakanath, V. Sundaram, and R.R. Tummala, Proc. of Electronic Components and Technology Conference (2016), p. 336.

H. Lu, R. Furuya, M.D. Brett, C. Sawyer, F. Nair, V.Sundram Liu, and R.R. Tummala, IEEE Trans. Compon. Packag. Manuf. Technol. 6, 959 (2016).

H.Y. Li, H.M. Chua, F.X. Che, A.D. Trigg, K.H. Teo, and S. Gao, Proc. of Electronics Packaging Technology Conference (2011), p. 341.

H.P. Park and Y.H. Kim, IEEE Electron. Lett. 53, 810 (2017).

H.P. Park, J.Y. Park, G.C. Seo, and Y.H. Kim, Proc. of Electronic Components and Technology Conference (2017), p. 2213.

G. Humpston and D.M. Jacobson, Principles of Soldering (Ohio: ASM International, 2004).

B. Su, M. Gershovich, and Y.C. Lee, Proc. of Electronic Components and Technology Conference (1997), p. 797.

Oliver Krammer, Microelectron. Reliab. 54, 457 (2014).

B.T. Tung, N. Watanabe, F. Kato, K. Kikuchi, and M. Aoyagi, Proc. of Electronic Components and Technology Conference (2014), p. 62.

Q. Tan, and Y.C. Lee, Proc. of Electronic Components and Technology Conference (1996), p. 26.

M. Hutter, H. Oppermann, G. Engelmann, L. Dietrich, and H. Reich, Proc. of Electronic Components and Technology Conference (2006), p. 1087.

A. Majumdar, J.E. Cunningham, and A.V. Krishnamoorthy, Trans. Adv. Packag. 33, 690 (2010).

D.H. Ahn, J.H. Lee, C.D. Yoo, and Y.S. Kim, J. Electron. Mater. 35, 411 (2006).

B. Fennell, S.G. Lee, and D.F. Baldwin, Microelectron. Reliab. 65, 217 (2016).

S.E. Deering and J. Szekely, J. Electron. Mater. 23, 1325 (1994).

M. Kong, S. Jeon, C.W. Hwang, and Y.C. Lee, J. Electron. Packag. 134, 12 (2012).

K.J. Puttlitz and K.A. Stalter, Handbook of Lead-Free Solder Technology for Microelectronic Assemblies (New York: IBM, CRC Press, 2004).

P. Ramm, J.J.-Q. Lu, and M.M.V. Taklo, Hand book of Wafer Bonding (Weinheim: WILEY-VCH, 2012).

T. Siewert, S. Liu, D.R. Smith, and J.C. Madeni, Properties of Lead-Free Solders (National Institute of Standards and Technology & Colorado School of Mines, Release 4.0, 2002).

C. Goncalves, H. Leitao, C.S. Lau, J.C. Teixeira, L. Ribas, S. Teixeira, M.F. Cerqueira, F. Macedo, and D. Soares, J. Mater. Sci. Mater. Electron. 26, 5106 (2015).

M. Wu and X. Su, J. Mater. Sci. Mater. Electron. 26, 8425 (2015).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Park, HP., Seo, G., Kim, S. et al. Effects of Solder Volume and Reflow Conditions on Self-Alignment Accuracy for Fan-Out Package Applications. J. Electron. Mater. 47, 133–141 (2018). https://doi.org/10.1007/s11664-017-5883-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-017-5883-0