Abstract

In this review, we provide an overview of our work in resistive switching mechanisms on oxide-based resistance random access memory (RRAM) devices. Based on the investigation of physical and chemical mechanisms, we focus on its materials, device structures, and treatment methods so as to provide an in-depth perspective of state-of-the-art oxide-based RRAM. The critical voltage and constant reaction energy properties were found, which can be used to prospectively modulate voltage and operation time to control RRAM device working performance and forecast material composition. The quantized switching phenomena in RRAM devices were demonstrated at ultra-cryogenic temperature (4K), which is attributed to the atomic-level reaction in metallic filament. In the aspect of chemical mechanisms, we use the Coulomb Faraday theorem to investigate the chemical reaction equations of RRAM for the first time. We can clearly observe that the first-order reaction series is the basis for chemical reaction during reset process in the study. Furthermore, the activation energy of chemical reactions can be extracted by changing temperature during the reset process, from which the oxygen ion reaction process can be found in the RRAM device. As for its materials, silicon oxide is compatible to semiconductor fabrication lines. It is especially promising for the silicon oxide-doped metal technology to be introduced into the industry. Based on that, double-ended graphene oxide-doped silicon oxide based via-structure RRAM with filament self-aligning formation, and self-current limiting operation ability is demonstrated. The outstanding device characteristics are attributed to the oxidation and reduction of graphene oxide flakes formed during the sputter process. Besides, we have also adopted a new concept of supercritical CO2 fluid treatment to efficiently reduce the operation current of RRAM devices for portable electronic applications.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Review

Introduction

If there was no record of culture relics and words for civilization, the era never existed in the past. People portrayed everything of life at different times in natural materials, such as stone, metal, and wood, to inherit the experience of life and prove the existence of once to be passed along. However, because the carriers of civilizations are bulky and difficult to be depicted and wrote by people, the life experience and scientific civilization can only be spread in the same place. When a major disaster or a big famine comes to here, people are forced to migrate to other environments, leading to the accumulated experience and knowledge of civilization making a fresh start. With the evolution of the times, the inventions of paper and printing bring people a convenient and light carrier of words, which causes the appearance of book. Not only the knowledge and ideas can be duplicated in books, but also they can be easily spread around the world. These inventions will make many people share the achievements of civilization. Owing to the continuous accumulation and growth of knowledge, the amount of papers and books used to store all civilizations also increase dramatically. In order to conserve these books and record the civilizations, people continue to set up the library around the world. But the space is limited; people are bound to find new ways to store knowledge. As the advent of the digital age, the problem of expansion of knowledge and information will be solved for human being.

Since the advent of the digital era, the way of digital memory is continuously in progress. Since the holes cards, magnetic matrix, tapes, magnetic cards, and hard disk used successively to nowadays flash memory invented by Simon M. Sze, the capacity and density of digital memory continues to upgrade and the speed also continuously increases. With the rise of portable electronic and Internet operations, knowledge of people around the world communicates and delivers fast anytime and anywhere. The uploaded content is no longer just text but using the manner of photos, video, and sound to record moments of life in detail, even using the websites, blogs, Facebook, etc. to communicate with each other. These progress and development are attributed to digital electronic technology and digital memory evolution.

Investigating how to enhance the progress of memory is the responsibility and obligations of people in every age. The more detailed heritage of civilization is achieved, the better the performance memory will be required. Resistance random access memory (RRAM) is a good direction of future development in memory. In recent years, continuous improvement and in-depth investigation in both materials and electrical switching mechanism not only make a breakthrough in performance of digital non-volatile memory but also look for other possibility of memory functionality.

With the demand of multi-functional electronic devices increasing greatly in the world, the investigation of device physics will be important for IC industry [1]. Furthermore, the multi-functional portable electronic products should integrate with memory [2-24], display [25-49], logic devices [50-57], and functional devices (e.g. sensor) [58,59] according to device physics and fabrication technology. Among the above-mentioned devices, the memory is important for the cultural evolution of human being. Since the origin of human civilization, different ways and media were used in transmitting historic experience and recording development of technology. From the earliest cuneiform scripts and pictograph to Greek and Latin and eventually to modern digital signal, ways to record information have been transformed from primitive stone slab and metalware carving to the Chinese invention of papermaking and printing and finally developed into nowadays memory devices [60,61]. With the transition of recording media becoming more portable and most importantly cheaper, it has promoted the development and dissemination of human culture. In addition, owing to the flourishing IC industry and notably the invention of flash non-volatile memory by Simon M. Sze [62], technology that records and transmits information has been particularly changed and boosted, laying a solid foundation for the extensive use and wide spreading of portable electronic products such as iPods, digital cameras, smart TVs, and smartphones. However, flash memory cannot keep pace with the sustained reduction of IC gate-length dimension and meanwhile fulfilling the storage needs due to the physical limit of gate oxide. Among emerging memory technologies [63-68], RRAM has the potential to become the ultimate next-generation non-volatile memory for its attributes of simple structure, good performance, and scalability [69-109]. Various materials have been reported owning RRAM properties including the extensively investigated grapheme [110-112] and its based materials. Also, graphene-based broken flakes materials are the most promising candidates to be applied in the industry owing to its special properties and relative easiness to fabricate [112].

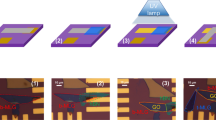

In this review, we provide an overview of our work in resistive switching mechanisms on oxide-based RRAM devices in recent years. The schematic structure of RRAM devices is shown in the top panel of Figure 1. The electrical measurement of the oxide-based RRAM devices was conducted in a variable temperature (4 to 400 K) microprobe system as shown in the bottom of Figure 1. Based on the investigation of physical mechanisms, we comprehensively research the influences and working characteristics for RRAM devices with different materials, device structures, and treatment methods.

Physical mechanisms in oxide-based RRAM devices

Recently, the switching mechanisms in metal oxide RRAM still existed various controversies. One of the most reasonable physical mechanisms is the filament formation and rupture. Many previous reports focused on the discussion of characteristics factors of filament in low-resistance state (LRS) and high-resistance state (HRS) such as resistance, temperature, and voltage [113-117]. However, there are few reports to discuss the physical mechanisms of dynamic set and reset processes in metal oxide RRAM. Therefore, we investigated the physical mechanisms of set and reset process by hafnium oxide RRAM devices.

Physical mechanism of set process in hafnium oxide RRAM devices

In this study, set process was mainly investigated to explore the relationship between voltage and pulse rising time for oxide-based RRAM devices with Ti/HfOx/TiN structure. It demonstrates that formation of filaments was directly related to the total energy of applied power.

In general, the set voltage for each specified RRAM device should be a constant, and the operating voltage needs to exceed the critical value so as to switch the device from HRS to LRS [113]. This study imposes a triangular wave under various leading time conditions with a fixed top voltage of 2 V and a trailing time of 100 ns. Same reset process was operated in DC mode to confirm the resistance at the same HRS before each setting process triggered by different leading time conditions. The critical set voltage (V C ) of RRAM device, which is the minimal voltage for a filament path formation irrelative to time, can be obtained from various triangular rising time shown in Figure 2 through a specific designed circuit measurement by a pulse generator and an oscilloscope.

Furthermore, the delta set voltage (ΔV set) can be defined as the difference between set voltage and critical set voltage from oscilloscope. The delta set time (Δt set) is defined as the time difference of corresponding set and critical set voltage. Figure 3 shows the experimental results of ΔV set − Δt set at different triangular rising times, which demonstrates that the setting process can be conformed by following formula through curve fitting:

Therefore,

If the resistive switching of metal oxide RRAM results from redox reaction mechanism, the reaction can only be triggered by sufficient energy based on electric chemical reaction theory. Therefore, we calculate the setting energy (W RRAM) over the critical voltage in the RRAM device from a critical position to a setting point as follows:

The setting energy of RRAM is constant in the same resistance state, which is proved by substituting Equation 2 into 3. From the discussion above, we present that resistive switching is directly related to a critical switching energy, which has a powerful influence on the redox reaction of RRAM set process. We think that the critical switching energy is the energy to interrupt the oxide chemical bond in the metal oxide RRAM devices during redox reaction of set process.

Atomic-level quantized reaction in RRAM reset process

From the study in previous literatures, the procedure of resistive switching is dominated by a sequential redox reaction [68,114,118-120]. The redox reaction will cause the formation and rupture of filament, leading to the resistive switching between HRS and LRS. However, the atoms involved in the reaction procedure are so few that we need to carefully design an experiment to verify the reset phenomenon in RRAM with Ti/HfOx/TiN structure. In order to examine the reset phenomenon of RRAM due to atomic-level reaction, the current versus voltage (I-V) would be analyzed at the ultra-cryogenic temperature of 4 K.

The continuous I-V curve of the RRAM device in the room temperature can be observed by the black line in Figure 4. In contrast, a special discontinuous trend of I-V curve was found at 4 K. The regularity at some regime of I-V curve can be observed by the ratio of voltage and current. Based on the Ohm’s law of R = V/I, the different ratios of voltage and current represent different resistance values. The resistance values revealed a regular phenomenon of decreased variation step by step with reset reaction procedure shown in the magnified inset of Figure 4. This quantization reaction is a different physical phenomenon with the conductance quantization in nanoscale conductive filament [121,122].

Quantization reaction for a RRAM at ultra-cryogenic temperature (4K). The inset diagram in the bottom part is an illustration to expound the discontinuous resistance variation due to quantized atomic reaction during reset process [5].

The typical resistance switching characteristics of Ti/HfOx/TiN cells were measured by DC voltage sweep mode shown in Figure 5. For the operation of RRAM, an irreversible forming procedure is required to activate the as-fabricated RRAM cells. A compliance current of 500 μA was set to prevent permanent breakdown during RRAM operation in DC-voltage sweeping mode. A sudden increase of the current was observed at the voltage of about 3.5 V to achieve the forming procedure. After forming process, a gradual descent of current interpreted the cell that was switched back to HRS from LRS while a positive bias was swept over the reset voltage (V reset, 0.55 V), which is called as ‘reset procedure’ and due to the rupture of the filament. Conversely, as the negative bias was swept over the set voltage (V set, −0.55 V), the RRAM cell will switch from HRS to LRS, i.e. ‘set procedure,’ which is attributed to the formation of filament. The inset diagram in the upper left shows that the set procedure is the transformation of HRS changed to LRS. The inset diagram in the lower right shows the reset procedure, which can be divided into different resistive stages by altering the negative stop voltage of DC sweeping cycle (V stop). The resistance value increases with increasing the V stop, leading to the multi-level resistance state obtained by controlling the V stop.

Abrupt set procedure and multistep reset procedure for oxide-based RRAM device [ 5 ].

To investigate the switching mechanism, the multiple I-V curves in Figure 5 are fitted to analyze the carrier transport of switching layer. Firstly, a good linear relationship with a slope of 1 was found in the curve of ln(I) versus ln(V), indicating that the carrier transport in LRS is dominated by Ohmic conduction. Furthermore, the different states of reset I-V curves which represent the multi-high-resistance state (multi-HRS) from stage 1 to stage 5 in the Figure 5 were fitted to analyze their carrier transport mechanism. We found that the relationship in the curve of ln(I/T 2) versus the square root of the applied voltage (V 1/2) is linear. This demonstrated that Schottky emission is considered as the main transport mechanism in multi-HRS during the reset procedure. The major leakage current is contributed from the electrons crossing the potential energy barrier between the interface of switching layer and TiN electrode by the thermionic effect. According to the formula of Schottky emission, \( J={A}^{**}{T}^2 exp\Big[\frac{-q\left({\varphi}_B-\sqrt{\raisebox{1ex}{$qV$}\!\left/ \!\raisebox{-1ex}{$4\pi {\varepsilon}_i{d}_{\mathrm{sw}}$}\right.}\right)}{kT} \), where A** is the Richardson constant, the effective switching thickness (dsw) and energy barrier height (φ B ) can be obtained from the slope and intercept of the plot of \( \sqrt{V}- \ln \left(\frac{I}{T^2}\right) \), respectively. The ε i = kε 0, and the k of HfO2 is about 25. Furthermore, the dsw and φ B of different multi-HRS in Figure 5 can also be obtained through calculation. Its dsw and φ B versus corresponding resistance for different multi-HRS in Figure 5 are shown in Figure 6. The results exhibit that the φ B was fixed about 0.7 eV and independent with corresponding resistance in different multi-HRS. This phenomenon implicates that the switching layer in different multi-HRS showed similar material properties. However, the dsw was increased with the increase of resistance value in different multi-HRS during the reset procedure. The results are attributed to the continuous conduction filament that will be ruptured gradually with the increasing of V stop, as shown in the insets of upper site of Figure 6.

Relationship among switching thickness, barrier height, and device resistance in the reset process [ 5 ].

In view of the analytic results for multi-HRS during reset procedure, the carrier transport mechanism is understood to be converted from Ohmic conduction to Schottky emission. This suggests that the conductive filament in initial LRS was oxidized through layer by layer by oxygen ions returned from the TiN electrode, and the filament was gradually disconnected from the TiN electrode to form a weak Schottky barrier during reset procedure. In the study, the experiment was designed to prove the oxidation procedure in conductive filament, which was observed by quantized resistance states with various reset voltage as shown in Figure 7. Each reset voltage was applied on device for a long time (1,000 s) to ensure complete oxidation of the conductive filament. Besides, the temperature of measurement environment was cooled down to 77 K to lessen thermodynamic effect during the reset procedure of RRAM. Figure 7 shows the correlation of the equilibrium resistance states with various reset voltage operation. The voltage bias was applied on the RRAM with suitable reaction time to initiate the oxidation of filament. The resistance states of RRAM start to change as the applied voltage exceed the first critical reaction voltage (V C1). The resistance states of RRAM were maintained at the first level of resistive states (HRS1) and the second level of high resistive states (HRS2) while the applied voltage was switched from V C1 to the second critical reaction voltage (V C2); and it was quite the same for the resistance change process when V C2 switched to the third critical reaction voltage (V C3). The resistance states of RRAM were transferred into higher resistance step by step as the reset voltage was raised gradually. The quantized reaction procedures for the RRAM transferred from the LRS to the HRS are illustrated in the upper site insets schematically. Moreover, the thickness of reaction layer will grow gradually, and the conductive filament becomes further away from the TiN electrode layer by layer. A higher reset voltage is necessary to supply enough electric field for the chemical reaction. Therefore, the resistance states would be kept until the reset voltage reaches the critical reaction electric field to initiate the next layer reaction of conductive filament. In this experiment, we demonstrated that the reset procedure of RRAM device is a layer-by-layer oxidation process. Therefore, atomic-level quantized oxidation must exist between the different reaction layers during reset procedure. This phenomenon can be observed obviously through the quantized current variation in ultra-cryogenic temperature (4 K) environment, which is shown in Figure 4.

Based on the above experiment results, the reaction began from the first layer of conductive filament close to the TiN electrode during the reset procedure. During the reaction in the first layer, the effective cross section of filament will reduce and cause the variation of resistance in RRAM. Therefore, we propose a three-dimensional diagram of filament in the LRS of RRAM to represent the continuous conduction path between TiN and Ti electrodes as shown in Figure 8. The effective conduction area of the filament would be reduced due to oxygen atoms oxidized with filament one after another, leading to the rise of the resistance value of RRAM. Because the resistance value is inversely proportional to the effective conduction area determined by the number of component atoms of conduction filament, the ratio of resistance with and without i atoms removed away in effective cross section is R N − i/R N = N/N − i. Therefore, the quantized variation of resistance can be attributed to the atomic-level reaction on the filament during the reset procedure. In order to clarify the switching mechanism, the resistance switching characteristics of RRAM were measured in the 4-K environment to eliminate the thermodynamic effects during reset procedure. The step-by-step resistance change shown in Figure 4 can be explained by the cross-sectional effective atom removal, which will result in the quantized reduction of the resistance.

Filament 3D speculation diagram. The inset shows the hexagonal-close-packed structure, where the light blue region is the effective cross section area of each atom [5].

The ratio of initial and post-reactive numbers of atom corresponds to a specific ratio of resistance states during the reset procedure. Every transition resistance states can be extracted from the slopes of experimental data in Figure 4 for each quantized step of I-V curve at ultra-cryogenic temperature (4 K). Based on the above discussion for resistance calculation, the theoretical resistance ratio of effective cross section between beginning and intermediate states can be calculated during the reset process. The experimental values complied exactly with the theoretical calculation data as shown in Figure 9. The results demonstrate that the reaction of reset procedure is an atomic-level reaction, leading to the decrease of the effective cross-sectional conduction area, which externally exhibits as the rising of resistance. The original number of atoms is 13, which is calculated from the experimental data in the intermediate region of reset procedure as shown in the enlarge inset of Figure 4. Because the magnitude of change in resistance value is not so pronounced at the beginning of reset procedure, leading to the number of atoms on effective conduction filament area in initial LRS, it is difficult to observe through Figure 4. However, we can obtain the atomic numbers of effective cross section in the initial LRS by the relationship of resistance value and conduction area of filament.

Atomic-level quantized reset reaction resistance ratio. The inset shows the cross-sectional numbers of effective atoms after reaction [5].

Because the resistance value of the filament is roughly inversely proportional to the area A, the number of component atoms in the effective cross section of filament is proportional to A. The number of component atoms in the initial LRS (#LRS) can be obtained from the resistance of 13 effective atoms (#13) acquired from the experimental data in Figure 4: #LRS = R 13 × #13/R LRS = 2,760 × 13/1,920 = 18.68. If the atoms in the filament are configured with a hexagonal lattice structure, the effective area of each atom can be indicated by the blue region of inset in Figure 8. While the lattice constant is 0.32 nm, the effective area (A #) of each atom is 0.0887 (nm2). The effective area (A LRS) of the initial LRS can be calculated as A LRS = #LRS × A # = 18.68 × 0.0887 = 1.66 (nm2). According to the simple Ohm’s law, the estimated resistivity ρ is 319 (nΩ-m), which is approximately the theoretical value of metal hafnium (ρ Hf = 331 (nΩ-m)). Therefore, we consider that the conductive filament for the carrier transport in the LRS is constructed with the elemental Hf. This is a first time to verify that the filament is constructed by Hf element in HfOx RRAM through the discussion of physical mechanisms during reset process.

Chemical mechanisms in oxide-based RRAM devices

The first-order rate law analysis of the electrochemical reaction in Ni:SiO2 thin film resistance random access memory (RRAM) devices was investigated and discussed for the mechanism of reset process. According to the relationship between the resistive switching properties and the reaction time, the reaction rate constant (k) of the first-order reaction equation in reset process of the Ni:SiO2 RRAM devices was calculated and defined. A special constant voltage sampling (CVS) method was introduced to testify the reaction rate constant, from which we obtained the same value of k, confirming the same electrochemical reaction mechanism.

Introduction of first-order rate law analysis

To inspect the properties involved in the reset process, the proportional reaction rate and the reactant concentration of the first-order rate law in electrochemical reaction were used and discussed. The first-order rate law can be expressed as, in which [A], t, and k represent the reaction production concentration, reaction time and reaction rate constant. In addition, there also exists a relationship between the reaction production concentration [A] and the charge quantity Q, which can be expressed as [Q/(q*n)]/V = mole/V = [A]. In this equation, Q/(q*n) is defined as the mole of the reaction production as a whole, in which n is the number of the reaction and q is the charge carried by one-mole electrons. Besides, V is the volume of the resistive film, which can be viewed as a constant. From this equation, we find that the reaction production concentration [A] is proportional to the charge quantity Q. By substituting this equation into the first-order rate law equation, we can obtain that the reaction rate constant k directly correlates with the slope of In(Q)-time curve. Thus by drawing out the Ln(Q)-time curve, we can evaluate the variation of constant k as shown in Figure 10.

Determination of chemical reaction rate for reset process in Ni:SiO2 RRAM

In this research, the reset voltage is defined as the point when obvious current drop exhibits and sometimes even accompanied with unstable I-V properties. Constant voltage sampling is an electrical measurement method, in which voltage bias sweeps from 0 V to the reset point and then remains unchanged. By keeping the voltage at the reset voltage, we sample the current for a period to obtain the continuing resistance change. The sampling voltage here works much more like a reading voltage, from which we can track the spontaneous chemical reaction triggered by the critical voltage point. And one constant voltage sampling result in the Ni:SiO2 RRAM is shown in Figure 11b. In this figure, the y and x axis represent current and time, respectively. From Figure 11b, we can see that the current still keeps decreasing even if the voltage remains at the reset point. Without increasing the operation voltage, continuous current drop manifests the lasting chemical reaction and this process sustains for more than 20 s. Figure 11c shows the first CVS results, and the sampling voltage is −0.9 V. By calculating Q from measurement results, we draw out the Ln(Q)-time curve, which can be seen in Figure 11c. With the increase of sampling time, Ln(Q) drops linearly within the first 10 s. From the red fitting curve, we find the slope of the Ln(Q)-time curve is −0.14. After the first CVS, another CVS measurement was conducted and the results are shown in Figure 11d. The reset voltage at this time is −1.2 V, but interestingly we get the same slope, which is −0.14. The second CVS lasts for 15 s. The same slope Ln(Q)-time curves implies the same reaction rate constant. It is quite common for RRAM to undergo slight current variation in the reset process owing to the stochastic oxidation reaction, but the same reaction rate constant involved in this random process unveils the similarities between relatively different reset situations. At the beginning of different reset processes, there will be a similar chemical reaction procedure in accordance with the first-order rate law and the reaction rate constant remains the same. Besides, even though the sampling voltages vary each other, the same k confirms the same reaction mechanism. This is quite different from our common view that higher voltage will lead to faster chemical reaction.

Bipolar switching behavior, current-time sampling, and Ln( Q )-time fitting curves for −0.9 and −1.2 V. (a) The typical bipolar switching behavior and the metal-insulator-metal (MIM) device structure and (b) the current-time sampling points of the Ni:SiO2 thin film RRAM device. (c) The Ln(Q)-time fitting curve for −0.9 V constant sampling voltage condition. (d) The Ln(Q)-time fitting curve for −1.2 V constant sampling voltage condition.

The current compliance was set with 10 mA and current-voltage curve is shown in Figure 11a. From the I-V curves, we can see the set voltage is around 1 V, and the reset voltage is about −1 V. Meanwhile, the set process is characterized by transient transformation, and the reset process is a gradual oxidation procedure, in which oxygen ions are propelled to rupture the conduction filament. Because of the random stochastic reaction relative complexity involved in the reset process, here we mainly focus our attention on the investigation of the reset process.

Chemical reaction model for reset process in Ni:SiO2 random resist access memory devices

Figure 12 shows the Ln(Q)-time curve at 30°C, from which we found that the curve can be divided into three line segments with unobvious variation on line slope. But when the temperature is increased to 60°C, the Ln(Q)-time curve reveals three line segments with different line slope. In order to further investigate the phenomena, the chemical reaction activation energy of different line segments in Ln(Q)-time curve was extracted at variable temperature according to the Arrhenius reaction equation, k = A exp(−E a/RT), where k is reaction rate constant, A is reaction intrinsic factor, E a is activation energy, and R is gas constant. After linear curve fitting and calculation for three line segments in Ln(k)-1/T curves as shown in Figure 13, we found that the activation energy of the first line segment, E a1, is 1.04 eV (101 kJ/mole), the activation energy of the second line, E a2, is 1.28 eV (124 kJ/mole), and the activation energy of the third segment, E a3, is 0.7 eV (71 kJ/mole). According to the literature reports [123], E a1 is close to O-O broken bond energy, E a2 is close to O-N broken bond energy, and E a3 is close to the migration activation energy of oxygen ion in silicon oxide solid state material.

According to the results, we propose a model to explain the oxygen ion reaction in Ni:SiO2 RRAM device to cause resistance switching process during reset process as shown in Figure 14. Firstly, the oxygen ions would be released due to the O-O bond broken in the bulk of switching layers. Then, the other oxygen ions would be released due to the O-N bond broken in the interface between resistance switching layer and TiN electrode. Finally, the released oxygen ions would be driven by the electric field to the conductive filament in RRAM device, leading to the rupture of filament due to oxidation reaction. Thus, the resistance state of RRAM device will be switched from low-resistance state to high-resistance state to complete the reset process.

Metal-doped silicon oxide-based resistance random access memory

Although the resistive switching behaviors have been presented in various metal oxide materials [124], silicon-based oxide is a promising material for RRAM applications due to its great compatibility in integrated circuit (IC) processes. Therefore, metal doped into SiO2 by cosputtering at room temperature was taken as the resistance switching layer of RRAM in this section. Furthermore, different metal elements were doped into SiO2 as the resistance switching layer to investigate the metal dopant type influence on resistive switching behaviors [125-130].

Figure 15a shows the current-voltage (I-V) properties of the control sample with the Pt/SiO2/TiN sandwich structure. The sputtered SiO2 layer exhibits no reliable RRAM properties even though the applied voltage is biased to a maximum voltage of 15 V. Figure 15b shows bipolar resistance switching characteristics of the Zn:SiO2 RRAM device by the DC voltage sweep operations. In particular, the device exhibits resistive switching behavior without forming process. For the Ni:SiO2 RRAM devices, the forming process is required to activate the as-deposited samples using DC voltage sweeping with a compliance current. A sudden increase in current occurs at a forming voltage, and the cell was transformed from the initial-resistance state (IRS) to the low-resistance state (LRS). In the Ni:SiO2 RRAM device, the resistance ratio of the HRS and the LRS is about 103 times at a reading voltage of 0.1 V, and there is no degradation after continuous I-V sweep operations as shown in Figure 15c. In the Sn:SiOx RRAM device, the resistance ratio of HRS and LRS is about 102 times at a reading voltage of 0.1 V, which is shown in Figure 15d.

I-V curve and bipolar curves of Pt/Zn:SiO 2 /TiN, Pt/Ni:SiO 2 /TiN, and Pt/Sn:SiO 2 /TiN devices. (a) Current–voltage (I-V) curve of the Pt/SiO2/TiN sandwich device at room temperature without resistive switching characteristic. Bipolar resistance switching I-V curves of (b) the Pt/Zn:SiO2/TiN device with forming-free property, (c) the Pt/Ni:SiO2/TiN device, and (d) the Pt/Sn:SiO2/TiN device.

The HRS and LRS of I-V curves were analyzed for the current conduction mechanisms in order to further discuss the resistance switching mechanisms in the metal-doped silicon oxide thin film (Zn:SiO2, Ni:SiO2, Sn:SiO2), which is shown in Figure 16. The I-V fitting results demonstrated that the current conduction in the HRS in the metal-doped thin film was dominated by the Poole-Frenkel emission mechanism. The Poole-Frenkel conduction is due to thermal emission of trapped electrons into conduction band. Based on the electrical analyses, it could be inferred that metal dopants in SiO2 may result in an increased amount of hetero-defects in the film. When the voltage was applied to the film, the electrons were emitted through the hetero-defects, from which we could verify the current conduction dominated by Poole-Frenkel mechanism. On the other hand, the HRS will transform into the LRS when the applied voltage was higher than the set voltage. In this case, results of the current fitting revealed that the current conduction was dominated by Ohmic’s conduction mechanism. We believe that the conductive filament would be formed due to the current flowing through metal-induced defects in the metal-doped silicon oxide film. The conductive filament makes the current conduction mechanism dominated by Ohmic conduction.

In general, endurance and retention tests should be conducted to evaluate the reliability properties of the non-volatile memory devices. Figure 17 shows the retention and endurance characteristics of metal-doped silicon oxide RRAM devices during reliability test. As for the retention performance, the resistance ratio of LRS/HRS remains over one order of magnitude even after 104 s at 85°C. Both HRS and LRS resistance values were measured at 0.1 V. Furthermore, over one-order resistance ratio between the HRS and the LRS can still be obtained even though over 105 cycling bias pulse operations were applied to metal-doped silicon oxide RRAM devices. These endurance and retention tests demonstrate that metal-doped silicon oxide RRAM devices possess acceptable reliabilities.

In order to analyze the influence of metal element on resistance switching characteristics in SiO2 thin film, mole fraction of each element in the metal:Si:O film was calculated from the peak areas of XPS spectra, which is shown in Table 1. In addition, endurance and retention testing results are also summarized in Table 1. The results of I-V and XPS analyses demonstrate that resistive switching properties for pure SiO2 film can be significantly improved by introducing small concentration metal dopants.

In brief, the reproducible bipolar resistance switching characteristics with acceptable reliability have been successfully achieved by doping few mole fraction of metal into the SiO2 film using the cosputtering technique at room temperature. The resistance switching performance of metal-doped SiO2 devices are improved due to a localized conduction filament confined in SiO2 layer during redox reaction of resistive switching process [125].

Multilayer graphene oxide-doped oxide-based RRAM

Except for the metal dopants’ influence research on the RRAM working performance, we have also investigated nonmetal-doped SiOx characteristics. Here in this section, we present double-ended graphene oxide (GO)-doped silicon oxide-based RRAM with comprehensive excellent quality. What is more, multi-functional property like implementation of complimentary resistive switch (CRS) [131], distinctive multi-bit characteristics in set region, and fine rheostatic behavior in reset process can be achieved. Patterned substrate is fabricated to form 1 × 1 μm size via (shown as Figure 18), in which resistive switching layer is a deposited layer by magnetron cosputtering.

Figure 19 is the TEM picture and schematic diagram of filament self-aligning formation process of the triple layer device. During electro-forming process, electrons tend to conduct through the current compliance graphene oxide (CGO) flake with lowest resistance and trigger the accumulation of metal precipitates to form a filament. The filament grows in a directional way, approaching to the switching graphene oxide (SGO) flake to form a current leakage path.

The double-ended GO triple switching layer structure possesses instinctive ability to restrict multi-filament growth that may lead to multi-switching points. The multi-filament formation reflects on the electrical characteristics as instable current-voltage curve, especially in the reset process and HRS [67]. Moreover, it is notable to mention the current compliance graphene oxide flake in top GO:SiO2 layer. Due to its finite size which defines the maximal flux of electrons, current is restricted automatically, making it easier to avoid the filament over-formation and excessive rupture. Also, it is quite normal for single layer RRAM, especially for the metal or metal oxide-based RRAM, to exhibit unstable HRS and over-shooting phenomenon in LRS, owing to the stochastic rupture of metal filament and excessive accumulation of metal precipitates, respectively [67,132]. Furthermore, the more frequent the filament over formation/rupture happens, the more unstable the current-voltage curve within, thus making it much more possible for RRAM device breakdown and degrading in continuous write/erase process. Therefore, by combining the current self-limiting property and uniform conductive path formation ability, the two-sided GO structure RRAM can undoubtedly achieve the goal of uniform resistive switching and this is confirmed by AC pulse switch test shown in Figure 20. From the testing result, the switching process of the two-sided GO structure device shows outstanding uniformity and stability even in the conventional rough unstable reset region.

To verify the excellent electrical property of the two-sided GO RRAM device, four kinds of devices are fabricated and tested, which are shown in Figure 21. In Figure 21a,b,c, and d are the schematic device structures, Figure 21e to Figure 21l are their corresponding DC (without equipment current compliance) and AC endurance test results. From DC testing result, we can find that single Zr:SiO2 exhibits no current self-limiting property but GO:SiO2/Zr:SiO2, Zr:SiO2/GO:SiO2, and GO:SiO2/Zr:SiO2/GO:SiO2 structure devices own intrinsic current restriction ability. It can be also observed that the two-sided GO RRAM device shows uniform switching during 100-cycle switching, and the memory window also remains stable compared with one-sided GO RRAM device (insets of Figure 21e-h are the corresponding distribution of HRS and LRS read at 0.1 V). To the AC endurance test, the two-sided GO device can achieve up to more than 1012 cycles. It is the first time for silicon oxide-based RRAM to reach this endurance value, comparable to the previous result of TaO-based RRAM [132].

Switching layer structure, 100-cycle current-voltage sweep, and corresponding endurance property test. a to d are the switching layer structures of the four kinds of devices. e to h are the 100-cycle current-voltage sweep without equipment current compliance. Insets of the figures are the corresponding HRS and LRS distribution with a reading voltage of 0.1 V. i to l are the endurance performance of each device.

In order to further confirm the reliability and performance of two-sided GO device, set response time, retention properties, and read disturbance immunity are tested, which are shown in Figures 22, 23, and 24.

To the two-sided GO device, resistive switching happens in the bottom GO:SiO2 layer, which results from the oxygen-contained chemical group adsorption and desorption. With the addition of more oxygen-contained chemical groups to GO, its resistance increases and meanwhile the hopping distance for electrons becomes longer. This is confirmed by ChemBio simulation (see Figure 25) and also previous research results from our group and other groups [6,133]. The current conduction model is shown schematically in Figure 26. Both GO flakes in the top and bottom GO:SiO2 layer work as the current limiter, but the bottom GO flake also plays a dominant role in the resistive switching. With the help of metal filament to concentrate electrical filed, oxygen-contained chemical groups can be attracted to or repelled from GO.

As it is the ultimate aim for device to be integrated, the scalability for RRAM device is an important factor. Owing to the inborn sneak current for cross-bar architecture, CRS memory is a promising candidate for the mass production of RRAM for its simple structure and elimination of any selector element [82]. Together with our device-instinctive current self-limiting ability, we successfully fabricated CRS memory, which is shown in Figure 27. Furthermore, in order to improve the density of integration, multi-bit storage is a simple and characteristic method for RRAM device, which needs no consideration for complex downscaling or multi-stacking. By decreasing only 0.1 V for the two-sided GO device, we obtain fine multi-bit property in reset region (see Figure 28) and this is also the first time for RRAM device to achieve such fineness.

What is more, multi-bit can be also achieved by increasing current compliance in set region (see Figure 29) and this is quite different from the single set process of Zr:SiO2 structure device (see the ole sweeping cycle multi-bit property; the double-ended GO-doped silicon oxide-based structure is a promising technique to the future mass production of RRAM for its comprehensive preferable working properties (bottom right inset of Figure 29) or metal-based RRAM device.

In summary, with its strong intrinsic current self-limiting ability, CRS implementation capability, and whole sweeping cycle multi-bit property, the double-ended GO-doped silicon oxide-based structure is a promising technique to the future mass production of RRAM for its comprehensive preferable working properties.

New low temperature process technology: supercritical fluids

The supercritical CO2 (SCCO2) fluid technology was used to improve the dielectric properties and performance of various thin film transistors (TFTs), such as hydrogenated amorphous-silicon TFTs and ZnO TFTs [134-138]. Therefore, the effect of SCCO2 treatment on RRAM was worthy to evaluate for low temperature process [139-146]. Figure 30 shows the critical point definition for supercritical fluid and the schematic diagram for SCCO2 treatment facilities. Supercritical phase is distinctive with its characteristics of high penetration of gas and solubility of liquid. The supercritical water fluid has tremendous oxidation property [147]. However, high critical temperature and high critical pressure are essential conditions to achieve supercritical water fluid. So it is difficult to realize through modern facilities (the table of Figure 30). Thus we adopted CO2, as it is easier for CO2 to achieve supercritical point and meanwhile it is relatively inert, which will not react with the treated materials. By adding a little water into supercritical CO2 fluids, the liquid water can approach to the supercritical fluid phase due to the mixed SCCO2 fluids close to idea solution.

In this section, we choose tin metal-doped silicon oxide (Sn:SiOx) as the resistance switching layer of RRAM to discuss the reaction mechanism of SCCO2 fluid on Sn:SiOx RRAM to explain the reason of electrical property improvement.

From Figure 31, we can find the leakage current of the Sn:SiOx RRAM devices after SCCO2 treatment was lower than that of pre-treatment devices. However, the forming voltage of RRAM after SCCO2 treatment is not changed. This phenomenon has been reported by our previous study [135].

The forming I-V curves of the Sn:SiO x RRAM devices before and after SCCO 2 treatment [ 146 ].

The voltage sweep bias was applied on TiN electrode with the grounded Pt electrode as shown in the bottom left inset of Figure 32. The electrical current-voltage properties of the Sn:SiOx devices were compared before and after SCCO2 treatment (Figure 32). We can find the working current of Sn:SiOx devices is remarkably reduced especially in the HRS after SCCO2 treatment.

The I-V curves are the resistive switching characteristics of Sn:SiO x film [ 146 ].

To investigate the reason of reduction on working current of Sn:SiOx, we analyzed the current conduction mechanism of Sn:SiOx thin film with and without SCCO2 treatment as shown in Figure 33. The carrier transport in LRS state of Sn:SiOx device was dominated by Ohmic conduction in the Sn:SiOx layer. After SCCO2 treatment, the current conduction mechanism will transfer to hopping conduction because of the change of material properties.

The I-V curves in the LRS of Sn:SiO x devices before and after SCCO 2 treatment. The I-V diagrams on the right were obtained through vary-temperature measurement before and after SCCO2 treatment, respectively [146].

In addition, we also analyzed the current conduction mechanism in HRS of Sn:SiOx with and without SCCO2 treatment as shown in Figure 34. The relationship in the curve of ln(I/V) versus the square root of the applied voltage (V 1/2) is linear. The results revealed that the carrier transport of Sn:SiOx film was dominated by Poole-Frenkel conduction due to the trap in the film. After SCCO2 treatment, the current conduction mechanism will transfer to Schottky emission because of the improvement of dielectric properties.

The I-V curves in the HRS of Sn:SiO x devices before and after SCCO 2 treatment. The fitting results of I-V curves in the HRS for the devices before and after SCCO2 treatment shown as the right side [146].

In order to explain the current reduction of SCCO2 treatment mechanism clearly, we proposed a reaction mode to explain the characteristics of the SCCO2-treated Sn:SiOx film, as shown in Figure 35. As the sample was put into the water-mixed SCCO2 fluid environment, the H2O molecule was carried into the grain boundary of Sn:SiOx film by SCCO2 fluid, which is attributed to the high penetration ability of SCCO2 fluid. Then, dehydration of neighbor hydroxyl groups was induced in supercritical fluids so as to form Si-O-Si and Sn-O-Si network-like bonding in the film, which is called as hydration-dehydration reaction of SCCO2 fluids in Sn:SiOx film.

The schematic diagram of hydration-dehydration reaction mechanism on Sn:SiO x film [ 146 ].

As for the LRS of Sn:SiOx film, the conductive filament will be formed in Sn:SiOx film after the forming process. Then, the carriers were transported through these dangling bonds, leading to the current conduction dominated by Ohmic conduction. If the Sn:SiOx film was put into the SCCO2 fluid environment, the tin metal in Sn:SiOx thin film will be isolated due to hydration-dehydration reaction by SCCO2 treatment. Only if the conductive filament was applied to the Sn:SiOx film, the tin metal will be isolated through SCCO2 treatment, leading to the electrical current conduction in LRS of Sn:SiOx film transferred to hopping conduction as shown in Figure 36.

The schematic diagram of carrier hopping model in Sn:SiO x film after SCCO 2 treatment [ 146 ].

On the other hand, the electrical current conduction in HRS of Sn:SiO x film will be transferred to Schottky emission from Poole-Frenkel conduction through passivation effect of SCCO2 as shown in Figure 37. This implicates that the SCCO2 can improve dielectric properties of the switching film, leading to the reduction of the working current and the power consumption of RRAM devices.

The schematic diagram of the transfer on carrier conduction mechanism in Sn:SiO x film after SCCO 2 treatment [ 146 ].

To sum up, the operation current of metal-doped silicon oxide RRAM device can be reduced by SCCO2 fluid treatment. According to the analysis of resistive switching physical mechanism, water molecules can be brought into the film to passivate the dangling bonds in the resistive switching layer due to hydration-dehydration reaction, and SCCO2 fluid treatment is undoubtedly a kind of attractive technology for the RRAM device working performance improvement. In order to discuss the advantages and disadvantages of the overall performances of silicon oxide-based RRAM devices by different fabricated methods, the comparison of silicon oxide-based RRAM devices with different fabricated methods is shown in Table 2. If the metal-doped silicon oxide is adopted as the resistive switching layer of RRAM device, the reliability performance including endurance property, retention, and operation stability can conform to the requirement of non-volatile memory. Furthermore, the outstanding performance of oxide-based RRAM (endurance property >1012 cycles, self-current limiting operation) can be demonstrated with multilayer GO-doped silicon oxide layer structure. Finally, we can reduce the operation current of silicon oxide-based RRAM for portable electronic product applications by SCCO2 fluid treatment.

Conclusions and outlook

In conclusion, we have reported the bipolar resistance switching characteristics and physical mechanisms of the oxide-based RRAM devices through ultra-cryogenic and fast I-V measurement systems. The experimental results show that the setting voltage is related to setting time, with ΔV set inversely proportional to (Δt set)− 0.5. These results can be used to correctly allocate voltage and time to control RRAM working characteristics. In addition, the switching mechanism is proved to be the redox reaction through a specific constant switching energy. The dynamic switching mechanisms during reset procedure in RRAM were also clarified by a sequential experimental design. According to the electrical measurement and analysis in ultra-cryogenic measurement systems, we verify that the ultra-fast switching speed of RRAM is attributed to several atomic reaction procedures in virtue of the atomic-level quantized phenomena in ultra-cryogenic temperature situation. Based on the investigation of resistance switching physical mechanism in RRAM devices, we designed a high performance multi-functional RRAM device by modifying the resistance switching layers, new device structures, and novel process technology. The reproducible bipolar resistance switching characteristics with acceptable reliability have been successfully achieved by doping few mole fraction of metal into the SiO2 film using the cosputtering technique at room temperature. With its strong intrinsic current self-limiting ability, CRS implementation capability, and whole sweeping cycle multi-bit property, the double-ended GO-doped silicon oxide-based structure is a promising technique to the future mass production of RRAM. Furthermore, the operation current of metal-doped silicon oxide RRAM device can be reduced by SCCO2 fluid treatment. Based on the analysis of resistive switching physical mechanism, the water molecules can be brought into the film to passivate the dangling bonds in the resistive switching layer due to hydration-dehydration reactions. In the future, we hope to spend more efforts to build up a universal model on resistive switching behaviors of oxide-based RRAM so as to boost the mass production of RRAM and also facilitate the fabrication of three-dimensional stacking structure storage circuits.

References

Sze SM. Semiconductor devices physics and technology. Hoboken, NJ, USA: Wiley; 2002.

Chang TC, Jian FY, Chen SC, Tsai YT. Developments in nanocrystal memory. Mater Today. 2011;14:608–15.

Hung MF, Wu YC, Tang ZY. High-performance gate-all-around polycrystalline silicon nanowire with silicon nanocrystals nonvolatile memory. App Phys Lett. 2011;98:162108.

Lin CC, Kuo Y, Zhang S. Nonvolatile memory devices with AlOx embedded Zr-doped HfO2 high-k gate dielectric stack. J Vac Sci Technol B. 2014;32:03D116.

Syu YE, Chang TC, Lou JH, Tsai TM, Chang KC, Tsai MJ, et al. Atomic-level quantized reaction of HfOx memristor. Appl Phys Lett. 2013;102:172903.

Chang KC, Zhang R, Chang TC, Tsai TM, Lou JC, Chen JH, et al. Origin of hopping conduction in graphene-oxide-doped silicon oxide resistance random access memory devices. IEEE Electron Device Lett. 2013;34:677–9.

Lin CC, Kuo Y. Memory functions of nanocrystalline cadmium selenide embedded ZrHfO high-k dielectric stack. J App Phys. 2014;115:084113.

Lin CC, Kuo Y. Improvement of zirconium-doped hafnium oxide high-k dielectric properties by adding molybdenum. J Vac Sci Technol B. 2013;31:030605.

Chen SC, Chang TC, Liu PT, Wu YC, Yeh PH, Weng CF, et al. Nonvolatile polycrystalline silicon thin-film-transistor memory with oxide/nitride/oxide stack gate dielectrics and nanowire channels. Appl Phys Lett. 2007;90:122111.

Chen CH, Chang TC, Liao IH, Xi PB, Hsieh J, Chen J, et al. Tungsten oxide/tungsten nanocrystals for nonvolatile memory devices. Appl Phys Lett. 2008;92:013114.

Tu CH, Chang TC, Liu PT, Liu HC, Tsai CC, Chang LT, et al. Formation of germanium nanocrystals embedded in silicon-oxygen-nitride layer. Appl Phys Lett. 2006;89:013114.

Chen WR, Chang TC, Hsieh YT, Sze SM, Chang CY. Formation of Ge nanocrystals using Si1.33Ge0.67O2 and Si2.67Ge1.33N2 film for nonvolatile memory application. Appl Phys Lett. 2007;91:102106.

Chen WR, Chang TC, Liu PT, Yeh JL, Tu CH, Lou JC, et al. Nonvolatile memory characteristics of nickel-silicon-nitride nanocrystal. Appl Phys Lett. 2007;91:082103.

Chen WR, Chang TC, Yeh JL, Sze SM, Chang CY. Reliability characteristics of NiSi nanocrystals embedded in oxide and nitride layers for nonvolatile memory application. Appl Phys Lett. 2008;92:152114.

Chen SC, Chang TC, Liu PT, Wu YC, Lin PS, Tseng BH, et al. A novel nanowire channel poly-Si TFT functioning as transistor and nonvolatile SONOS memory. IEEE Electron Device Lett. 2007;28:540–2.

Yeh PH, Chen LJ, Liu PT, Wang DY, Chang TC. Metal nanocrystals as charge storage nodes for nonvolatile memory devices. Electrochim Acta. 2007;52:2920–6.

Yang FM, Chang TC, Liu PT, Yeh PH, Chen US, Yu YC, et al. Using double layer CoSi2 nanocrystals to improve the memory effects of nonvolatile memory devices. Appl Phys Lett. 2007;90:212108.

Chen WR, Chang TC, Liu PT, Lin PS, Tu CH, Chang CY. Formation of stacked Ni silicide nanocrystals for nonvolatile memory application. Appl Phys Lett. 2007;90:112108.

Yang FM, Chang TC, Liu PT, Yeh PH, Yu YC, Lin JY, et al. Memory characteristics of Co nanocrystal memory device with HfO2 as blocking oxide. Appl Phys Lett. 2007;90:132102.

Chu TJ, Tsai TM, Chang TC, Chang KC, Pan CH, Chen KH, et al. Ultra-high resistive switching mechanism induced by oxygen ion accumulation on nitrogen-doped resistive random access memory. Appl Phys Lett. 2014;105:223514.

Huang X, Chang KC, Chang TC, Tsai TM, Shih CC, Zhang R, et al. Controllable Set Voltage in Bilayer ZnO:SiO2/ZnOx Resistance Random Access Memory by Oxygen Concentration Gradient Manipulation. IEEE Electron Device Lett. 2014;35:1227–9.

Yang XN, Zheng ZW, Wang Y, Huo ZL, Jin L, Jiang DD, et al. Gate Bias Dependence of Complex Random Telegraph Noise Behavior in 65-nm NOR Flash Memory. IEEE Electron Device Lett. 2014;36:26–8.

Chen YT, Chang TC, Yang PC, Huang JJ, Tseng HC, Huang HC, et al. Improvement of Resistive Switching Characteristics by Thermally Assisted Forming Process for SiO2-Based Structure. IEEE Electron Device Lett. 2013;34:226–8.

Wang M, Bi C, Li L, Long SB, Liu Q, Lv HB, et al. Thermoelectric seebeck effect in oxide-based resistive switching memory. Nat Commun. 2014;5:4598.

Chang GW, Chang TC, Jhu JC, Tsai TM, Syu YE, Chang KC, et al. Suppress temperature instability of InGaZnO thin film transistors by N2O plasma treatment, including thermal-induced hole trapping phenomenon under gate bias stress. Appl Phys Lett. 2012;100:182103.

Liu PT, Chou YT, Teng LF. Charge pumping method for photo-sensor application by using amorphous indium-zinc oxide thin film transistors. Appl Phys Lett. 2009;94:242101.

Tsai CT, Chang TC, Chen SC, Lo I, Tsao SW, Hung MC, et al. Influence of positive bias stress on N2O plasma improved InGaZnO thin film transistor. Appl Phys Lett. 2010;96:242105.

Chen HB, Chang CY, Lu NH, Wu JJ, Han MH, Cheng YC, et al. Characteristics of gate-all-around junctionless poly-Si TFTs with an ultrathin channel. IEEE Electron Device Lett. 2013;34:897–9.

Chen TC, Chang TC, Tsai CT, Hsieh TY, Chen SC, Lin CS, et al. Behaviors of InGaZnO thin film transistor under illuminated positive gate-bias stress. Appl Phys Lett. 2010;97:112104.

Chang GW, Chang TC, Jhu JC, Tsai TM, Syu YE, Chang KC, et al. Abnormal subthreshold leakage current at high temperature in InGaZnO thin-film transistors. IEEE Electron Device Lett. 2012;33:540–2.

Liu KH, Chang TC, Chang KC, Tsai TM, Hsieh TY, Chen MC, et al. Investigation of on-current degradation behavior induced by surface hydrolysis effect under negative gate bias stress in amorphous InGaZnO thin-film transistors. Appl Phys Lett. 2014;104:103501.

Chang GW, Chang TC, Jhu JC, Tsai TM, Chang KC, Syu YE, et al. Temperature-dependent instability of bias stress in InGaZnO thin-film transistors. IEEE Trans Electron Devices. 2014;61:2119–24.

Liu KH, Chang TC, Chou WC, Chen HM, Tsai MY, Wu MS, et al. Influence of an anomalous dimension effect on thermal instability in amorphous-InGaZnO thin-film transistors. J Appl Phys. 2014;116:154508.

Teng LF, Liu PT, Wang WY. Electrical Performance Enhancement of Al-Zn-Sn-O Thin Film Transistor by Supercritical Fluid Treatment. IEEE Electron Device Lett. 2013;34:1154–6.

Chang GW, Chang TC, Syu YE, Tsai TM, Chang KC, Tu CH, et al. Paraffin wax passivation layer improvements in electrical characteristics of bottom gate amorphous indium-gallium-zinc oxide thin-film transistors. Thin Solid Films. 2011;520:1608–11.

Chen HL, Chang TC, Young TF, Tsai TM, Chang KC, Zhang R, et al. Ultra-violet light enhanced super critical fluid treatment in In-Ga-Zn-O thin film transistor. Appl Phys Lett. 2014;104:243508.

Chung WF, Chang TC, Li HW, Chen CW, Chen YC, Chen SC, et al. Influence of H2O dipole on subthreshold swing of amorphous indium-gallium-zinc-oxide thin film transistors. Electrochem and Solid-State Lett. 2011;14:H114–6.

Huang SY, Chang TC, Chen MC, Chen SC, Tsai CT, Hung MC, et al. Effects of ambient atmosphere on electrical characteristics of Al2O3 passivated InGaZnO thin film transistors during positive-bias-temperature-stress operation. Electrochem and Solid-State Lett. 2011;14:H177–9.

Lu HY, Liu PT, Chang TC, Chi S. Enhancement of brightness uniformity by a new voltage-modulated pixel design for AMOLED displays. IEEE Electron Device Lett. 2012;27:743–5.

Chung WF, Chang TC, Li HW, Chen SC, Chen YC, Tseng TY, et al. Environment-dependent thermal instability of sol-gel derived amorphous indium-gallium-zinc-oxide thin film transistors. Appl Phys Lett. 2011;98:152109.

Chen TC, Chang TC, Hsieh TY, Tsai CT, Chen SC, Lin CS, et al. Light-induced instability of an InGaZnO thin film transistor with and without SiOx passivation layer formed by plasma-enhanced-chemical-vapor-deposition. Appl Phys Lett. 2010;97:192103.

Chen YC, Chang TC, Li HW, Chen SC, Lu J, Chung WF, et al. Bias-induced oxygen adsorption in zinc tin oxide thin film transistors under dynamic stress. Appl Phys Lett. 2010;96:262104.

Liu KH, Chang TC, Wu MS, Hung YS, Hung PH, Hsieh TY, et al. Investigation of channel width-dependent threshold voltage variation in a-InGaZnO thin-film transistors. Appl Phys Lett. 2014;104:133503.

Jhu JC, Chang TC, Chang GW, Tai YH, Tsai WW, Chiang WJ, et al. Reduction of defect formation in amorphous indium-gallium-zinc-oxide thin film transistors by N2O plasma treatment. J Appl Phys. 2013;114:204501.

Li L, Lu ND, Liu M. Effect Mobility Model in Oxide Semiconductor Thin Film Transistors With Arbitrary Energy Distribution of Traps. IEEE Electron Device Lett. 2014;35:226–8.

Tsai MY, Chang TC, Chu AK, Chen TC, Hsieh TY, Lin KY, et al. Asymmetric structure-induced hot-electron injection under hot-carrier stress in a-InGaZnO thin film transistor. Appl Phys Lett. 2013;103:143508.

Tsai MY, Chang TC, Chu AK, Hsieh TY, Chen TC, Lin KY, et al. High temperature-induced abnormal suppression of sub-threshold swing and on-current degradations under hot-carrier stress in a-InGaZnO thin film transistors. Appl Phys Lett. 2013;103:012101.

Hsieh TY, Chang TC, Chen YT, Liao PY, Chen TC, Tsai MY, et al. Hot-Carrier Effect on Amorphous In-Ga-Zn-O Thin-Film Transistors With a Via-Contact Structure. IEEE Electron Device Lett. 2013;34:638.

Hsieh TY, Chang TC, Chen TC, Chen YT, Tsai MY, Chu AK, et al. Self-Heating-Effect-Induced Degradation Behaviors in a-InGaZnO Thin-Film Transistors. IEEE Electron Device Lett. 2013;34:63–5.

Dai CH, Chang TC, Chu AK, Kuo YJ, Ho SH, Hsieh TY, et al. Hot carrier effect on gate-induced drain leakage current in high-k/metal gate n-channel metal-oxide-semiconductor field-effect transistors. Appl Phys Lett. 2011;99:012106.

Dai CH, Chang TC, Chu AK, Kuo YJ, Jian FY, Lo WH, et al. On the origin of gate-induced floating-body effect in PD SOI p-MOSFETs. IEEE Electron Device Lett. 2011;32:847–9.

Dai CH, Chang TC, Chu AK, Kuo YJ, Lo WH, Ho SH, et al. Impact of static and dynamic stress on threshold voltage instability in high-k/metal gate n-channel metal-oxide-semiconductor field-effect transistors. Appl Phys Lett. 2011;98:092112.

Tsai JY, Chang TC, Chen CE, Ho SH, Liu KJ, Lu YH, et al. Electron-electron scattering-induced channel hot electron injection in nanoscale n-channel metal-oxide-semiconductor field-effect-transistors with high-k/metal gate stacks. Appl Phys Lett. 2014;105:143505.

Chen CE, Chang TC, Chen HM, You B, Yang KH, Ho SH, et al. On the Origin of Anomalous OffCurrent Under Hot Carrier Stress in p-Channel DDDMOS Transistors With STI Structure. IEEE Electron Device Lett. 2014;35:651–3.

Ho SH, Chang TC, Lu YH, Chen CE, Tsai JY, Liu KJ, et al. Investigation of abnormal negative threshold voltage shift under positive bias stress in input/output n-channel metal-oxide-semiconductor field-effect transistors with TiN/HfO2 structure using fast I-V measurement. Appl Phys Lett. 2014;104:113503.

Tsai JY, Chang TC, Lo WH, Ho SH, Chen CE, Chen HM, et al. Abnormal threshold voltage shift under hot carrier stress in Ti1-xNx/HfO2 p-channel metal-oxide-semiconductor field-effect transistors. J App Phys. 2013;114:124505.

Ho SH, Chang TC, Wu CW, Lo WH, Chen CE, Tsai JY, et al. Investigation of an anomalous hump in gate current after negative-bias temperature-instability in HfO2/metal gate p-channel metal-oxide-semiconductor field-effect transistors. Appl Phys Lett. 2013;102:012103.

Wei TY, Yeh PH, Lu SY, Lin-Wang Z. Gigantic enhancement in sensitivity using Schottky contacted nanowire nanosensor. J Am Chem Soc. 2009;131:17690–5.

Chen HM, Chang TC, Tai YH, Chen YC, Yang MC, Chou CH, et al. Ultrahigh Sensitivity Self-Amplification Phototransistor Achieved by Automatic Energy Band Lowering Behavior. IEEE Trans Electron Devices. 2014;61:3186–90.

Distin K. Cultural evolution. UK: Cambridge University Press; 2010.

Gibson KR, Gibson KR, Ingold T. Tools, language and cognition in human evolution. UK: Cambridge University Press; 1994.

Kahng D, Sze SM. A floating gate and its application to memory devices. Bell Syst Tech J. 1967;46:1288.

Wong HP, Raoux S, Kim SB, Liang J, Reifenberg JP, Rajendran B, et al. Phase change memory. Proc IEEE. 2010;98:2201–27.

Strukov DB, Snider GS, Stewart DR, Williams RS. The missing memristor found. Nature. 2008;453:80–3.

Lankhorst MH, Ketelaars BW, Wolters RAM. Low-cost and nanoscale non-volatile memory concept for future silicon chips. Nature Mater. 2005;4:347–52.

Scott JF. Data storage - multiferroic memories. Nature Mater. 2007;6:256–7.

Waser R, Dittmann R, Staikov G, Szot K. Redox-based resistive switching memories - nanoionic mechanisms, prospects, and challenges. Adv Mater. 2009;21:2632–63.

Chen YJ, Chen HL, Young TF, Chang TC, Tsai TM, Chang KC, et al. Hydrogen induced redox mechanism in amorphous carbon resistive random access memory. Nanoscale Res Lett. 2014;9:52.

Long SB, Cagli C, Ielmini D, Liu M, Sune J. Analysis and modeling of resistive switching statistics. J App Phys. 2012;111:074508.

Syu YE, Chang TC, Tsai CT, Chang GW, Tsai TM, Chang KC, et al. Improving resistance switching characteristics with SiGeOx/SiGeON double layer for nonvolatile memory applications. Electrochem and Solid-State Lett. 2011;14:H419–21.

Chang WY, Peng CS, Lin CH, Tsai JM, Chiu FC, Chueh YL. Polarity of bipolar resistive switching characteristics in ZnO memory films. J Electrochem Soc. 2011;158:H872–5.

Hsu CH, Fan YS, Liu PT. Multilevel resistive switching memory with amorphous InGaZnO-based thin film. Appl Phys Lett. 2013;102:062905.

Chen KH, Zhang R, Chang TC, Tsai TM, Chang KC, Lou JC, et al. Hopping conduction distance dependent activation energy characteristics of Zn:SiO2 resistance random access memory devices. Appl Phys Lett. 2013;102:133503.

Guan WH, Long SB, Jia R, Liu M. Nonvolatile resistive switching memory utilizing gold nanocrystals embedded in zirconium oxide. Appl Phys Lett. 2007;91:062111.

Fan YS, Liu PT, Teng LF, Hsu CH. Bipolar resistive switching characteristics of Al-doped zinc tin oxide for nonvolatile memory applications. Appl Phys Lett. 2012;101:052901.

Tsai TM, Chang KC, Zhang R, Chang TC, Lou JC, Chen JH, et al. Performance and characteristics of double layer porous silicon oxide resistance random access memory. Appl Phys Lett. 2013;102:253509.

Huang CH, Huang JS, Lin SM, Chang WY, He JH, Chueh YL. ZnO1–x nanorod arrays/ZnO thin film bilayer structure: from homojunction diode and high-performance memristor to complementary 1D1R application. ACS Nano. 2012;6:8407–14.

Huang JW, Zhang R, Chang TC, Tsai TM, Chang KC, Lou JC, et al. The effect of high/low permittivity in bilayer HfO2/BN resistance random access memory. Appl Phys Lett. 2013;102:203507.

Liu Q, Guan W, Long SB, Jia R, Liu M, Chen J. Resistive switching memory effect of ZrO2 films with Zr+ implanted. Appl Phys Lett. 2008;92:012117.

Syu EY, Zhang R, Chang TC, Tsai TM, Chang KC, Lou JC, et al. Endurance improvement technology with nitrogen implanted in the interface of WSiOx resistance switching device. IEEE Electron Device Lett. 2013;34:864–6.

Liu M, Abid Z, Wang W, He XL, Liu Q, Guan WH. Multilevel resistive switching with ionic and metallic filaments. Appl Phys Lett. 2009;94:233106.

Zhang R, Chang KC, Chang TC, Tsai TM, Chen KH, Lou JC, et al. High performance of graphene oxide-doped silicon oxide-based resistance random access memory. Nanoscale Res Lett. 2013;8:497.

Wang Y, Liu Q, Long SB, Wang W, Wang Q, Zhang MH, et al. Investigation of resistive switching in Cu-doped HfO2 thin film for multilevel non-volatile memory applications. Nanotechnology. 2010;21:045202.

Zhang R, Tsai TM, Chang TC, Chang KC, Chen KH, Lou JC, et al. Mechanism of power consumption inhibitive multi-layer Zn:SiO2/SiO2 structure resistance random access memory. J App Phys. 2013;114:234501.

Li YT, Long SB, Zhang MH, Liu Q, Zhang S, Wang Y, et al. Resistive switching properties of Au/ZrO2/Ag structure for low voltage nonvolatile memory applications. IEEE Electron Device Lett. 2010;31:117–9.

Chang KC, Huang JW, Chang TC, Tsai TM, Chen KH, Young TF, et al. Space electric field concentrated effect for Zr:SiO2 RRAM devices using porous SiO2 buffer layer. Nanoscale Res Lett. 2013;8:523.

Guan WH, Liu M, Long SB, Liu Q, Wang W. On the resistive switching mechanisms of Cu/ZrO2:Cu/Pt. Appl Phys Lett. 2008;93:223506.

Chang KC, Tsai TM, Chang TC, Chen KH, Zhang R, Wang ZY, et al. Dual ion effect of the lithium silicate resistance random access memory. IEEE Electron Device Lett. 2014;35:530–2.

Lai YC, Hsu FC, Chen JY, He JH, Chang TC, Hsieh YP, et al. Transferable and Flexible Label-Like Macromolecular Memory on Arbitrary Substrates with High Performance and a Facile Methodology. Adv Mater. 2013;25:2733–9.

Zhang R, Chang KC, Chang TC, Tsai TM, Huang SY, Chen WJ, et al. Characterization of oxygen accumulation in indium-tin-oxide for resistance random access memory. IEEE Electron Device Lett. 2014;35:630–2.

Shih CC, Chang KC, Chang TC, Tsai TM, Zhang R, Chen JH, et al. Resistive switching modification by ultraviolet illumination in transparent electrode resistive random access memory. IEEE Electron Device Lett. 2014;35:633–5.

Chen YJ, Chang KC, Chang TC, Chen HL, Young TF, Tsai TM, et al. Resistance switching induced by hydrogen and oxygen in diamond-like carbon memristor. IEEE Electron Device Lett. 2014;35:1016–8.

Ye C, Zhan C, Tsai TM, Chang KC, Chen MC, Chang TC, et al. Low-power bipolar resistive switching TiN/HfO2/ITO memory with self-compliance current phenomenon. Appl Phys Express. 2014;7:034101.

Chen MC, Chang TC, Tsai CT, Huang SY, Chen SC, Hu CW, et al. Influence of electrode material on the resistive memory switching property of indium gallium zinc oxide thin films. Appl Phys Lett. 2010;96:262110.

Chen MC, Chang TC, Huang SY, Chang KC, Chen SC, Huang HC, et al. Influence of oxygen partial pressure on resistance random access memory characteristics of indium gallium zinc oxide. Electrochem and Solid-State Lett. 2011;14:H475–7.

Feng LW, Chang CY, Chang YF, Chen WR, Wang SY, Chiang PW, et al. A study of resistive switching effects on a thin FeOx transition layer produced at the oxide/iron interface of TiN/SiO2/Fe-contented electrode structures. Appl Phys Lett. 2010;96:052111.

Yang PC, Chang TC, Chen SC, Lin YS, Huang HC, Gan DS. Influence of bias-induced copper diffusion on the resistive switching characteristics of a SiON thin film. Electrochem and Solid-State Lett. 2011;14:H93–5.

Tseng HC, Chang TC, Huang JJ, Yang PC, Chen YT, Jian FY, et al. Investigating the improvement of resistive switching trends after post-forming negative bias stress treatment. Appl Phys Lett. 2011;99:132104.

Huang SY, Chang TC, Chen MC, Chen SC, Lo HP, Huang HC, et al. Resistive switching characteristics of Sm2O3 thin films for nonvolatile memory applications. Solid-State Electron. 2011;63:189–91.

Chen SC, Chang TC, Chen SY, Chen CW, Chen SC, Sze SM, et al. Bipolar resistive switching of chromium oxide for resistive random access memory. Solid-State Electron. 2011;62:40–3.

Tsai YT, Chang TC, Lin CC, Chen SC, Chen CW, Sze SM, et al. Influence of nanocrystals on resistive switching characteristic in binary metal oxides memory devices. Electrochem and Solid-State Lett. 2011;14:H135–8.

Wang SY, Huang CW, Lee DY, Tseng TY, Chang TC. Multilevel resistive switching in Ti/CuxO/Pt memory devices. J Appl Phys. 2010;108:114110.

Liu HT, Lv HB, Yang BH, Xu XX, Liu RY, Liu Q, et al. Uniformity Improvement in 1T1R RRAM With Gate Voltage Ramp Programming. IEEE Electron Device Lett. 2014;35:1224–6.

Sun HT, Lv HB, Liu Q, Long SB, Wang M, Xie HW, et al. Overcoming the Dilemma Between RESET Current and Data Retention of RRAM by Lateral Dissolution of Conducting Filament. IEEE Electron Device Lett. 2013;34:873–5.

Long SB, Lian XJ, Ye TC, Cagli C, Perniola L, Miranda E, et al. Cycle-to-Cycle Intrinsic RESET Statistics in HfO2-Based Unipolar RRAM Devices. IEEE Electron Device Lett. 2013;34:623–5.

Chou KI, Cheng CH, Zheng ZW, Liu M, Chin A. Ni/GeOx/TiOy/TaN RRAM on Flexible Substrate With Excellent Resistance Distribution. IEEE Electron Device Lett. 2013;34:505–7.

Zhang ZP, Gao B, Fang Z, Wang XP, Tang YZ, Sohn J, et al. All-Metal-Nitride RRAM Devices. IEEE Electron Device Lett. 2015;36:29–31.

Fang Z, Wang XP, Sohn J, Weng BB, Zhang ZP, Chen ZX, et al. The Role of Ti Capping Layer in HfOx-Based RRAM Devices. IEEE Electron Device Lett. 2014;35:912–4.

Zhang ZP, Wu Y, Wong HSP, Wong SS. Nanometer-Scale HfOx RRAM. IEEE Electron Device Lett. 2013;34:1005–7.

Gómez-Navarro C, Weitz RT, Bittner AM, Scolari M, Mews A, Burghard M, et al. Electronic transport properties of individual chemically reduced graphene oxide sheets. Nano Lett. 2007;7:3499–503.

Novoselov KS, Geim AK, Morozov SV, Jiang D, Zhang Y, Dubonos SV, et al. Electric field effect in atomically thin carbon films. Science. 2004;306:666–9.

Geim AK, Novoselov KS. The rise of graphene. Nature Mater. 2007;6:183–91.

Ielmini D, Cagli C, Nardi F. Resistance transition in metal oxides induced by electronic threshold switching. Appl Phys Lett. 2009;94:063911.

Syu YE, Chang TC, Tsai TM, Hung YC, Chang KC, Tsai MJ, et al. Redox reaction switching mechanism in RRAM device with Pt/CoSiOX/TiN structure. IEEE Electron Device Lett. 2011;32:545–7.

Lee SB, Chae SC, Chang SH, Lee JS, Seo S, Kahng B, et al. Scaling behaviors of reset voltages and currents in unipolar resistance switching. Appl Phys Lett. 2008;93:212105.

Chu TJ, Chang TC, Tsai TM, Wu HH, Chen JH, Chang KC, et al. Charge quantity influence on resistance switching characteristic during forming process. IEEE Electron Device Lett. 2013;34:502–4.

Su YT, Chang KC, Chang TC, Tsai TM, Zhang R, Lou JC, et al. Characteristics of hafnium oxide resistance random access memory with different setting compliance current. Appl Phys Lett. 2013;103:163502.

Russo U, Ielmini D, Cagli C, Lacaita AL. Self-accelerated thermal dissolution model for reset programming in unipolar resistive-switching memory (RRAM) devices. IEEE Trans Electron Devices. 2009;56:193–200.

Syu YE, Chang TC, Tsai TM, Chang GW, Chang KC, Lou JH, et al. Asymmetric carrier conduction mechanism by tip electric field in WSiOX resistance switching device. IEEE Electron Device Lett. 2012;33:342–4.

Liu Q, Long SB, Lv HB, Wang W, Niu JB, Huo ZL, et al. Controllable growth of nanoscale conductive filaments in solid-electrolyte-based ReRAM by using metal nanocrystal cover bottom electrode. ACS Nano. 2010;4:6162–8.

Tappertzhofen S, Valov I, Waser R. Quantum conductance and switching kinetics of AgI-based microcrossbar cells. Nanotechnology. 2012;23:145703.

Mehonic A, Vrajitoarea A, Cueff S, Hudziak S, Howe H, Labbe´ C, et al. Quantum conductance in silicon oxide resistive memory devices. Sci Rep. 2013;3:2708.

Atkins P. Physical Chemistry. 8th ed. India: Oxford University Press; 2005.

Chen MC, Chang TC, Chiu YC, Chen SC, Huang SY, Chang KC, et al. The resistive switching characteristics in TaON films for nonvolatile memory applications. Thin Solid Films. 2013;528:224–8.

Syu YE, Chang TC, Tsai TM, Chang GW, Chang KC, Tai YH, et al. Silicon introduced effect on resistive switching characteristics of WOX thin films. Appl Phys Lett. 2012;100:022904.

Chang KC, Tsai TM, Chang TC, Syu YE, Liao KH, Chuang SL, et al. The effect of silicon oxide based RRAM with tin doping. Electrochem and Solid-State Lett. 2012;15:H65–8.

Tsai TM, Chang KC, Chang TC, Syu YE, Chuang SL, Chang GW, et al. Bipolar resistive RAM characteristics induced by Nickel Incorporated into silicon oxide dielectrics for IC applications. IEEE Electron Device Lett. 2012;33:1696–8.

Chang KC, Tsai TM, Chang TC, Wu HH, Chen JH, Syu YE, et al. Characteristics and mechanisms of silicon oxide based resistance random access memory. IEEE Electron Device Lett. 2013;34:399–401.

Chu TJ, Tsai TM, Chang TC, Chang KC, Zhang R, Chen KH, et al. Tri-resistive switching behavior of hydrogen induced resistance random access memory. IEEE Electron Device Lett. 2014;35:217–9.

Ji L, Chang YF, Fowler B, Chen YC, Tsai TM, Chang KC, et al. Integrated one diode-one resistor architecture in nanopillar SiOx resistive switching memory by nanosphere lithography. Nano Lett. 2014;14:813–8.

Linn E, Rosezin R, Kügeler C, Waser R. Complementary resistive switches for passive nanocrossbar memories. Nature Mater. 2010;9:403–6.

Lee MJ, Lee CB, Lee D, Lee SR, Chang M, Hur JH, et al. A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta2O5-x/TaO2-x bilayer structures. Nature Mater. 2011;10:625–30.

Bagri A, Mattevi C, Acik M, Chabal YJ, Chhowalla M, Shenoy VB. Structural evolution during the reduction of chemically derived graphene oxide. Nature Chemi. 2010;2:581–7.

Tsai CT, Chang TC, Liu PT, Yang PY, Kuo YC, Kin KT, et al. Low-temperature method for enhancing sputter-deposited HfO2 films with complete oxidization. Appl Phys Lett. 2007;91:012109.

Tsai CT, Chang TC, Kin KT, Liu PT, Yang PY, Weng CF, et al. A low temperature fabrication of HfO2 films with supercritical CO2 fluid treatment. J Appl Phys. 2008;103:074108.

Chen MC, Chang TC, Huang SY, Chang KC, Li HW, Chen SC, et al. A low-temperature method for improving the performance of sputter-deposited ZnO thin-film transistors with supercritical fluid. Appl Phys Lett. 2009;94:162111.

Tsai CT, Liu PT, Chang TC, Wang CW, Yang PY, Yeh FS. Low-temperature passivation of amorphous-silicon thin-film transistors with supercritical fluids. IEEE Electron Device Lett. 2007;28:584–6.

Chen MC, Chang TC, Huang SY, Chang KC, Huang HC, Chen SC, et al. Improvement of the performance of ZnO TFTs by low-temperature supercritical fluid technology treatment. Surf Coat Technol. 2009;204:1112–5.

Chang KC, Tsai TM, Chang TC, Syu YE, Hung HC, Hung YC, et al. Low-temperature synthesis of ZnO nanotubes by supercritical CO2 fluid treatment. Electrochem Solid-State Lett. 2011;14:K47–50.

Chang KC, Tsai TM, Chang TC, Syu YE, Wang CC, Chuang SL, et al. Reducing operation current of Ni-doped silicon oxide resistance random access memory by supercritical CO2 fluid treatment. Appl Phys Lett. 2011;99:263501.

Tsai TM, Chang KC, Chang TC, Syu YE, Liao KH, Tseng BH, et al. Dehydroxyl effect of Sn-doped silicon oxide resistance random access memory with supercritical CO2 fluid treatment. Appl Phys Lett. 2012;101:112906.

Tsai TM, Chang KC, Chang TC, Chang GW, Syu YE, Su YT, et al. Origin of hopping conduction in Sn-doped silicon oxide RRAM with supercritical CO2 fluid treatment. IEEE Electron Device Lett. 2012;33:1693–5.

Chang KC, Tsai TM, Chang TC, Senior Member, IEEE, Wu HH, Chen KH, et al. Low temperature improvement method on Zn:SiOx resistive random access memory devices. IEEE Electron Device Lett. 2013;34:511–3.