Abstract

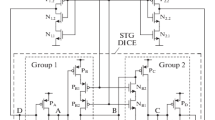

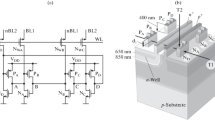

An RS trigger with a structure of transistors separated into two groups (spaced transistor groups (STGs) RS trigger) is developed and the TCAD simulation of this logical element is performed by the bulk CMOS technology with a designed size of 65 nm. The tolerance of an RS trigger to the effect of single nuclear particles is improved by separating its transistors into two groups such that the impact on one of these groups does not lead to the upset of the logical state of this trigger. In an STG RS trigger, the collection of a charge from particle tracks oriented along the normal to the crystal surface does not result in an upset during the linear energy transfer within the range of up to 50 (MeV cm2)/mg. An increase in the distance between these two groups leads to the growth of tolerance to upsets. No upsets occur in the case of topology with alternating groups of neighboring RS triggers during linear on-track energy transfers of 100 (MeV cm2)/mg. The data reading elements of 65-nm CMOS blocks of content-addressable memory (CAM) are developed based on the STG RS trigger.

Similar content being viewed by others

REFERENCES

Calin, T., Nicolaidis, M., and Velazco, R., Upset hardened memory design for submicron CMOS technology, IEEE Trans. Nucl. Sci., 1996, vol. 43, no. 6, pp. 2874–2878.

Loveless, T.D., Jagannathan, S., Reece, T., Chetia, J., Bhuva, B.L., McCurdy, M.W., Massengill, L.W., Wen, S.-J., Wong, R., and Rennie, D., Neutron- and proton-induced single event upsets for D- and DICE-flip/flop designs at a 40 nm technology node, IEEE Trans. Nucl. Sci., 2011, vol. 58, no. 3, pp. 1008–1014.

Lilja, K., Bounasser, M., Wen, S., Wong, R., Holst, J., Gaspard, N., Jagannathan, S., Loveless, D., and Bhuva, B., Single event performance and layout optimization of flip-flops in a 28-nm bulk technology, IEEE Trans. Nucl. Sci., 2013, vol. 60, no. 4, pp. 2782–2788.

Katunin, Yu.V., Stenin, V.Ya., and Stepanov, P.V., Modeling the characteristics of trigger elements of two-phase CMOS logic, taking into account the charge sharing effect under exposure to single nuclear particles, Russ. Microelectron., 2014, vol. 43, no. 2, pp. 112–124.

Stenin, V.Ya., Simulation of the characteristics of the DICE 28-nm CMOS cells in unsteady states caused by the effect of single nuclear particles, Russ. Microelectron., 2015, vol. 44, no. 5, pp. 324–334.

Stenin, V.Ya., Katunin, Yu.V., and Stepanov, P.V., Upset-resilient RAM on STG DICE memory elements with the spaced transistors into two groups, Russ. Microelectron., 2016, vol. 45, no. 6, pp. 419–432.

Katunin, Yu.V. and Stenin, V.Ya., Simulation of single event effects in STG DICE memory cells, Russ. Microelectron., 2018, vol. 47, no. 1, pp. 20–33.

Katunin, Yu.V. and Stenin, V.Ya., The multiport CMOS memory cell based on the dice trigger with two spaced transistor groups for hardened 65-nm CMOS RAM, in Proceedings of International Siberian Conference on Control and Communications, Moscow, 2016, pp. 1–5.

Katunin, Yu.V. and Stenin, V.Ya., The STG DICE cell with the decoder for reading data in steady and unsteady states for hardened SRAM, in Proceedings of Radiation Effects on Components and Systems Conference RADECS, Genewa, Switzerland, October 2017, pp. 1–8.

Stenin, V.Ya., and Antonyuk, A.V., Design of the CMOS comparison elements on STG DICE for a content-addressable memory and simulation of single-event transients, Telfor J., 2017, vol. 9, no. 1, pp. 61–66.

Katunin, Yu.V. and Stenin, V.Ya., TCAD simulation of single-event transients in the 65-nm CMOS element of matching for a content-addressable memory, in Proceedings of Telecommunications Forum TELFOR 25, Belgrad, Serbia, November 2017, pp. 1–4.

Stenin, V.Ya. and Stepanov, P.V., Basic memory elements using DICE cells for fault-tolerant 28 nm CMOS RAM, Russ. Microelectron., 2015, vol. 44, no. 6, pp. 368–379.

Stenin, V.Ya., Antonyuk A.V., Katunin, Yu.V., and Stepanov, P.V., Design of logical elements for the 65-nm CMOS translation lookaside buffer with compensation of single events effects, in Proceedings of International Siberian Conference on Control and Communications, Astana, Kazakhstan, June 2017, pp. 1–6.

Stenin, V.Ya., Antonyuk, A.V., Stepanov, P.V., and Katunin, Yu.V., Design of the 65-nm CMOS translation lookaside buffer on the hardened elements, in Proceedings of Telecommunications Forum TELFOR 25, Belgrad, Serbia, November 2017, pp. 1–4.

Wang, W. and Gong, H., Edge triggered pulse latch designed with delayed latching edge for radiation hardened application, IEEE Trans. Nucl. Sci., 2004, vol. 51, no. 6, pp. 3626–3630.

Garg, R. and Khatri, S.P., Analysis and Design of Resilient VLSI Circuits: Mitigating Soft Errors and Process Variations, New York: Springer, 2010, pp. 194–205.

Soft Errors in Modern Electronic Systems, Nicolaidis, M., Ed., New York: Springer, 2011, pp. 35–37.

Author information

Authors and Affiliations

Corresponding authors

Additional information

Translated by E. Glushachenkova

Rights and permissions

About this article

Cite this article

Stenin, V.Y., Katunin, Y.V. Simulation the Effects of Single Nuclear Particles on STG RS Triggers with Transistors Spacing into Two Groups. Russ Microelectron 47, 407–414 (2018). https://doi.org/10.1134/S1063739718060082

Received:

Published:

Issue Date:

DOI: https://doi.org/10.1134/S1063739718060082