Abstract

Benefit from exceptional electrical transport properties, graphene receives worldwide attentions, especially in the domain of high frequency electronics. Due to absence of effective bandgap causing off-state the device, graphene material is extraordinarily suitable for analog circuits rather than digital applications. With this unique ambipolar behavior, graphene can be exploited and utilized to achieve high performance for frequency multipliers. Here, dual-gated graphene field-effect transistors have been firstly used to achieve frequency quadrupling. Two Dirac points in the transfer curves of the designed GFETs can be observed by tuning top-gate voltages, which is essential to generate the fourth harmonic. By applying 200 kHz sinusoid input, arround 50% of the output signal radio frequency power is concentrated at the desired frequency of 800 kHz. Additionally, in suitable operation areas, our devices can work as high performance frequency doublers and frequency triplers. Considered both simple device structure and potential superhigh carrier mobility of graphene material, graphene-based frequency quadruplers may have lots of superiorities in regards to ultrahigh frequency electronic applications in near future. Moreover, versatility of carbon material system is far-reaching for realization of complementary metal-oxide-semiconductor compatible electrically active devices.

Similar content being viewed by others

Introduction

Frequency multipliers, cooperated with low frequency local oscillators, can provide high frequency electromagnetic signal for radio astronomy, radar technology and other communication applications1,2,3. Frequency multipliers with high multiplication factors can release required operation frequency of local oscillator systems, which results in an easily available high frequency generator. However, in conventional frequency multipliers, output powers of high-order harmonics are much lower than low-order harmonics. Therefore, high-multiplication frequency multipliers are often achieved by cascading multi-stage frequency doublers4,5,6. However, this kind of high-multiplication frequency multiplier is complex in the structure and usually costly.

On the other side, graphene, the first discovered two-dimension monolayer material7, has aroused extensive research interests due to its outstanding electronic7,8, optical9,10, mechanical11, and thermal properties12. Combining its ultra-high electron mobility, tunable electronic transport polarity and ultrastrong intrinsic strength, graphene functions as a promising candidate for solid electronic13,14,15,16, flexible electronic17,18,19, and sensing20,21,22,23. Graphene has wide applications for future high frequency electronics because of its ultrahigh carrier mobility and saturation velocity8. With the unique ambipolar behavior, graphene field effect transistor (GFET) based frequency doublers24,25, frequency triplers26, mixers27,28, and demodulators29 have been accomplished. Due to linear dispersion relation of energy band of graphene30, Fermi level of graphene can be easily shifted across the Dirac cone from valence band to conduction band or reversely by applying a tunable external electrostatic field, thus resulting in the V-shaped transfer characteristic (Ids–Vgs) curves of GFETs31. With this new type non-linear transfer characteristic, several groups have achieved frequency doublers with high output signal purity (>90%) with just a single GFET and without any additional filters24,25,32. Chen et al. developed the new concept and reported the first graphene-based frequency tripler constructed by two GFETs connected in series26. By separately tuning the doping levels of graphene in the two GFETs with an external electrostatic field, a W-shaped transfer characteristic was obtained, which is critical for high spectral purity (>70%) frequency triplers26. However, one GFET is enough for the purpose of frequency tripling. We have reported a pure frequency tripler with ultrahigh output signal purity (>94%) with only one GFET for the first time33. The CVD grown graphene with micron scale graphene flakes interspersed on the surface was used as the channel material of the GFET. A W-shaped transfer curve was obtained due to different doping levels of the single layer graphene and the bilayer graphene in the channel. In order to achieve a high performance frequency quadrupler with our reported device structures, lots of work optimizing synthesis conditions would be required to achieve a more perfect W-shaped transfer curve with two symmetrical Dirac points. In this work, a much simpler method was carried out to realize a tunable W-shaped transfer curve with two Dirac points. More specifically, a dual-gated GFET with a W-shaped transfer curve was firstly used to achieve frequency quadrupling. With an input of 200 kHz sinusoid signal, about half of the output signal radio frequency (RF) power is concentrated at desired 800 kHz. Moreover, in suitable operation areas, our devices can also work as high performance frequency doublers and frequency triplers, respectively. Compared with the first reported graphene-based frequency tripler26, this work shows a remarkable improvement in operation bandwidth with a relative simple device configuration. The simple device structure and potential superhigh carrier mobility of graphene make this graphene-based frequency quadrupler prospective for ultrahigh-frequency electronic applications in the future. Complementary metal-oxide-semiconductor (CMOS) compatible fabrication processes give these carbon material-based devices a chance to replace traditional silicon material in analog circuit, especially in RF applications.

Results and Discussion

Structure design and device fabrication

The V-shaped transfer curves can be obtained easily in GFETs if homogeneous graphene material is used as the channel material7. Total channel resistance (Rtotal) can be written as34:

where RC is the metal/graphene contact resistance (nearly a constant)35, W and L are the width and the length of the channel, respectively, μ is the mobility of the charge carrier, n0 is the electron-hole puddle36 concentration (a constant), e is the electron charge, and n is gate (VG) dependent charge carrier concentration which can be described by:

where, ε and t are the permittivity and thickness of the dielectric layer and VDirac is the gate voltage of charge neutrality point. Hence n equals to zero with VG reaching VDirac, and the minimal drain current of the V-shaped transfer curve can be obtained as Rtotal reaches the peak value. However, if inhomogeneous graphene, such as a graphene PN junction37, is used in the FET channel, then equation (1) will be replaced by:

as two graphene parts are connected in series. Here, L1 and L2 are the length of the N-type doping graphene and P-type doping graphene, respectively. μ1 and μ2 are the carrier mobility in the two regions. As equation (2), the charge carrier concentrations in the two different regions can be given by:

where VDirac1 and VDirac2 are the Dirac voltage of N-type region and P-type region, respectively. With different values of VDirac1 and VDirac2, two maxima will be discovered in Rtotal at gate voltages of VDirac1 and VDirac2.

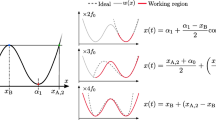

Figure 1a and b sketchily display formation of the W-shaped transfer curve in a single GFET with two different graphene parts connected in series as the channel material. In Fig. 1a, due to different doping levels, gate voltages for resistance maxima in graphene 1 (red line) and graphene 2 (blue line) are different. The black line with two resistance maxima is the total channel resistance of GFET. Since the drain current is inversely proportional to the total channel resistance, a W-shaped transfer curve with two conductance minima can be obtained, which is shown in Fig. 1b. Figure 1c shows how GFETs with W-shaped transfer curves can work as frequency quadruplers. The device can generate four-cycle waveform at Vout with one-cycle input Vin. Therefore, a frequency quadrupler can be realized with only one GFET if two different graphene parts with different doping levels, such as graphene PN junctions, are formed in the channel.

(a) Both resistances of graphene 1(R1) and graphene 2 (R2) with different doping levels and the total channel resistance of them connected in series (Rtotal) are as a function of gate voltage. (b) The corresponding transfer curve is shown as the drain current is inversely proportional to total channel resistance. (c) Generation of four-cycle waveform at Vout from one-cycle input Vin results from relationship between Ids and Vgate in the working area.

Although no effective bandgap, graphene-based PN junctions find their applications in electronic38,39 and optoelectronic fields40,41. Stable graphene PN junctions can be obtained by electrostatic doping42,43, chemical doping44,45, substrate engineering46 and photoinduced doping47,48. Among these methods, electrostatic doping method is tunable in real time by applying variable gate voltages42,43. In our case, a tunable doping method is aspired for the purpose of achieving a tunable W-shaped transfer curve. Therefore, a narrow top gate (TG) is utilized to dope the underneath graphene with electrostatic field and form PN junctions in the graphene channel of GFET. A dual-gated GFET is designed and fabricated to achieve frequency quadrupling function for the first time since the dual-gated GFET structure can modulate charge transport characteristics in graphene films efficiently34. In this case, the total channel resistance can be derived as:

where L is the channel length, LTG is the length of the TG, and the charge carrier concentrations in graphene under the TG and away from the TG can be given by:

where ε1, ε2 and t1, t2 are the permittivities and thicknesses of the back gate (BG) dielectric layer and TG dielectric layer, respectively, VDiarc BG is the Dirac voltage of the channel graphene without TG and VBG is the BG voltage. The peak value of Rtotal can be obtained by setting either equation (7) or equation (8) to zero. Therefore, a W-shaped transfer curve with two Dirac points can be achieved with this dual-gated GFET structure. The values of the two Dirac voltages can be obtained from equation (7) and equation (8), respectively, which are shown as:

Hence the newly arising Dirac voltage VBG1 is tunable with variable TG voltages and a linear relation can be observed from equation (9).

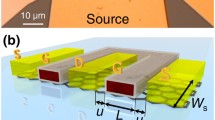

The three-dimensional schematic of the dual-gated GFET-based frequency quadrupler is shown in Fig. 2a. The P++ silicon with the SiO2 cover layer works as global BG. The narrow Ti/Au finger with Al2O3 bottom layer is utilized as local TG. With suitable TG voltage, the one-cycle input electronic signals applying to global BG can result in the four-cycle output signals at the drain electrode. The circuit implementation of the frequency quadrupler is displayed in Fig. 2b. A common-source topology is used for dual-gated GFET in this frequency quadrupler. At first, a suitable voltage VTG is applied to the TG to achieve electrostatic doping in the underneath graphene. Direct-current (DC) voltage VBG is applied to BG to bias the working point of the frequency quadrupler, while an alternating current (AC) sinusoidal input signal Vin is added to VBG. VS is connected to the ground. High performance bias tee is utilized to apply DC bias and extract the output RF power.

(a) The three-dimensional layout of the basic device structure. The P++ silicon with the SiO2 cover layer is working as global BG and the narrow Ti/Au finger with the Al2O3 bottom layer is utilized as local TG. A one-cycle input electronic signal at BG can result in a four-cycle output signal at the drain electrode. (b) Circuit schematic used in this work to actualize the dual-gated GFET-based frequency quadruplers. A high performance bias tee was used to apply DC bias and extract output RF power. (c) The device began from a heavily doped silicon wafer. (d) A SiO2 layer with thickness of 100 nm was completed by a dry thermal oxidization process. (e) Wet-transfer of CVD grown graphene onto the surface of the SiO2 layer. The patterned graphene was defined by lithography and O2 plasma etching. (f) With photolithography, thermal evaporated and lift-off processes, Au/Ti pads working as contact electrodes were obtained. (g) Al2O3 layer with thickness of 40 nm was achieved on graphene with an ALD technique. Before this process, a 1 nm Al seed layer was deposited on graphene with electron beam evaporation. (h) The device was completed with fabrication of the Ti/Au finger working as local TG in the center of the GFET channel.

The detailed device fabrication process of dual-gated GFETs is schematically illustrated in Fig. 2c–h. A heavily doped silicon chip was used as the substrate and global BG (Fig. 2c). Then the silicon wafer was put into an atmospheric thermal oxidation furnace with a temperature of 1000 °C for 3 h. A 100 nm-thick SiO2 layer working as the dielectric layer of BG was formed on the surface of the silicon substrate (Fig. 2d). Then the commercial CVD grown graphene film was transferred onto the surface of the thermal oxidization SiO2 layer after the copper foil being etched away. The photolithography and O2 plasma etching were successively used to fabricate the patterned graphene channel (50 μm * 20 μm) that works as the active region (Fig. 2e). The Ti (10 nm)/Au (200 nm) films working as metal contacts were competed by lift-off in acetone after the photolithography and thermal evaporated processes (Fig. 2f). In order to obtain the dielectric layer for TG, 40 nm Al2O3 dielectric was generated on the graphene films successfully by atomic layer deposition (ALD) (Fig. 2g). Here, it should be noted that before the ALD process, a 1 nm Al seed layer was deposited on the graphene surface with electron beam evaporation. After deposition of the Al2O3 dielectric layer, photolithography and wet etching processes were carried out to etch the Al2O3 layer on the surface of the contact pads. At last, the Ti (10 nm)/Au (200 nm) films working as TG were finished by lift-off in acetone after the photolithography and thermal evaporated processes (Fig. 2h). As the fabrication temperatures of these processes mentioned above are lower than 200 °C, CMOS compatible fabrication process is achieved49.

Characterization of the fabricated device

Before deposition of the Al2O3 dielectric layer, Raman spectrum (Fig. 3a) of graphene was obtained utilizing a 532 nm excited laser with incident power of 5 mW and laser spot diameter of 20 μm. Intensity ratio of 2D/G is 3, indicating monolayer nature of the CVD graphene sample. The almost invisible D band suggests high quality of the graphene film. Figure 3b shows the optical micrograph of the fabricated dual-gated GFET-based frequency quadrupler. The channel length and width of fabricated GFET are 9.5 μm and 20 μm, respectively. The length of TG is 2.3 μm. The white dotted frame shows location of the single layer graphene. The graphene layer was visible on the surface of the 100 nm SiO2 layer and became invisible after deposition of 40 nm Al2O3 layer. Scanning electron microscopy (SEM) image of the device surface is displayed in Fig. 3c. The boundary of the buried graphene layer can be discovered with easiness because of high electrical conductivity of graphene.

(a) Raman spectrum of monolayer graphene obtained at the position of the black dot in the inset. (b) Optical microscope image of dual-gated GFET and the white dotted frame shows the graphene location. The scale bar is 10 μm. (c) SEM of the device surface where the graphene boundary can be discovered due to high electrical conductivity of graphene. The length of TG is 2.3 μm.

Static response of the device

Figure 4 shows the DC transfer curves of dual-gated GFET with different TG voltages. BG voltage VBGS (VBG-VS) swept from −30 V to 0 V and bias voltage Vds (VD-VS) was set at 1 V. By decreasing TG voltage VTGS (VTG-VS) from −1 V to −8 V, the second obvious Dirac point is arising. When VTGS was set at −1 V, only one Dirac point at about −21 V is discovered, indicating homogenization of the whole graphene channel and heavy n-type doping of the original graphene. When VTGS was decreased to −8 V, two clear conductance minima can be found at the BG voltages of about −21 V and −4 V, respectively. Occurrence of the second Dirac point at −4 V indicates formation of soft n-doped graphene underneath TG. The inset shows relationship between location of the newly formed Dirac point and TG voltages and illustrates that new Dirac voltage is approximately a linear function of TG voltage, which agrees well with equation (9). With decrease of TG voltage, an increasing number of holes will be injected into the graphene layer underneath TG due to capacitance effect, which results in decrease of the doping level of graphene. As the doping level of original heavy n-type graphene away from TG in the channel remains unchanged, a constant Dirac voltage at −21 V (in agree with equation (10)) can be discovered. An interesting phenomenon is that the new Dirac point becomes obvious with decrease of VTGS. In other words, the total area of the soft n-doped graphene increases with decrease of VTGS. Therefore, resistance of this part graphene plays a growing important role in the total channel resistance. The reason is that TG can dope the graphene near the TG edges due to edge effect of the capacitor structure and the total doping range increases when VTGS decreases (increase in absolute value). Nonlinear behaviour in the inset at lower VTGS is another result of edge effect proposed above. Therefore, with narrow TG for underneath graphene electrostatic doping, obvious inhomogeneous graphene could be formed in the FET channel and a W-shaped transfer curve was obtained with dual-gated GFET.

Dynamic response of the device

Figure 5 shows the measured AC performances of our dual-gated GFET based frequency quadrupler. In the AC measurements, the VTGS was set at −8 V and the Vds was set to 1 V. The capacitor C from a bias tee was used to block the DC signal from the output Vout. A 200 kHz sinusoidal input (VBGS ranges from −22 V to −2 V) was applied to the BG to initiate the frequency quadrupling. In principle, a pure frequency quadrupler (nearly 100% spectrum purity) can be achieved when two symmetric conductance minima arise in the operation area simultaneously, which is sketchily shown in Fig. 1c. In other words, a higher symmetrical factor in the working area can result in a higher output power of the fourth harmonic. The relative output RF power spectrum is obtained through the Fourier transform of the output real time RF signals. With these data, it is found that about 50% of the output RF power is concentrated at the desired 800 kHz. Compared with the useful frequency, these undesired output frequency components (about 25% at the fundamental frequency, about 12% at the second harmonic and about 12% at the third harmonic) play a minor role. In order to investigate the RF conversion efficiency of the frequency quadrupler, the RF input power was obtained. As the total capacitance of the dual-gated GFET is about 18 pF, the total RF input power is about 1.7 mW. The quadrupled output power is 2.4 μW, which means that a RF conversion efficiency of 0.14% is achieved in this frequency quadrupler. Relative low RF power conversion efficiency is attributed to the large parasitic capacitance of the fabricated GFET. Here, noticeably for the first time a GFET based frequency quadrupler is reported. Moreover, the simple dual-gated GFET based frequency quadruplers provide perfect illustration of versatility of graphene material once again.

A frequency multiplier with simple structure and tunable multiplication factor may have lots of superiorities for RF electronic applications due to low cost and high integration. In our case, dual-gated GFET can also work as high performance frequency doublers or frequency triplers with a suitable operation area. Figure 6a shows relative output RF power spectrum of working dual-gated GFETs as frequency doublers (VTGS = −6 V and VBGS ranged from −10 V to −2 V) and about 78% of output RF power is concentrated at useful 400 kHz, with an input of 200 kHz. Figure 6b presents AC performances of working dual-gated GFETs as frequency triplers, where VTGS was set to −8 V and VBGS swept from −15 V to −1 V. About 79% of total RF power is concentrated at 600 kHz with 200 kHz input. Therefore, dual-gated GFET can work as high performance frequency doublers, frequency triplers and frequency quadruplers by choosing suitable operation areas. This is the first time that a multi-mode frequency multiplier is reported.

With potential ultrahigh carrier mobility and high saturation velocity, graphene can response to high frequency signals completely. Hence large RC time constant of the device structure is major obstacle to improvement of operation bandwidth of graphene based device. Therefore, performance of graphene based devices can be enhanced significantly if an optimized fabrication process is carried out to decrease both parasitic capacitance and output resistance. More clearly, in order to decrease the parasitic capacitance of the GFET-based frequency quadrupler, a highly resistive substrate such as quartz assisting with a local BG technique is preferred. On the other hand, both contact resistance and channel resistance make contribution to output resistance of GFET. A polymeric residue-free graphene fabrication process50 can be carried out to reduce contact resistance. Channel resistance can be decreased by fabricating GFET with nanoscale channel length and large W/L ratio. In order to investigate limitation of operation frequency of dual-gated GFET-based frequency quadrupler, a developed device structure is designed and proposed. The channel width and length of newly designed GFET are 10 μm and 1 μm, respectively. A local BG with width of 1 μm is located at the bottom of the channel. A SiO2 gate dielectric layer with thickness of 90 nm is formed between BG and the graphene channel. With this structure, time constant of about 1.74 ps (R of about 200 Ω and C of about 8.7 fF) can be obtained, indicating cut-off frequency of about 92 GHz and 368 GHz generated output signal. Under a 1 V bias voltage, required carrier mobility of graphene is only 3680 cm2/Vs, which can be achieved easily due to ultrahigh intrinsic carrier mobility of graphene material. Hence graphene-based frequency quadruplers have great potential to generate ultrahigh frequency signals and could find its roles easily in ultrahigh frequency electronic applications in near future.

Here, we summarize potential superiorities that dual-gated GFET offers as a new device for RF applications.

-

A multi-mode frequency multiplier. The zero band gap of graphene enables tunable electronic transport polarity. In this work, a narrow top gate was utilized to dope underneath graphene with electrostatic field, and a tunable transfer curve was achieved with one GFET. With the tunable transfer curve, GFET can work as high performance frequency doubler, frequency tripler and frequency quadrupler.

-

High multiplication factor. Without any additional filter system, it is impossible to achieve a frequency multiplier with high multiplication factor by using traditional nonlinear electronic devices because output power of the high-order harmonic is much smaller than the low-order harmonic. In this work, a graphene based frequency quadrupler with about 50% power purity was realized with dual-gated GFET. Developing idea proposed in this work, a frequency multiplier with multiplication factor of 2 * N (N > 2) can be realized by fabricating N-1 top gates in the GFET channel. With superhigh carrier mobility of graphene, this graphene-based frequency multiplier will play an important role in the ultrahigh-frequency electronic applications, such as signal generator for THz.

-

Low cost. The cost-effective high performance CVD graphene material can be available with rapid improvement of the synthetic technology. Simplicity of the GFET structure results in low fabrication cost. Furthermore, the demand of this multi-mode frequency multiplier increasing rapidly as communications would become indispensable nowadays.

Conclusion

In summary, a novel dual-gated GFET based high performance frequency quadrupler is presented. Benefit from electrostatic doping effect of the narrow TG to the underneath graphene, a W-shaped transfer curve was obtained with only one GFET. With this new type nonlinear I-V feature, a graphene-based frequency quadrupler was achieved. This device can also operate as high performance frequency doublers and frequency triplers. To the best of our knowledge, it is the first reported multi-mode graphene based frequency multiplier in the world. The potential ultrahigh carrier mobility of the graphene, together with simplicity of the device structure and CMOS compatible fabrication processes makes the dual-gated GFET based frequency quadrupler one of the most captivating candidates for future ultrahigh-frequency electronics, especially RF applications.

Methods

We characterized the fabricated device at room temperature in ambient conditions. The DC characteristics of the dual-gated GFET were measured by a Keithley 1602B semiconductor analyzer. Both Agilent 33250A signal generator and Agilent MSO-X 3034A mixed signal oscilloscope were used to obtain AC characteristics of the graphene based frequency quadrupler.

Additional Information

How to cite this article: Cheng, C. et al. A graphene based frequency quadrupler. Sci. Rep. 7, 46605; doi: 10.1038/srep46605 (2017).

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

References

Raisanen, A. V. Frequency multipliers for millimeter and submillimeter wavelengths. Proc. IEEE 80, 1842–1852 (1992).

Riley, J. R. & Smith, A. D. Design considerations for an harmonic radar to investigate the flight of insects at low altitude. Comput. Electron. Agricult. 35, 151–169 (2002).

Chien, G. & Gray, P. R. A 900-MHz local oscillator using a DLL-based frequency multiplier technique for PCS applications. IEEE J. Solid-State Circuits 35, 1996–1999 (2001).

Bao, M. Q., Kozhuharov, R., Chen, J. J. & Zirath, H. A D-band keyable high efficiency frequency quadrupler. IEEE Microw. Wireless Compon. Lett. 24, 793–795 (2014).

Chen, G. Y. et al. Design and analysis of Ka -band monolithic high-efficiency frequency quadrupler using GaAs HBT–HEMT common-base/common-source balanced topology. IEEE Trans. Microw. Theory Tech. 61, 3674–3689 (2013).

Abbasi, M. & Ricketts, D. S. 275–285 GHz balanced frequency quadrupler chain in 45 nm SOI CMOS. Electron. Lett. 51, 1424–1425 (2015).

Novoselov, K. S. et al. Electric field effect in atomically thin carbon films. Science 306, 666–669 (2004).

Bolotin, K. I. et al. Ultrahigh electron mobility in suspended graphene. Solid State Commun. 146. 351–355 (2008).

Nair, R. R. et al. Fine structure constant defines visual transparency of graphene. Science 320, 1308 (2008).

Wang, F. et al. Gate-variable optical transitions in graphene. Science 320, 206–209 (2008).

Lee, C. G., Wei, X. D., Kysar, J. W. & Hone, J. Measurement of the elastic properties and intrinsic strength of monolayer graphene. Science 321, 385–388 (2008).

Balandin, A. A. et al. Superior thermal conductivity of single-layer graphene. Nano Lett. 8, 902–907 (2008).

Schwierz, F. Graphene transistors. Nat. nanotech. 5, 487–496 (2010).

Lv, H. M. et al. Inverted process for graphene integrated circuits fabrication. Nanoscale 6, 5826–5830 (2014).

Han, S. J., Garcia, A. V., Oida, S., K. Jenkins, A. & Haensch, W. Graphene radio frequency receiver integrated circuit. Nat. Commun. 5, 3086–3091 (2014).

Lin, Y. M. et al. Wafer-scale graphene integrated circuit. Science 332, 1294–1297 (2011).

Yeh, C. H. et al. Gigahertz flexible graphene transistors for microwave integrated circuits. ACS Nano 8, 7663–7670 (2014).

Tao, L. Q. et al. Fabrication techniques and applications of flexible graphene-based electronic devices. J. Semicond. 37, 041001 (2016).

Kim, K. S. et al. Large-scale pattern growth of graphene films for stretchable transparent electrodes. Nature 457, 706–710 (2009).

Shao, Y. Y. et al. Graphene based electrochemical sensors and biosensors: a review. Electroanalysis 22, 1027–1036 (2010).

Fu, W. Y. et al. Electrolyte-gated graphene ambipolar frequency multipliers for biochemical sensing. Nano Lett. 16, 2295–2300 (2016).

Lee, H. et al. A graphene-based electrochemical device with thermoresponsive microneedles for diabetes monitoring and therapy. Nat. Nanotech. 11, 566–574 (2016).

Smith, A. D. et al. Resistive graphene humidity sensors with rapid and direct electrical readout. Nanoscale 7, 19099–19109 (2015).

Wang, H., Nezich, D., Kong, J. & Palacios, T. Graphene frequency multipliers. IEEE Electron Device Lett. 30, 547–549 (2009).

Ramón, M. E. et al. Three-gigahertz graphene frequency doubler on quartz operating beyond the transit frequency. IEEE Trans. Nanotechnol. 11, 877–883 (2012).

Chen, H. Y. & Appenzeller, J. Graphene-based frequency tripler. Nano Lett. 12, 2067–2070 (2012).

Wang, H., Hsu, A., Wu, J., Kong, J. & Palacios, T. Graphene-based ambipolar RF mixers. IEEE Electron Device Lett. 31, 906–908 (2010).

Habibpour, O., Cherednichenko, S., Vukusic, J., Yhland, K. & Stake, J. A subharmonic graphene FET mixer. IEEE Electron Device Lett. 33, 71–73 (2012).

Habibpour, O. et al. Graphene FET gigabit ON–OFF keying demodulator at 96 GHz. IEEE Electron Device Lett. 37, 333–336 (2016).

McClure, J. W. Band structure of graphite and de Haas-van alphen effect. Phys. Rev. 108, 612–618 (1957).

Neto, A. H. C., Guinea, F., Peres, N. M. R., Novoselov, K. S. & Geim, A. K. The electronic properties of graphene. Rev. Mod. Phys. 81, 109–162 (2009).

Wang, Z. et al. A high performance top-gate graphene field-effect transistor based frequency doubler. Appl. Phys. Lett. 96, 173104 (2010).

Cheng, C. T. et al. A pure frequency tripler based on CVD graphene. IEEE Electron Device Lett. 37, 785–788 (2016).

Kim, S. et al. Realization of a high mobility dual-gated graphene field-effect transistor with Al2O3 dielectric. Appl. Phy. Lett. 94, 062107 (2009).

Russo, S., Craciun, M. F., Yamamoto, M., Morpurgo, A. F. & Tarucha, S. Contact resistance in graphene-based devices. Physica E 42, 677–679 (2010).

Martin, J. et al. Observation of electron–hole puddles in graphene using a scanning single-electron transistor. Nat. Phys. 4, 144–148 (2008).

Feng, T. T. et al. Back-gate graphene field-effect transistors with double conductance minima. Carbon 79, 363–368 (2014).

Cheianov, V. V., Fal’ko, V. & Altshuler, B. L. The focusing of electron flow and a Veselago lens in graphene p-n junctions. Science 315, 1252–1255 (2007).

Stander, N., Huard, B. & Gordon, D. G. Evidence for klein tunneling in graphene p-n junctions. Phys. Rev. Lett. 102, 026807 (2009).

Liu, N. et al. Large-area, transparent, and flexible infrared photodetector fabricated using P-N junctions formed by N-doping chemical vapor deposition grown graphene. Nano Lett. 14, 3702–3708 (2014).

Lemme, M. C. et al. Gate-activated photoresponse in a graphene p-n junction. Nano Lett. 11, 4134–4137 (2011).

Özyilmaz, B. et al. Electronic transport and quantum Hall effect in bipolar graphene p-n-p junctions. Phys. Rev. Lett. 99, 166804 (2007).

Choi, J. H. et al. Complete gate control of supercurrent in graphene p-n junctions. Nat. Commun. 4, 2525–2534 (2013).

Lohmann, T., Klitzing, K. V. & Smet, J. H. Four-terminal magneto-transport in graphene pn junctions created by spatially selective doping. Nano Lett. 9, 1973–1979 (2009).

Kim, S. et al. Graphene p–n vertical tunneling diodes. ACS Nano 7, 5168–5174 (2013).

Chiu, H. Y., Perebeinos, V., Lin, Y. M. & Avouris, P. Controllable p-n junction formation in monolayer graphene using electrostatic substrate engineering. Nano Lett. 10, 4634–4639 (2010).

Seo, B. H., Youn, J. M. & Shim, M. Direct laser writing of air-stable p-n junctions in graphene. ACS Nano 8, 8831–8836 (2014).

Ju, L. et al. Photoinduced doping in heterostructures of graphene and boron nitride. Nat. Nanotechnol. 9, 348–352 (2014).

Chaisakul, P. et al. Integrated germanium optical interconnects on silicon substrates. Nat. Photon. 8, 482–488 (2014).

Wu, Y . et al. 200 GHz maximum oscillation frequency in CVD graphene radio frequency transistors. ACS Appl. Mater. Interfaces 8, 25645–25649 (2016).

Acknowledgements

The authors are grateful for the financial support from the National Key Research and Development Program of China (Grant No. 2016YFB0402505, 2016YFA0202201), the financial support from the National Basic Research Program of China (Grant No. 2015CB352100), the Natural Science Foundation of China (Grant Nos 61675191, 61178051, 61335010, 61321063, 11404239, 61275169, 61227807, 61575108, 61504093) and the Opened Fund of the State Key Laboratory on Integrated Optoelectronics (No. IOSKL2015KF07, IOSKL2014KF15). We appreciate Assistant Professor Hongmei Chen from Chinese Academy of Sciences for carefully revising this manuscript.

Author information

Authors and Affiliations

Contributions

B.J.H., P.X. and H.D.C. designed the experiment. C.T.C. and B.J.H. performed device fabrication. C.T.C. and B.J.H. performed the device measurements. C.T.C., X.R.M., Z.Z., Z.Y.Z. and Z.X.G. analyzed the data. C.T.C. wrote the paper. H.D.C. supervised the project. All authors discussed the results and commented on the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Cheng, C., Huang, B., Mao, X. et al. A graphene based frequency quadrupler. Sci Rep 7, 46605 (2017). https://doi.org/10.1038/srep46605

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep46605

- Springer Nature Limited

This article is cited by

-

Reconfigurable frequency multipliers based on graphene field-effect transistors

Discover Nano (2023)

-

Electronics based on two-dimensional materials: Status and outlook

Nano Research (2021)

-

Crack-and-Fold Style Defects in CVD Graphene on Raw Cu Foils

Journal of Electronic Materials (2020)

-

Design and Simulation of a Frequency Doubler Using Graphene Nanoribbon Field Effect Transistors for Communication Devices

Journal of Electronic Materials (2019)