Abstract

The fabrication of vertically stacked SiGe nanosheet (NS) field-effect transistors (FETs) was demonstrated in this study. The key process technologies involved in this device fabrication are low pressure chemical vapor deposition SiGe/Si multilayer epitaxy, selective etching of Si layers over SiGe layers using tetramethyl-ammonium-hydroxide wet solution, and atomic layer deposition of Y2O3 gate dielectric. For the fabricated stacked SiGe NS p-GAAFETs with a gate length of 90 nm, ION/IOFF ratio of around 5.0 × 105 and subthreshold swing of 75 mV/dec were confirmed via electrical measurements. Moreover, owing to its high quality of Y2O3 gate dielectric, the device showed a very small drain-induced barrier-lowering phenomenon. These designs can improve the gate controllability of channel and device characteristics.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Introduction

In response to market demands, CMOS technologies continuously aim to scale down the device dimension as much as possible. Nevertheless, miniature Si metal–oxide–semiconductor field-effect transistors (MOSFETs) have encountered many fundamental physical limits; the accompanying difficulties in either developing required process technology or enhancing device performance are also increased. Simply shrinking the channel length and/or the dielectric thickness can no longer realize the excellent switching ratio, high driving capability, low leakage current, and acceptable reliability. Compared to pure Ge channel FET, SiGe channel FETs will be most likely utilized beyond 3-nm technology node because of the absence of dislocations resulting from the smaller lattice mismatch with Si1. Thus, rapid development in SiGe technologies is warranted, and relevant studies in this field are needed2,3,4,5,6,7,8,9,10,11,12,13.

Many reports regarding the stacked channel FETs have been published. However, few studies have reported on the stacked SiGe channel FETs. The main reason behind this is that selective etching of Si over SiGe is a difficult process. In this work, we fabricated vertically stacked SiGe nanosheet (NS) FET devices on cost-effective traditional Si substrates by selective etching of Si in SiGe/Si/SiGe stack structures using wet tetramethyl-ammonium-hydroxide (TMAH) solution to form stacked SiGe NS channels. The fabrication process exhibits various advantages. (1) isotropic etching without ion bombardment with extremely high Si to SiGe selective etching rate ratio; (2) better control of the composition, thickness, and spacing of SiGe channel materials; (3) low process complexity, which is in line with standard process and mass production. These advanced designs can improve the gate controllability of channel and device characteristics. As the semiconductor-related field gradually enters its physical limitations, Si/SiGe/Si/SiGe epitaxial multi-layer combined with selective etching is considered as the most likely implementation of the vertically stacked SiGe14,15.

In this work, selective etching of Si over SiGe was systematically studied and a complete process-flow for the formation of vertically stacked SiGe channels was developed. Recently, highly selective etchants were demonstrated in our group1, which enabled the fabrication of SiGe NS using a wet-etching approach. After selective etching, optimization was done to achieve high-k gate oxide solutions on p-FET channels and obtain an applicable interface quality for demonstration.

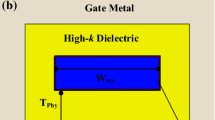

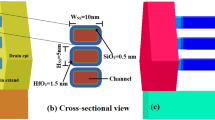

Device fabrication

The fabrication procedure of two stacked p-type SiGe NS gate-all-around field-effect transistor (p-GAA FETs) is illustrated in Fig. 1. Two periods of Si0.8Ge0.2 (60 nm)/Si (25 nm) layers were epitaxially grown on 200 mm SOI (100) substrate with a top Si thickness of 40 nm and a buried oxide thickness of 150 nm by low pressure chemical vapor deposition (LPCVD) using Dichlorosilane and GeH4 gases. The GeH4 and DCS flow rates were set to 25 and 130 sccm, respectively. When only Si layer was grown, the GeH4 was switched to vent mode (that is, GeH4 bypassed the chamber). The growth temperature and pressure were kept at 700 °C and 20 torr for all layers. A specific SiGe/Si epitaxy was employed to stack NS channels, with Si being used as a sacrificial layer that defines the suspension thickness between the channels. Figure 2 shows the transmission electron microscopy (TEM) cross-sectional images of the SiGe/Si multilayer epitaxy. The alternative layer thickness was well-controlled giving precise film thickness. X-ray diffraction (XRD) rocking curve analysis and reciprocal space mapping (RSM) in Fig. 3 show that the SiGe layers in the stacking SiGe/Si multilayers are fully strained, implying that the SiGe layers are not relaxed, and therefore no dislocations are generated. This results can also be supported by TEM images in Fig. 2. After LPCVD epitaxy, the active region of the device was defined by electron-beam lithography. Subsequently, the active region was isolated by etching Si0.8Ge0.2/Si stacked layers down to the BOX layer using Cl2/HBr-related etching process. The fabricated fin structures in the central area of the active region have a width of ~ 100 nm. After the fin formation, we used TMAH solution (2.38% in H2O) to selectively etch away Si layers and keep Si0.8Ge0.2 layers. To achieve a good selective etching between Si0.8Ge0.2/Si, megasonic agitation was used with the TMAH solution at approximately 60 °C. Figure 4 shows the stacked Si0.8Ge0.2 NS structures after selective etching. As shown in Fig. 4a, the stacked Si0.8Ge0.2 NS with a nanosheet width (WNS) of ~ 100 nm is released. The N2 blow drying process on the sample after wet-etching must be performed cautiously. Strong N2 blowing would lead to the issue of NS bending (see Fig. 4b). The resultant NS thickness is greater than 30 nm, and it is possible to obtain a thinner NS and higher WNS with further optimization. Subsequently, the 3 nm high-k dielectric Y2O3 gate dielectric was deposited by atomic layer deposition (ALD) and TiN gate metal layer was deposited by PVD sputtering with a thickness of 75 nm. The deposited thickness of TiN on the sidewall was ~ 60 nm. After gate patterning, the S/D regions were formed by ion-implanted using 11B ions for SiGe nanosheets p-FET (1 × 1015 cm−2 at 10 keV). Activation was accomplished by annealing at 900 ℃ for 30 s. A simplified process flow with selected cross-sectional SEM pictures from critical steps is shown in Fig. 5.

Simplified process sequence with selected cross-sectional SEM pictures from critical steps: (a) Key process flow of Si0.8Ge0.2 nanosheets p-FET fabrication; (b) a fin formation for channel and S/D extension regions; (c) stacked Si0.8Ge0.2 nanosheet structures formation by megasonic-agitation-assisted TMAH selective etching at 60 °C; (d) conformal depositions of Y2O3/TiN as gate dielectric and metal; (e) top view SEM image of a finished device.

Results

In our previous work, we had reported SiGe MOS interfacial properties using a gate stack of Y2O3 with ten cycles of TMA pre-treatment. The scalability of EOT via reduction in film thickness of Y2O3 and its effects on the properties of Si0.8Ge0.2 MOS interfaces still remained unclear16,17. In this work, the feasibility of EOT scaling in TiN/Y2O3 gate stacks with TMA treatment was examined. Figure 6a shows the capacitance–voltage (C–V) measurement on a control TiN/Y2O3/p-Si0.8Ge0.2 MOS capacitor, which was fabricated using the same ALD Y2O3 process as the device. The C–V curves of Si0.8Ge0.2 MOS devices exhibit only 3% frequency dispersion between 1 kHz and 1 MHz in the accumulation region at room temperature, indicating that the bulk Y2O3 was of high quality. Preliminary results on TiN/Y2O3/p-Si0.8Ge0.2 structures that underwent forming gas annealing indicate a decrease in the calculated equivalent thickness (CET), implying that ALD Y2O3 is a promising gate dielectric. Based on the measured C–V curves, the calculated equivalent thickness is ~ 1.5 nm. To characterize Y2O3 film properties and the depth profiles of each element, high resolution transmission electron microscopy (HRTEM) was performed. The TEM images and depth profiles from TiN/Y2O3 with TMA treatment are shown in Fig. 6b. A thinner interfacial layer was observed between Y2O3 and SiGe showing an amorphous characteristic. This suggests an amorphous nature of interface layers (ILs), making the crystallization of ultrathin Y2O3 films difficult. However, C–V characteristics indicated sufficient performance of this gate stack for further device fabrication.

Finally, ID–VGS and ID–VDS curves for the nanosheets p-FETs are shown in Fig. 7a and b, respectively. In Fig. 7b, the gate overdrive voltage VOV sweeps from 0 to 1.0 V with steps of 0.25 V. The normalized current (per footprint width of SiGe nanosheets) at VOV = − 0.5 V and VDS = − 1.0 V is approximately 790 μA/μm. The ION/IOFF ratios for the p-GAAFETs are approximately 1 × 106. These devices show negligible drain-induced barrier lowering effects, indicating that the electrostatic control of the all-around gates on the stacked Si0.8Ge0.2-NS channels is excellent. The subthreshold swings (SS) are approximately 70 mV/dec. Table 1 shows a comparison of Si0.8Ge0.2 stacked NS GAAFETs in this study with other GAAFETs that use different stacked channels.

We found there would be a remaining Si parasitic channel underneath the Si0.8Ge0.2 NS and the shape of SiGe nanosheet would distort if the process of selective wet etching of Si sacrificial layers is not optimized (see Fig. 8), for instance, the temperature of TMAH solution is lower than 60 °C and concentration is less than 2.38%. The electrical measurement in Fig. 8b shows this parasitic Si channel influences the overall device performance by showing worse SS characteristic. Besides, the irregular shape of Si0.8Ge0.2 channel was observed to give relatively less overall perimeter compared to the rectangle nanosheet structure. Consequently, this will reduce the Ion current of the device.

Conclusion

This study demonstrates the stacked Si0.8Ge0.2 NS p-FETs using Si/SiGe multilayers. Selective etching of Si over SiGe processes was successfully developed to obtain the Si0.8Ge0.2 nanosheets. The stacked SiGe NS GAAFETs have the potential to fulfill the requirement for the 3 nm technology node and beyond. Future studies will focus on further optimization of its performance terms of etch-selectivity and Ion current. The technique demonstrated in this study has a significant potential to boost the p-FET device performance for the next generation of CMOS logic in GAA NS technology.

Methods

Si-on-insulator (SOI) wafers with a 40 nm thick Si top layer (p-type, 9–18 Ω cm) were employed as the substrates. The wafers were cleaned using the RCA standard cleaning methods for removing organic materials, certain metals, and particles from the Si substrates; the wafers were subsequently rinsed in deionized water and dried in N2 gas. Four alternative layer stacking of SiGe (60 nm) and Si (25 nm) were epitaxially grown on SOI (100) wafer with a 40 nm Si top seed layer. GeH4 and DCS gases were used to build the layer using an ASM Epsilon 2000 + low-pressure CVD machine. The growth temperature for the SiGe and Si layer was 700 °C. The growth pressure in chamber was kept at 20 torr. Electron-beam lithography and dry etching with Cl2/HBr were utilized to define and form the active device area, respectively. TMAH solution at 60 °C was used to remove Si interlayers selectively and form the stacked SiGe nanosheets. The gate dielectrics Y2O3 were formed by ALD18. The gate metal TiN was deposited by PVD sputtering.

References

Chu, C. L. et al. Stacked Ge-nanosheet GAAFETs fabricated by Ge/Si multilayer epitaxy. IEEE Electron Device Lett. 39, 1133–1136. https://doi.org/10.1109/LED.2018.2850366 (2018).

Chang, W. H., Ota, W. H. & Maeda, T. Gate-first high-performance germanium nMOSFET and pMOSFET using low thermal budget ion implantation after germanidation technique. IEEE Electron Device Lett. 37, 253–256. https://doi.org/10.1109/LED.2016.2523518 (2016).

van Dal, M. J. H. et al. Ge CMOS gate stack and contact development for vertically stacked lateral nanowire FETs. In IEDM 21.1.1–21.1.4 (San Francisco, CA, USA, 2019). https://doi.org/10.1109/IEDM.2018.8614577.

Ritenour, A., Hennessy, J. & Antonidis, D. A. Investigation of carrier transport in germanium MOSFETs with WN/Al2O3/AlN gate stacks. IEEE Electron Device Lett. 28, 746–749. https://doi.org/10.1109/LED.2007.901272 (2007).

Seo K.-I. et al. A 10nm platform technology for low power and high performance application featuring FINFET devices with multi workfunction gate stack on bulk and SOI. In Dig. Tech. Pap. - Symp. VLSI Technol. 1–2 (Honolulu, HI, USA, 2014). https://doi.org/10.1109/VLSIT.2014.6894342.

Guo, D. et al. FINFET technology featuring high mobility SiGe channel for 10nm and beyond. In Dig. Tech. Pap. - Symp. VLSI Technol. 1–2 (Honolulu, HI, USA, 2016). https://doi.org/10.1109/VLSIT.2016.7573360.

Fischetti, M. V. & Laux, S. E. Band structure, deformation potentials, and carrier mobility in strained Si Ge, and SiGe alloys. J. Appl. Phys. 80, 2234–2252. https://doi.org/10.1063/1.363052 (1996).

Jeong, C. et al. Physical understanding of alloy scattering in SiGe channel for high-performance strained pFETs. In IEDM 2–5 (Washington, DC, USA, 2013). https://doi.org/10.1109/IEDM.2013.6724614.

Capogreco, E. et al. First demonstration of vertically stacked gate-all-around highly strained germanium nanowire pFETs. IEEE Trans. Electron Devices 65, 5145–5150. https://doi.org/10.1109/TED.2018.2871595 (2018).

Mitard, J. et al. An in-depth study of high-performing strained germanium nanowires pFETs. In Dig. Tech. Pap. - Symp. VLSI Technol. 83–84 (Honolulu, HI, USA, 2018). https://doi.org/10.1109/VLSIT.2018.8510666.

Capogreco, E. et al. High performance strained germanium gate all around p-channel devices with excellent electrostatic control for sub-Jtlnm LG. In Dig. Tech. Pap. - Symp. VLSI Technol. T94–T95 (Kyoto, Japan, 2019). https://doi.org/10.23919/VLSIT.2019.8776558.

Lee, T.-E., Kato, K., Ke, M., Takenaka, M. & Takagi, S. Improvement of SiGe MOS interface properties with a wide range of Ge contents by using TiN/Y2O3 gate stacks with TMA nassivation. In Dig. Tech. Pap. - Symp. VLSI Technol. T100–T101 (Kyoto, Japan, 2019). https://doi.org/10.23919/VLSIT.2019.8776523.

Loubet, N. et al. T17–5 (late news) stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET T230 T231. VLSI Technol. 5, 14–15 (2017).

Bera, L. K. et al. Three dimensionally stacked SiGe nanowire array and gate-all-around p-MOSFETs. In IEDM 1–4 (San Francisco, 2006). https://doi.org/10.1109/IEDM.2006.346841.

Mochizuki, S. et al. Stacked gate-all-around nanosheet pFET with highly compressive strained Si1-xGexchannel. In IEDM 2.3.1–2.3.4 (San Francisco, 2020). https://doi.org/10.1109/IEDM13553.2020.9372041.

Lee, T. E., Ke, M., Toprasertpong, K., Takenaka, M. & Takagi, S. Reduction of MOS interface defects in TiN/Y2O3/Si0.78Ge0.22 structures by trimethylaluminum treatment. IEEE Trans. Electron Devices 67, 4067–4072. https://doi.org/10.1109/TED.2020.3014563 (2020).

Lee, T.-E., Toprasertpong, K., Takenaka, M. & Takagi, S. Impacts of equivalent oxide thickness scaling of TiN/Y2O3 gate stacks with trimethylaluminum treatment on SiGe MOS interface properties. IEEE Electron Device Lett. 42, 966–969. https://doi.org/10.1109/LED.2021.3081513 (2021).

Chu, C. L. et al. Ge/Si multilayer epitaxy and removal of dislocations from Ge-nanosheet-channel MOSFETs. Sci. Rep. 12, 959. https://doi.org/10.1038/s41598-021-04514-y (2022).

Author information

Authors and Affiliations

Contributions

C.L.C. for experiment performing and manuscript drafting; S.H.H. for manuscript editing; S.H.C. for manuscript drafting; W.Y.C. for figure illustration; G.L.L. for project ownership and planning.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Chu, CL., Hsu, SH., Chang, WY. et al. Stacked SiGe nanosheets p-FET for Sub-3 nm logic applications. Sci Rep 13, 9433 (2023). https://doi.org/10.1038/s41598-023-36614-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-023-36614-2

- Springer Nature Limited