Abstract

Silicon spin qubits are promising candidates for scalable quantum computers, due to their coherence and compatibility with CMOS technology. Advanced industrial processes ensure wafer-scale uniformity and high device yield, but traditional transistor processes cannot be directly transferred to qubit structures. To leverage the micro-electronics industry expertise, we customize a 300 mm wafer fabrication line for silicon MOS qubit integration. With careful optimization of the gate stack, we report uniform quantum dot operation at the Si/SiO2 interface at mK temperature. We measure a record-low average noise with a value of 0.61 \({\rm{\mu }}{\rm{eVH}}{{\rm{z}}}^{-0.5}\) at 1 Hz and even below 0.1 \({\rm{\mu }}{\rm{eVH}}{{\rm{z}}}^{-0.5}\) for some operating conditions. Statistical analysis of the charge noise measurements show that the noise source can be described by a two-level fluctuator model. This reproducible low noise level, in combination with uniform operation of our quantum dots, marks CMOS manufactured spin qubits as a mature platform towards scalable high-fidelity qubits.

Similar content being viewed by others

Explore related subjects

Find the latest articles, discoveries, and news in related topics.Introduction

The demand for greater computational power has put quantum computation in the limelight: the concept of using quantum states for information processing promises a huge speedup and solutions to certain problems that are intractable on classical computers1. In the past decades, quantum computing has shown marked development, with small-scale quantum algorithms and quantum advantage achieved on different platforms2,3,4. In moving towards practical quantum computing applications, the research focus is shifting from fundamental qubit operation to large qubit systems5. Particularly, qubits fabricated with industrial semiconductor manufacturing technologies recently received great attention6,7,8. The capability of the semiconductor industry in fabricating billions of nanostructures with remarkable uniformity and reliability could indeed be leveraged for the full integration of large-scale quantum processors9,10. The rationale here is that the first practical quantum algorithm would require the number of physical qubits to be in the million scale11, similar to the transistor count of integrated circuit chip transistors back in 1990s12.

Tantalizingly, the structure of silicon spin qubits closely resembles the CMOS transistor technology13. Nanoscale electrodes define the quantum dot structure trapping a single electron or a hole and its spin states encode the qubit14. With industrial fabrication, semiconductor nanostructures are patterned subtractively for accurate wafer-scale critical dimension control, where lithography defined patterns are transferred onto the gate electrodes by dry etching rather than the academic-style lift-off process15. Comprehensive metrology tools and close process monitoring steps ensure high reproducibility and yield. Moreover, the material science and characterization technology developed around the CMOS industry allow deep insight into the performance limiting factors and optimization directions. All this could provide spin qubits a shortcut for upscaling.

The spin state is also an excellent platform for quantum information encoding and processing16. By isotopically purifying the silicon substrate, long quantum coherence has been achieved17,18. Single and two qubit gates with operation fidelities higher than the error correction threshold have been demonstrated and efforts towards scaling have been shown with a six-qubit device18,19,20,21,22,23,24. In addition, spin qubits can be operated at elevated temperatures above 1 K, addressing several upscaling requirements on cooling power and wiring interconnect25,26,27. For the next step towards large qubit arrays, advanced semiconductor manufacturing is commonly expected to be needed to realize the architectures required for scaling up16,28,29. However, state-of-the-art spin qubits are mostly fabricated in laboratory-based environments18,19,20,21,22,23,24. Though there are several exciting demonstrations of qubits made by advanced industrial fabrication with good yield and transport uniformity, the final qubit performance typically shows a certain level of degradation over that of lab devices6,7,8. Device charge noise, which is one of the limiting factors for spin coherence and an important metric characterizing the device quality at cryogenic temperatures19,30,31,32,33,34, is typically high in fab devices with different materials and structures8,35,36,37.

To minimize the charge noise, it is important to understand its origin. The semiconductor/oxide interface has been identified as the source of charge noise and has been intensively studied over the last 40 years38. The McWhorter model is widely accepted in MOSFET devices39, it was first introduced to argue that noise in electrical devices is a consequence of an ensemble of defects each represented by a different switching time. In this model, defects in the oxide cause carrier number fluctuations in the MOSFET channel. However, in quantum devices it has been shown that charge noise is not a result of carrier number fluctuations38,40,41. Rather, defects at the Si/SiO2 interface or in the oxide, for these quantum devices, can be described as bistable systems known as two-level fluctuators (TLFs) that couple via the Coulomb interaction42. Each TLF has a unique Lorentzian spectrum. A random distribution of TLFs, all added together, results in the infamous \(1/f\) noise43. However, the microscopic nature of the TLFs remains inconclusive. While many different proposals have been employed to explain the origin of the TLFs including tunneling atoms or tunneling electrons40,41 it remains difficult to identify microscopic defects from typical measurements. Low noise devices with high quality interfaces could reveal individual TLFs and show their microscopic origin.

In this work, we customize a state-of-the-art 300 mm wafer fabrication flow for silicon MOS qubit structures7. Through full gate stack optimization, we demonstrate that the Si/SiO2 interface could provide low-noise environments for qubit operations rather than detrimental. Across multiple devices, all the quantum dot structures show stable and uniform operation at milli-Kelvin, and an average charge noise level of 0.6 \({\rm{\mu }}{\rm{eVH}}{{\rm{z}}}^{-0.5}\) at 1 Hz. This ultra-low noise level at different devices and operation conditions allows statistical analysis of the key metrics of the charge noise spectrum. With numerical simulations, we find that the charge noise can be well described with a simple TLF model and provide further insights into spatial density and position.

Results

Device fabrication and interface characterization

Industrial CMOS fabrication processes are used for our device fabrication7. We optimize the process flow for spin qubits, specifically for the planar overlapping gate scheme44. The overlapping structure has been the main design for high fidelity qubit operations18,20,22,23, and the integration with the standard industrial fabrication allows wafer-scale accurate critical dimension control and high device yield7,8,10,35. Additionally, the planar, gate-based quantum dot structure is compatible with large-scale qubit arrays16,28,29. We also employ 300 mm e-beam lithography for the pitch critical quantum dot gates and optical lithography for the size relaxed features. E-beam enables fast turnaround for device designs, and the process can be transferred to advanced optical lithography as similar photoresist and hardmask are used. The fabrication starts with a \(12\,{\rm{nm}}\) thermally grown oxide, which defines the high-quality Si/SiO2 interface for quantum dot confinement along the vertical direction. Following that, we deposit the first gate layer across the wafer and pattern it subtractively. Rather than metallic gates, we use polysilicon as the gate metal to reduce interface strain at cryogenic temperatures35,45. We then deposit an oxide of 7-8 nm of ALD SiO2. By repeating the above processes, we achieve the overlapping gates as shown in Fig. 1a.

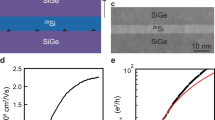

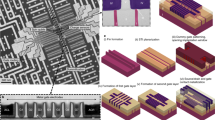

a Schematic of the subtractive patterning steps to fabricate the overlapping qubit structures. (i) A full sheet of gate material and photoresist are deposited through the 300 mm wafer. (ii) The photoresist is patterned with electron beam lithography. (iii) The 1st gate layer is patterned using dry etching techniques. (iv) For the 2nd gate layer, the steps start with deposition of ALD SiO2, 2nd gate layer, and photoresist. (v) Then the photoresist is patterned with e-beam, and (vi) transferred to the gate material with dry etching. (vii) Step iv-vi are repeated for the 3rd gate layer. The resulting scanning electron microscope (SEM) image of the qubit structure is shown in the bottom right. b Hall mobility (\(\mu\)) with respect to charge carrier density (\({n}_{S}\)) of the Si/SiO2 interface under different gate layers. The effect of multiple patterning steps is evident in the reduced mobility of higher gate layers (gate level 2 and 3, dashed lines). Through process optimization we show an improved mobility for gate level 2 and 3 (solid lines). c Hall mobility of gate level 1 at 10 mK, showing a peak mobility of \(30\times {10}^{3}{c}{m}^{2}{V}^{-1}{s}^{-1}\) and a percolation density of \(8\times {10}^{10}{c}{m}^{-2}\). d Quantum Hall effect of gate level 1 showing clear plateaus in the transverse resistance (\({R}_{{xy}}\)) and Shubnikov de Haas (SdH) oscillations in the longitudinal resistance (\({\rho }_{{xx}}\)). The SdH oscillations are visible starting \(B=0.5{T}\) and the oscillation minima go to zero at \(B=2{T}\), further indicating a high quality single subband transport channel.

However, subtractive patterning with dry etching can be more intrusive than academic-style metal lift-off processes46. This is further exacerbated for overlapping gate devices, in which each device is subjected to multiple etch steps35. The degraded dielectric and interface contribute to quantum dot non-uniformity and higher charge noise. To overcome this, we carefully optimize the process flow, and study the Si/SiO2 interface with cryogenic hall mobilities47, as shown in Fig. 1b (methods). In comparison to the first gate level, we find that the mobility drops considerably for higher gate layers. Nonetheless, the degradation is significantly reduced with optimized etching conditions, guaranteeing high quality structures for full qubit integration.

We perform further quantum transport measurements on the first gate layer, where the Si/SiO2 is protected by the gate from the following processing. The additional transport characterization allows us to compare the effect of implementing different process optimization steps, rather than different layer comparisons. The quality of the primary Si/SiO2 interface can be evaluated for a large-scale qubit array as well as for the implementation of the single-etch gating scheme48. With a base temperature lower than 10 mK, we can reach a peak mobility of \(30\times {10}^{3}\,{\rm{c}}{{\rm{m}}}^{2}{{\rm{V}}}^{-1}{{\rm{s}}}^{-1}\) at a charge density of \(4\times {10}^{11}\,{\rm{c}}{{\rm{m}}}^{-2}\) (Fig. 1c), which is significantly higher than previously reported Si MOS Hallbars with ~10 nm SiO2 gate oxide47,49. From a Metal-to-Insulator fit50 we determine a percolation density of \(8\times {10}^{10}\,{\rm{c}}{{\rm{m}}}^{-2}\). This matches the lowest values reported for MOS gate stacks47,49 and is comparable to SiGe heterostructures51. To gain further insight into the interface quality limiting factor, we operate the device in the quantum hall regime as shown in Fig. 1d and extract the Dingle ratio52 (see Supplementary Information section 1). The Dingle ratio is an indication of the spacing between the scattering centers to the conduction channel in 2D electron gas (2DEG) systems, with higher values mean larger spacing. We report a Dingle ratio \(\sim 3\), which is not as high as GaAs or SiGe heterointerfaces53,54 but larger than the typically number of ~1 on Si MOS samples47, suggesting that rather than defects directly at the Si/SiO2 interface, defects further away, either inside or on top of the oxide also play an important role in our optimized gate stack.

Electrical characterization of single quantum dots

For spin qubits, gate defined quantum dots are used to trap single spins14. Beyond the single spin regime, the quantum dots are commonly used as used as charge sensors to read out the spin states via different spin-to-charge conversion methods55,56,57. In this regime, only a single charge can flow through the quantum dot at any given time due to Coulomb repulsion, despite the presence of other charges inside the dot, and the current is very sensitive to the environmental electrical potential58. Such a structure is called a single electron transistor (SET).

As shown in Fig. 2a, the SET highly resembles a planar MOSFET transistor but with more gate electrodes59. The SET top gate (ST) induces an electron channel while the tunneling barrier gates (LB and RB) define the single quantum dot in between, which is a nanoscale electron island. Figure 2b shows the quantum dot charge stability map by measuring the SET current as a function of biases on LB and RB. The diagonal lines correspond to Coulomb oscillations where electrons tunnel through the quantum dot one by one58. Between the Coulomb oscillations, the electron numbers are fixed. From the barrier maps and regular Coulomb oscillations we observe that our system is gate defined and not defect driven.

a The SET device structure. The top is the SEM top view. The barrier gates have a critical dimension of 30 nm with a space of 60 nm. At the white dashed line, the schematic cross section is shown in the middle. The bottom shows the conduction band edge diagram, where the SET top gate (ST) forms the electron channel and the left and right barrier gates (LB and RB) induce the barriers above the Fermi level and define the quantum dot. b Barrier gate stability map at a fixed \({V}_{{\rm{ST}}}=3.5\,{\rm{V}}\). The single quantum dot between the barriers gives the diagonal Coulomb oscillation lines in the map (white dashed lines). c \({I}_{{\rm{D}}}{V}_{{\rm{G}}}\) characteristics of the top gate (blue lines) and barrier gates (green lines) across 12 SETs at 10 mK. d The cumulative distribution functions (CDF) of the threshold voltage (\({V}_{{\rm{TH}}}\)) and subthreshold swing (\({SS}\)) of the SET gates. The almost vertical lines, especially for the barrier gates, highlight the level of uniformity with advanced manufacturing techniques.

To study the SET uniformity in the milli-Kelvin temperature range, we measure the \({I}_{{\rm{D}}}{V}_{{\rm{G}}}\) characteristics by sweeping each gate individually while keeping the other two at a fixed high voltage potential. In other words, we operate the quantum dot as a conventional MOSFET transistor. In Fig. 2c, we show the average \({I}_{{\rm{D}}}{V}_{{\rm{G}}}\) characteristics of 12 devices (12 ST gates and 24 barrier gates). Furthermore, we extract the threshold voltage and sub-threshold swing at standard maximum transconductance point (methods). The devices show remarkable uniformity as seen in the cumulative distribution functions plots in Fig. 2b, with a standard deviation ~70 mV for the barrier threshold voltage and < 20% (5 mV dec−1) for the sub-threshold swing. We note that above SET studies focus on single quantum dots in the many-electron regime, while large qubit arrays require many quantum dots in the last (or few) electron regime, and more studies are needed to address this challenge. Nonetheless, the statistical analysis on SETs in the mK range still highlights the uniformity with CMOS manufacturing and provides initial guidelines for the design of a large-scale spin qubit array8,60.

Charge noise

An electron spin in a (Silicon) quantum dot has long coherence as there is no direct coupling to charge fluctuations. By isotopically purifying the silicon substrate, recent studies show single spin dephasing times T2* beyond \(10\,{\rm{\mu }}{\rm{s}}\) and even \(100\,{\rm{\mu }}{\rm{s}}\)8,17,18,19,21,30. The remaining spin-orbit interaction (SOI), either intrinsic from the Si/SiO2 interface44 or extrinsic with micromagnet structure8,20,21,22,23,61, indirectly couples the spin to the environment’s electrical field noise. Many of the best reported spin qubits show that the device charge noise is in fact the limiting factor for the qubit coherence and the quantum gate fidelity19,30,62.

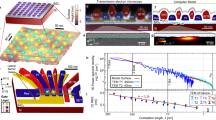

To study the device noise, we focus on the SET charge noise, measured in the many electron regime, as it has been shown to well represent the qubit noise30,31,32,63, and typically the noise figure at 1 Hz is used as the metric to benchmark between different structures and material platforms. On the flanks of the Coulomb peaks, where the SET is the most sensitive to environmental noise, we record the current noise spectrum. We extract the quantum dot potential fluctuation from this current noise with the device transconductance and capacitance ratio (methods), and the final charge noise spectral density is shown in Fig. 3a. This measurement is repeated on all Coulomb peaks ranging from VST = 3.5 V to 4.0 V, as shown in Fig. 3b. For statistical analysis, we perform the same procedure across 12 different devices, which gives 223 different spectra in total. In Fig. 3c, d, we show violin plots of the charge noise at 1 Hz (\({S}_{0}\)) and the power factor (\(\gamma\)) extracted from each noise measurement, respectively (see Supplementary Information section 3). The charge noise shows a standard deviation of 0.27 μe VHz-0.5 with the average of \(0.61\,{\rm{\mu }}{\rm{eVH}}{{\rm{z}}}^{-0.5}\) and several points lower than \(0.1\,{\rm{\mu }}{\rm{eV}}/\sqrt{{\rm{Hz}}}\). This is the state-of-the-art low charge noise for MOS devices8,34,35,36, and comparable to SiGe heterostructures30,31,33,54.

a Noise spectral density of the quantum dot. The resulting spectrum of the average of all \(223\) measurements showing a standard \(1/f\) spectrum (blue) showing a standard \(1/f\) spectrum. Spectral density of the charge noise in Coulomb blockade (orange) highlights that the background noise does not limit the measurements. The noise spectrum of one of the lowest charge noise spectra measured on Device H (red). b Coulomb oscillations of device A (black) by sweeping the ST bias. The charge noise at different peaks is overlayed. c, d The violine plot of \({S}_{0}\) and \(\gamma\) across 12 SETs and \(223\) peaks, with the mean value shown as a solid line.

On closer examination of each charge noise spectrum, we found that most have a power law dependence \(1/{f}^{\gamma }\), where \(\gamma\) is the power factor. This indicates a wide spatial distribution of TLFs but different frequency distributions as \(\gamma\) deviated from 1 slightly in some cases, which has also been recently observed in Si/SiGe quantum dots33. However, some spectra are Lorentzian in type36, or even the combination of a power law and Lorentzian, as seen in Fig. 4a. The Lorentzian noise spectrum suggests the presence of a single dominating TLF43, which can be expected given the random site of TLFs and the nanoscale quantum dots; for sufficiently low average densities of TLFs, statistical fluctuations in nanoscale devices are expected to result in some devices only observing a (few) dominant TLF(s).

a Charge noise spectra with power law (blue), Lorentzian (red), and combination of power law and Lorentzian (green). The Lorentzian spectrum can be observed when a single TLF dominates the charge noise spectrum. This is more likely to happen due to the random spatial distribution of TLFs and low overall TLF density. b Scatter plot of \({S}_{0}\) with respect to \({V}_{{ST}}.\) The different colors represent the shape of the spectra from (a). No correlation is observed suggesting negligible screening and uniform distribution of TLFs in energy. c Schematic depicting the types of defects in SiO2 (including dangling bonds, tunneling atoms, tunneling electrons and oxygen vacancies)38. The defects directly affect the electron wavefunction in the quantum dot. Right insert is the band diagram representation of the random TLF energy distribution in the oxide.

The nanoscale quantum dots together with the low charge noise spectra could therefore serve as an excellent probe for TLFs and their microscopic nature. In Fig. 4b, we plot each \({S}_{0}\) at the corresponding ST bias. Across an ST bias range from 3.5 to 4 V, we see a uniform distribution of \({S}_{0}\). In other words, as we change \({V}_{{ST}}\), different ensembles of TLFs are activated or deactivated randomly within the same frequency range, but the overall active number of TLFs at different electrical field is the same. We further examine the charge noise with respect to different metrics (see Supplementary Information section 3). No correlation between \({S}_{0}\) and \(\gamma\) is observed, suggesting that the TLFs are uniformly distributed in the examined frequency range due to the wide spread of the relaxation times. The exponent \(\gamma\) represents the distribution of TLFs in frequency. If the defects are distributed log-uniform in frequency, the expected \(\gamma\) is roughly 1. An increased (decreased) distribution in frequency or a dominating TLF could result in \(\gamma\, <\, 1\,\left(\gamma\, >\, 1\right)\)64. We find a wide distribution of \(\gamma\) between 0 and 2, suggesting the spectra dataset has a good coverage of TLFs with different switching times. In addition, varying the ST bias changes the number of electrons in the quantum dot, and we detect a systematic change in the quantum dot size and lever arm, which is the ratio of the ST-to-dot capacitance to the overall dot capacitance. As electrons in the quantum dot could partially screen the electrical field, varying the electron numbers could influence the charge noise pickup, especially in the few-electron regime33,65,66. But we do not identify a correlation between the charge noise and the lever arm suggesting that the screening effect is weak in our SET structures. Detailed statistical studies in the few electron regime is required for further insights. The above results suggest a uniform distribution of TLFs, which agrees with the standard TLF model43. Similar results have been reported with superconducting qubits38 from defects in the superconducting oxides, where most results are limited to fast TLFs in the radio frequency regime due to the nature of the microwave resonators in the qubits acting as a frequency filter. Albeit of different physical origin, our results suggest that near DC, i.e., nine frequency decades away, slow TLFs around 1 Hz are also uniformly distributed at the Si/SiO2 interface and/or in the oxide, as shown schematically in Fig. 4c.

Noise simulations

Our statistical measurements and analysis on the quantum dot charge noise suggests its microscopic origin: randomly distributed TLFs over a nanoscale device area. To further verify this postulation, we employ a simplified TLF model to reconstruct and validate the experiments. Following our previous study in ref. 64, we use double well potential (DWP, charge dipole) type defects to represent the TLFs as they best match the quantum dot charge noise Conversely, the full electron trapping/detrapping type of defect would lead to much larger noise distributions than what we observe in our data – as well as much larger than in previously published literature results8,33. We assume a two-dimensional distribution of TLFs in the silicon oxide, and only the TLF density (\({n}_{{\rm{TLF}}}\)) and its depth in the oxide (\(z\)) are tunable variables in the simulation. With the above conditions, TLFs are randomly placed over an area centered around a many-electron quantum dot. We perform a Monte Carlo simulation with \(1000\) random sets of TLF configurations and extract each noise spectrum of the quantum dot potential. Further details about the simulation can be found in Supplementary Information section 6.

Figure 5a shows the average noise at 1 Hz (\(\bar{{S}_{0}}\)) as a function of \({n}_{{\rm{TLF}}}\) and \(z\). In Fig. 5b, c, we plot the kernel density for the \(\gamma\) and \({S}_{0}\). Decreasing \({n}_{{TLF}}\) or reducing \(z\) increases the distribution of \({S}_{0}\) and \(\gamma\) around the averaged values, as the probability of finding a single dominating TLF increases. We find \({n}_{{TLF}}=1.6\times {10}^{10}\,{\rm{c}}{{\rm{m}}}^{-2}\) and \(z=6\,{\rm{nm}}\) to best represent the experimental distributions as shown in the overlaying distributions in Fig. 5d, e. The good simulation-to-experiment agreement on charge noise and power factor for both average values and distribution further supports that randomly distributed TLFs over the quantum dot lead to the device charge noise. In addition, we would like to point out that other combinations of \({n}_{{\rm{TLF}}}\) and \(z\) could still have reasonable match between simulation and experiments, and three-dimensional distribution of TLF could give a better matching than simple two-dimensional (Supplementary information section 6). Based on our simulations, we believe that advanced CMOS processing reduces disorder associated with the Si/SiO2 interface, and that defects within the oxide play an important role in this scenario. The Si/SiO2 interface does not need to be detrimental to quantum dot performance, and disorder at the interface, deep in the oxide, or even at the upper oxide/gate interface should be taken into consideration for further optimization67.

a Contour plot of the simulated quantum dot charge noise with respect to the TLF density (\({n}_{{\rm{TLF}}}\)) and the depth in the oxide (\(z\)). b, c The kernel distribution estimation of \(\gamma\), \({S}_{0}\) at different \({n}_{{\rm{TLF}}}\) generated from 1000 simulations. d, e The violin plots of \(\gamma\) and \({S}_{0}\) with experimental data with the mean value shown as a dotted line. Overlayed are the simulation results that best matches the experimental average and distribution (\({n}_{{TLF}}=1\times {10}^{10}\,{{\rm{cm}}}^{-2}\), \(z=6\,{\rm{nm}}\)).

This simple TLF model also enables the construction of a charge noise environment to predict the qubit performance. With the co-simulation framework reported in ref. 64, we estimate the two-qubit SWAP gate fidelities with above TLF distribution (see Supplementary Information section 7). The average SWAP error in our models is lower than \(0.1 \%\), highlighting the low noise level of Si MOS quantum dots with industrial manufacturing. Meanwhile, a relatively large variation in qubit fidelity due to the randomly distributed TLFs can also be captured in the simulation, suggesting that statistical analysis on the qubit metrics is needed to properly assess the qubit environment.

Discussion

We show the integration of Si MOS quantum dots with full industrial 300 mm wafer fabrication. By leveraging the know-how of CMOS technology, we optimize the full gate stack for high performance spin qubit devices with high yield and uniformity, as previously reported in 7. The Si/SiO2 interface shows state-of-the art Hall mobility and critical density. Considering the nanoscale nature of the quantum dots versus the full 300 mm wafer, we characterize multiple SETs for statistical analysis. The SET gates demonstrate uniform turn on curves and single quantum dot formation in the milli-Kelvin temperature range. We further characterize the SETs using current spectroscopy techniques and extract record-low average charge noise of 0.61 \({\rm{\mu }}{\rm{eVH}}{{\rm{z}}}^{-0.5}\) on Si MOS structures. The stable, uniform, and low noise operation is comparable to the best reported SiGe heterostructure base devices, which shift the interface to the deeper Si/SiGe quantum wells to reduce the influence from disorders. However, the Si/SiGe buried quantum well brings significant drawbacks in terms of valley splitting50,68 as well as crosstalk69, limiting the yield rate and addressability of large qubit arrays. Our results confirm the Si MOS is and remains a compelling material platform for spin qubits and the maturity of industrial fabrication for the qubit development.

The low noise quantum dot together with its nanoscale size could be an excellent probe for TLFs and their microscopic nature. The statistical analysis of the charge noise shows uniform distributions with respect to different metrics. Noise spectra reconstructed with a simple TLF model can also match the experiments well. These findings are strong evidence that the quantum dot charge noise indeed originates from randomly distributed DWP type defects over the nanoscale area. Future studies could investigate the influence of gate oxide thickness on charge noise and explore novel detection methods for slow TLFs across the gate stack.

A thorough understanding of the qubit environment is crucial for upscaling to large and reproducible qubit arrays. Our statistical analysis of the quantum dot charge noise and the TLF model provides important insights into the microscopic origin of charge noise. Our methodologies also have the advantage of faster throughput and statistical relevance compared to much slower experimental data from individual qubits – the slow throughput of the latter currently limiting our understanding and being subject to uncorrected drift phenomena that affect qubit metrics30. We therefore believe that our results and methodologies will allow efficient feedback into the qubit design optimization process and help advance the scaling up of spin qubit devices.

Methods

300 mm device integration

The quantum dot devices are fabricated with a 300 mm integration flow. The fabrication starts with intrinsic silicon wafers. Optical lithography was used to defined alignment markers and ohmic implantation. Then electron beam lithography (EBL) is used to pattern the pitch-critical quantum dot gates. Here we employ EBL for flexible and short turnaround replacement for advanced optical lithography70. For better process compatibility, we use the same photoresist for EBL as advanced optical lithography. Apart from the light/e-beam sensitive layer, there is also a hardmask layer at the bottom of the photoresist, which helps preserve the pattern during the etching process15. As shown in Fig. 1a, the quantum dot gate stack starts from thermally grown SiO2, followed by the polysilicon layer with chemical vapor deposition and photoresist. Then the photoresist is patterned by EBL and transferred to the polysilicon gate subtractively with plasma dry etching. The 2nd and 3rd gate layer starts with the deposition of inter-gate dielectric. Then similar processes as the 1st gate layer are used for patterning. After that, we switch back to optical lithography. Another layer of silicon oxide is deposited followed by optically defined ESR antenna or EDSR micromagnets as qubit control structures. Finally, the quantum dot structures are encapsulated with a back end of line module, including a thick layer of silicon oxide, qubit gate via contact, metal bonding pad, and forming gas annealing. Through the integration process, we employ inline and post-line process monitoring. Tight critical dimension (CD) control is achieved for all gate layers, with a standard deviation ~1 nm for quantum dot gates. After full processing, electrical characterization of different metrology structures is carried out to verify the processing. Additionally, room temperature leakage and \({I}_{{\rm{D}}}{V}_{{\rm{G}}}\) sweeps of the quantum dots are carried out to determine the yield as described in 7, with this particular process resulting in a 95% yield. More details about the integration flow, process monitoring, and proof of principle qubit operation can be found in ref. 7,35.

In our previous study, we report charge noise in the few µeV \({\rm{H}}{{\rm{z}}}^{-0.5}\) range (3.6 µeV \({\rm{H}}{{\rm{z}}}^{-0.5}\) with single data point in ref. 35). Through full gate stack optimization, we achieve the low noise environments in this work. For the first gate level, the improvement in the Hall mobility is due to a thicker dry oxide layer (12 nm vs 8 nm) than our previous work48, which can be attributed to a further oxide/deposited oxide interface. For the higher gate layers, we increase the deposited ALD silicon oxide thickness from 5 nm to 8 nm. To reduce the damage in the dry etching process, we replaced the etchant from chlorine-based to hydrogen bromide71, as the heavy bromide ion could provide better selectivity at the end of polysilicon etching, which would reduce the physical bombardment damage. In addition, we carefully control the etching time by monitoring the emission spectra during the dry etching process.

Hall bar characterization

The fast turn-over interface characterization is carried out in a cryogenic probe station with base temperature of \(4\,{\rm{K}}\) and a \(2.5\,{\rm{T}}\) magnet. This allows us to refine the process and identify high quality gate stacks with optimized processes for further detailed characterization. The advanced interface characterization is carried out in a dilution fridge with a base temperature of \(8\,{\rm{mK}}\) and a \(3\,{\rm{T}}\) magnet. Both setups employ a standard Hall bar measurement procedure where a positive voltage is applied to the top gate to form a 2-dimensional electron gas (2DEG) at the Si/SiO2 interface. The current through the sample is measured through an IV transimpedance amplifier. Additionally, the longitudinal and transverse Hall voltages are measured simultaneously using standard lock-in techniques. The Hall carrier sheet density \({n}_{{\rm{S}}}\) is extracted from the Hall resistance \({R}_{{xy}}\,=\,{\bf{B}}\cdot {n}_{{\rm{S}}}\cdot e\), where \(B\) is the magnetic field, \({n}_{S}\) is the 2DEG density, and \(e\) is the electron charge. The carrier mobility \(\mu\) is obtained from \(\mu \,=\,{n}_{S}\cdot e\cdot {\rho }_{0}\) where \({\rho }_{0}\) is the resistivity. The percolation density is extracted from a metal-to-insulator transition (MIT) fit of the density dependent conductivity \(\sigma \sim {({n}_{{\rm{S}}}-{n}_{{\rm{p}}})}^{1.31}\). The measurement is repeated on three different Hall bars across the wafer, and we found good agreement.

Quantum dot threshold voltage and subthreshold swing

A fourth order routine is used to calculate the derivative of the measured \({I}_{{\rm{D}}}{V}_{{\rm{G}}}\) data. The maximum derivative (maximum transconductance \({g}_{{\rm{m}}}\)) of the curve is used to calculate the threshold voltage \({V}_{{\rm{TH}}}\) and the conductance \({K}_{0}\). All gates of the quantum dot were operated in the linear regime where the drain current is given by \({I}_{{\rm{D}}}={K}_{0}\left({V}_{{\rm{G}}}-{V}_{{\rm{TH}}}-{V}_{{\rm{D}}}/2\right){V}_{{\rm{D}}}\). Thus, the \({I}_{{\rm{D}}}{V}_{{\rm{G}}}\) is used to fit \({K}_{0}\) and \({V}_{{\rm{TH}}}\). The conductivity \({K}_{0}\) equals the fitted slope divided by the drain voltage. The threshold voltage \({V}_{{\rm{TH}}}\) is the intercept of the tangent line \({g}_{{{\rm{m}}}_{\max }}\) with the x-axis minus \({V}_{{\rm{D}}}/2\).

Electrical characterization of the quantum dots

The devices are tuned systematically with the following procedure. From the barrier gate stability map, we identify the barrier gate voltage. We then sweep the top gate bias from \(3.5\,{\rm{V}}\) to \(4.0\,{\rm{V}}\) to measure the Coulomb oscillations. If a background current is observed between the Coulomb oscillations, the barrier gates are readjusted, and the measurement repeated. The source drain bias is then swept with respect to the top gate voltage to obtain Coulomb diamonds. We measure the drain current noise and convert the time domain signal to the effective single-sided (double sideband) spectral density with a Hann window. During the data collection, the spectrum is smoothed with an exponential averaging filter of \({{\rm{s}}}_{{\rm{t}}}={{\rm{\alpha }}}_{\exp }{{\rm{x}}}_{{\rm{t}}}+(1-{{\rm{\alpha }}}_{\exp }){{\rm{s}}}_{{\rm{t}}-1}\), where \({{\rm{s}}}_{{\rm{t}}}\) (\({{\rm{s}}}_{{\rm{t}}-1}\)) is the current (previous) spectrum and \({{\rm{\alpha }}}_{\exp }\) is the smoothing factor. We use \({{\rm{\alpha }}}_{\exp }\) of 2/31 (or weight of 30) and a total measurement time 10 times longer than the single spectrum collection time (as the spectrum is stable and we do not see difference with longer measurement times). The current noise spectrum is converted to charge noise spectrum using \({S}_{0}=\alpha \sqrt{{S}_{I}}/({dI}/d{V}_{{ST}})\), where \(\alpha\) is the lever arm of the quantum dot, and \({dI}/d{V}_{{ST}}\) is the slope of the Coulomb peak. Further details on extracting the quantum dot charge noise can be found in the Supplementary Information section 2.

Data availability

The data that support the findings of this study are available from the authors upon reasonable request.

Code availability

The analysis and plotting codes used in this study are available from the authors upon reasonable request.

References

Feynman, R. P. Simulating physics with computers. In Feynman and computation Vol. 22, 133–153 (CRC Press, 2018).

Arute, F. et al. Quantum supremacy using a programmable superconducting processor. Nature 574, 505–510 (2019).

Daley, A. J. et al. Practical quantum advantage in quantum simulation. Nature 607, 667–676 (2022).

Zhong, H.-S. et al. Quantum computational advantage using photons. Science 370, 1460–1463 (2020).

Preskill, J. Quantum computing in the NISQ era and beyond. Quantum 2, 79 (2018).

Maurand, R. et al. A CMOS silicon spin qubit. Nat. Commun. 7, 13575 (2016).

Li, R. et al. A flexible 300 mm integrated Si MOS platform for electron- and hole-spin qubits exploration. in 2020 IEEE International Electron Devices Meeting (IEDM) 38.3.1-38.3.4 (IEEE, 2020).

Zwerver, A. M. J. et al. Qubits made by advanced semiconductor manufacturing. Nat. Electron. 5, 184–190 (2022).

Radamson, H. H. et al. State of the art and future perspectives in advanced CMOS technology. Nanomaterials 10, 1555 (2020).

Pillarisetty, R. et al. High Volume Electrical Characterization of Semiconductor Qubits. in 2019 IEEE International Electron Devices Meeting (IEDM) 31.5.1-31.5.4 (IEEE, 2019).

Fowler, A. G., Mariantoni, M., Martinis, J. M. & Cleland, A. N. Surface codes: towards practical large-scale quantum computation. Phys. Rev. A 86, 032324 (2012).

Bohr, M. A 30 year retrospective on Dennard’s MOSFET scaling paper. IEEE Solid-State Circuits Newsl. 12, 11–13 (2007).

Zwanenburg, F. A. et al. Silicon quantum electronics. Rev. Mod. Phys. 85, 961–1019 (2013).

Hanson, R., Kouwenhoven, L. P., Petta, J. R., Tarucha, S. & Vandersypen, L. M. K. Spins in few-electron quantum dots. Rev. Mod. Phys. 79, 1217–1265 (2007).

Van Zant, P. Microchip fabrication: a practical guide to semiconductor processing. (McGraw-Hill Professional, 2014).

Vandersypen, L. M. K. et al. Interfacing spin qubits in quantum dots and donors—hot, dense, and coherent. Npj Quantum Inf. 3, 34 (2017).

Muhonen, J. T. et al. Storing quantum information for 30 seconds in a nanoelectronic device. Nat. Nanotechnol. 9, 986–991 (2014).

Veldhorst, M. et al. An addressable quantum dot qubit with fault-tolerant control-fidelity. Nat. Nanotechnol. 9, 981–985 (2014).

Yoneda, J. A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than 99.9%. Nat. Nanotechnol. 13, 6 (2018).

Noiri, A. et al. Fast universal quantum gate above the fault-tolerance threshold in silicon. Nature 601, 338–342 (2022).

Xue, X. et al. Quantum logic with spin qubits crossing the surface code threshold. Nature 601, 343–347 (2022).

Mills, A. R. et al. High fidelity state preparation, quantum control, and readout of an isotopically enriched silicon spin qubit. Phys. Rev. Appl. 18, 064023 (2022).

Philips, S. G. J. et al. Universal control of a six-qubit quantum processor in silicon. Nature 609, 919–924 (2022).

Yang, C. H. et al. Silicon qubit fidelities approaching incoherent noise limits via pulse engineering. Nat. Electron. 2, 151–158 (2019).

Petit, L. et al. Universal quantum logic in hot silicon qubits. Nature 580, 355–359 (2020).

Camenzind, L. C. et al. A hole spin qubit in a fin field-effect transistor above 4 kelvin. Nat. Electron. 5, 178–183 (2022).

Yang, C. H. et al. Operation of a silicon quantum processor unit cell above one kelvin. Nature 580, 350–354 (2020).

Veldhorst, M., Eenink, H. G. J., Yang, C. H. & Dzurak, A. S. Silicon CMOS architecture for a spin-based quantum computer. Nat. Commun. 8, 1766 (2017).

Li, R. et al. A crossbar network for silicon quantum dot qubits. Sci. Adv. 4, eaar3960 (2018).

Struck, T. et al. Low-frequency spin qubit energy splitting noise in highly purified 28Si/SiGe. Npj Quantum Inf. 6, 40 (2020).

Connors, E. J., Nelson, J., Edge, L. F. & Nichol, J. M. Charge-noise spectroscopy of Si/SiGe quantum dots via dynamically-decoupled exchange oscillations. Nat. Commun. 13, 940 (2022).

Kranz, L. et al. Exploiting a single‐crystal environment to minimize the charge noise on qubits in silicon. Adv. Mater. 32, 2003361 (2020).

Wuetz, B. P. et al. Reducing charge noise in quantum dots by using thin silicon quantum wells. Nat. Commun. 14, 1385 (2023).

Bohuslavskyi, H. et al. Scalable on-chip multiplexing of low-noise silicon electron and hole quantum dots. 33.

Stuyck, N. I. D. et al. Uniform spin qubit devices with tunable coupling in an all-silicon 300 mm integrated process. in 2021 Symposium on VLSI Circuits 1–2 (IEEE, 2021). https://doi.org/10.23919/VLSICircuits52068.2021.9492427.

Spence, C. et al. Probing charge noise in few electron CMOS quantum dots. Phys. Rev. Appl. 19, 044010 (2023).

Kotlyar, R. et al. Mitigating Impact of Defects On Performance with Classical Device Engineering of Scaled Si/SiGe Qubit Arrays. in 2022 International Electron Devices Meeting (IEDM) 8.4.1-8.4.4 (IEEE, 2022).

Müller, C., Cole, J. H. & Lisenfeld, J. Towards understanding two-level-systems in amorphous solids: insights from quantum circuits. Rep. Prog. Phys. 82, 124501 (2019).

Dutta, P. Low-frequency fluctuations in solids: 1/f noise. Rev. Mod. Phys. 53, 497–516 (1981).

Culcer, D., Hu, X. & Das Sarma, S. Dephasing of Si spin qubits due to charge noise. Appl. Phys. Lett. 95, 073102 (2009).

Culcer, D. & Zimmerman, N. M. Dephasing of Si singlet-triplet qubits due to charge and spin defects. Appl. Phys. Lett. 102, 232108 (2013).

Bermeister, A., Keith, D. & Culcer, D. Charge noise, spin-orbit coupling, and dephasing of single-spin qubits. Appl. Phys. Lett. 105, 192102 (2014).

Machlup, S. Noise in semiconductors: spectrum of a two‐parameter random signal. J. Appl. Phys. 25, 341–343 (1954).

Yang, C. H. et al. Spin-valley lifetimes in a silicon quantum dot with tunable valley splitting. Nat. Commun. 4, 2069 (2013).

Thorbeck, T. & Zimmerman, N. M. Formation of strain-induced quantum dots in gated semiconductor nanostructures. AIP Adv. 5, 087107 (2015).

Fonash, S. J. An overview of dry etching damage and contamination effects. J. Electrochem. Soc. 137, 3885–3892 (1990).

Camenzind, T. N. et al. High mobility SiMOSFETs fabricated in a full 300 mm CMOS process. Mater. Quantum Technol. 1, 041001 (2021).

Ha, W. et al. A flexible design platform for Si/SiGe exchange-only qubits with low disorder. Nano Lett. 22, 1443–1448 (2022).

Lodari, M. et al. Valley splitting in silicon from the interference pattern of quantum oscillations. Phys. Rev. Lett. 128, 176603 (2022).

Tracy, L. A. et al. Observation of percolation-induced two-dimensional metal-insulator transition in a Si MOSFET. Phys. Rev. B 79, 235307 (2009).

Paquelet Wuetz, B. et al. Multiplexed quantum transport using commercial off-the-shelf CMOS at sub-kelvin temperatures. Npj Quantum Inf. 6, 43 (2020).

Das Sarma, S. & Stern, F. Single-particle relaxation time versus scattering time in an impure electron gas. Phys. Rev. B 32, 8442–8444 (1985).

Lodari, M. et al. Low percolation density and charge noise with holes in germanium. Mater. Quantum Technol. 1, 011002 (2021).

Mani, R. G. & Anderson, J. R. Study of the single-particle and transport lifetimes in GaAs/ Al x Ga 1 − x As. Phys. Rev. B 37, 4299–4302 (1988).

Elzerman, J. M., Hanson, R., Vandersypen, L. M. K. & Kouwenhoven, L. P. Single-shot read-out of an individual electron spin in a quantum dot. 430, 5 (2004).

Fogarty, M. A. et al. Integrated silicon qubit platform with single-spin addressability, exchange control and single-shot singlet-triplet readout. Nat. Commun. 9, 4370 (2018).

Ono, K., Austing, D. G., Tokura, Y. & Tarucha, S. Current rectification by pauli exclusion in a weakly coupled double quantum dot system. Science 297, 1313–1317 (2002).

Kouwenhoven, L. P., Marcus, C. M., Mceuen, P. L., Tarucha, S. & Wingreen, N. S. Electron transport in quantum dots. In Mesoscopic Electron Transport, Vol. 345 (eds Sohn, L.L., et al.), 105–214 (Springer, Dordrecht,1997).

Angus, S. J., Ferguson, A. J., Dzurak, A. S. & Clark, R. G. Gate-defined quantum dots in intrinsic silicon. Nano Lett. 7, 2051–2055 (2007).

Neyens, S. et al. “ Probing single electrons across 300 mm spin qubit wafers.” Nature 629, 80–85 (2024).

Yoneda, J. et al. Robust micromagnet design for fast electrical manipulations of single spins in quantum dots. Appl. Phys. Express 8, 084401 (2015).

Takeda, K. et al. A fault-tolerant addressable spin qubit in a natural silicon quantum dot. Sci. Adv. 2, e1600694 (2016).

MacQuarrie, E. R. et al. Progress toward a capacitively mediated CNOT between two charge qubits in Si/SiGe. Npj Quantum Inf. 6, 81 (2020).

Shehata, M. M. E. K. et al. Modelling semiconductor spin qubits and their charge noise environment for quantum gate fidelity estimation. Phys. Rev. B. 108, 045305 (2023).

Barnes, E., Kestner, J. P., Nguyen, N. T. T. & Das Sarma, S. Screening of charged impurities with multielectron singlet-triplet spin qubits in quantum dots. Phys. Rev. B 84, 235309 (2011).

Leon, R. C. C. et al. Coherent spin control of s-, p-, d- and f-electrons in a silicon quantum dot. Nat. Commun. 11, 797 (2020).

Ashlea Alava, Y. et al. Ultra-shallow all-epitaxial aluminum gate GaAs/AlxGa1−xAs transistors with high electron mobility. Adv. Funct. Mater. 32, 2104213 (2022).

Wuetz, B. P. et al. Atomic fluctuations lifting the energy degeneracy in Si/SiGe quantum dots. Nat. Commun. 13, 7730 (2022).

Lawrie, W. I. L. et al. Quantum dot arrays in silicon and germanium. Appl. Phys. Lett. 116, 080501 (2020).

Hayakawa, H. et al. Next generation electron beam lithography system F7000 for wide range applications. In Photomask and NGL Mask Technology XX Vol. 8701 (ed. Kato, K.) 9-15 (SPIE, 2013).

Kim, D., Kim, Y. K. & Lee, H. A study of the role of HBr and oxygen on the etch selectivity and the post-etch profile in a polysilicon/oxide etch using HBr/O2 based high density plasma for advanced DRAMs. Mater. Sci. Semicond. Process. 10, 41–48 (2007).

Acknowledgements

We thank J. Wendoloski and A. Hamilton for helpful discussions about the quantum Hall analysis. The authors acknowledge financial support from European Union’s Horizon 2020 Research and Innovation Program under grant agreement No 951852 (QLSI). This work was performed as part of IMEC’s Industrial Affiliation Program (IIAP) on Quantum Computing.

Author information

Authors and Affiliations

Contributions

A.E., M.M.K.S., and C.G. performed the experiments. S.K. integrated the devices with support from S.M., Y.C., and J.J. M.M.K.S. performed the simulation with support from G.S. R.L., M.M., D.W., B.G. I.R., P.V.D. and K.D.G. conceived and supervised the project. A.E., R.L., and K.D.G. wrote the manuscript with input from all the authors.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Elsayed, A., Shehata, M.M.K., Godfrin, C. et al. Low charge noise quantum dots with industrial CMOS manufacturing. npj Quantum Inf 10, 70 (2024). https://doi.org/10.1038/s41534-024-00864-3

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41534-024-00864-3

- Springer Nature Limited