Abstract

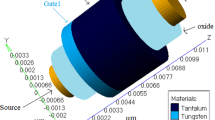

This paper presents a novel structure of TSV-based silicon nanotube gate-all-around FETs (both junction-based and junctionless) along with their electrical characteristics using Silvaco ATLAS 3D device simulator. In comparison, the junctionless silicon nanotube gate-all-around structures presented an excellent performance improvement over the junction-based structures in terms of short channel effects, an improved drain-induced barrier lowering of ~ 28% for n-MOS and ~ 22% for p-MOS, and improved (ION/IOFF) switching ratio of ~ 68% for n-MOS and ~ 42% for p-MOS. Similarly, the junctionless structure shows a steep subthreshold value very close to the ideal value (~ 60 mv/dec). Furthermore, the static and transient characteristics of CMOS inverter circuits designed using the complementary device architecture have been explored using mixed-mode simulations. The noise margin and propagation delay of the circuit are analyzed and are found to agree with the information available in the literature for nano-scaled devices.

Similar content being viewed by others

Data availability

No datasets were generated or analysed during the current study.

References

Ambika R, Srinivasan R (2018) Impact of structural process variation on junctionless silicon nanotube FET. Adv Nat Sci Nanosci Nanotechnol 9(3):035015

Buddharaju KD, Singh N, Rustagi SC, Teo SHG, Lo GQ, Balasubramanian N, Kwong DL (2008) Si-nanowire CMOS inverter logic fabricated using gate-all-around (GAA) devices and top-down approach. Solid-State Electron 52(9):1312–1317

David Gerke Jet Propulsion Laboratory, Pasadena, California, “Through-Silicon Via Technology”, NASA Electronic Parts and Packaging (NEPP) Program Office of Safety and Mission Assurance, 2009.

Djeffal F, Ferhati H, Bentrcia T (2016) Improved analog and RF performances of gate-all-around junctionless MOSFET with drain and source extensions. Superlattices Microstruct 90:132–140

Fahad HM, Hussain MM (2012) Are nanotube architectures more advantageous than nanowire architectures for field effect transistors? Sci Rep 2(1):475

Fahad HM, Smith CE, Rojas JP, Hussain MM (2011) Silicon nanotube field effect transistor with core-shell gate stacks for enhanced high performance operation and area scaling benefits. Am Chem Soc 11:4393–4399

Gagnard X, Mourier T (2010) Through silicon via: From the CMOS imager sensor wafer level package to the 3D integration. Microelectron Eng 87(3), 470–476

Gautam R, Saxena M, Gupta RS, Gupta M (2013) Numerical analysis of localised charges impact on the static and dynamic performance of nanoscale cylindrical surrounding gate MOSFET based CMOS inverter. Microelectron Reliab 53(2):236–244

Hussain MM, Fahad HM, Smith CE, Rojas JP (2015) Cylindrical-Shaped Nanotube Field Effect Transistor”, US Patent application USOO9224813B2

Jena B, Dash S, Mishra GP (2018) Improved switching speed of a CMOS inverter using work-function modulation engineering. IEEE Trans Electron Devices 65(6):2422–2429

Karmarkar AP, Guo W, Xiaopeng X, Van der Plas G, Van Huylenbroeck S, Gonzalez M, Absil P, El Sayed K, Beyne E (2016) Performance and reliability impact of copper plasticity in backside TSV-last fabrication process. IEEE Trans Device Mater Reliab 16(3):402–412

NH Khan, SM Alam, and S Hassoun (2011). Power Delivery Design for 3-D ICs Using Different Through-Silicon Via (TSV) Technologies. IEEE Transactions on Very Large-Scale Integration (VLSI) Systems, 19(4)

Kim DH, Mukhopadhyay S, Lim SK (2011) Fast and accurate analytical modeling of through-silicon-via capacitive coupling. IEEE Trans Adv Packag 1:168–180

Kim DH, Athikulwongse K, and Lim SK (2013) Study of through-silicon-via impact on the 3-D stacked IC Layout. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 21(5).

Knickerbocker JU, Andry PS, Dang B, Horton RR, Interrante MJ, Patel CS, Polastre RJ, Sakuma K, Sirdeshmukh R, Sprogis EJ, Sri-Jayantha SM, Stephens AM, Topol AW, Tsang CK, Webb BC, Wright SL (2008) Three dimensional silicon integration. IBM J Res Dev 52(6):553–569

Kothandaraman C, Rosenblatt S, Wang G (2014), “TSV Structure with a Built-In U-Shaped FET Transistor for Improved Characterization”, US Patent application US 20140319600A1 by International Business Machines Corporation (IBM)

Lee J, Ryu M, Kim Y (2015) On-Chip interconnect boosting technique by using of 10nm double gate-all around (DGAA) transistor. IEICE Electronics Express 12:1–11

Liu TY, Pan FM, Sheu JT (2015) Characteristics of gate-all-around junctionless polysilicon nanowire transistors with twin 20-nm gates. J Electron Devices Soc 3(5):405–409

Majima H, Ishikuro H, Hiramoto T (2000) Experimental evidence for quantum mechanical narrow channel effect in ultra-narrow MOSFET’s. IEEE Electron Device Lett 21(8):396–398

Nayak K, Bajaj M, Konar A, Oldiges PJ, Natori K, Iwai H, Murali KVRM, Rao VR (2014) CMOS logic device and circuit performance of Si gate all around nanowire MOSFET. IEEE Trans Electron Devices 61(9):3066–3074

Panda SR, Pradhan KP, Sahu PK (2017) Device and circuit performance of Si-based accumulation-mode CGAA CMOS inverter. Mater Sci Semicond Process 66:87–91

Qian L, Qian K, He X, Chu Z, Ye Y, Shi G, and Xia Y (2019), Through-Silicon Via-Based Capacitor and Its Application in LDO Regulator Design. IEEE Transactions on Very Large-Scale Integration (VLSI) Systems, 27(8).

Rustagi SC, Singh N, Fang WW, Buddharaju KD, Omampuliyur SR, Teo SHG, Tung CH, Lo GQ, Balasubramanian N, Kwong DL (2007) CMOS inverter based on gate-all-around silicon-nanowire MOSFETs fabricated using top-down approach. IEEE Electron Device Lett 28(11):1021–1024

Ramm P, Klumpp A, Weber J, Taklo MM (2010) 3D system-on-chip technologies for more than moore systems. Microsyst Technol 16:1051–1055

Ryu M, Bien F, Kim Y (2016a) Optimal inverter logic gate using 10-nm double gate-all-around (DGAA) transistor with asymmetric channel width. AIP Adv 6:015311

Ryu M, Bien F, and Kim Y (2016) Optimal inverter logic gate using 10-nm double gate-all-around (DGAA) transistor with asymmetric channel width, AIP ADVANCES

Savidis I, Alam SM, Jain A, Pozder S, Jones RE, Chatterjee R (2010) Electrical modeling and characterization of through-silicon vias (TSVs) for 3-D integrated circuits. Microelectron J 41(1):9–16

Singh A, Pandey CK (2022) Improved DC performances of gate-all-around Si-nanotube tunnel FETs using gate-source overlap. SILICON 14:1463–1470

Singh A, Pandey CK, Chaudhury S et al (2021) Tuning of threshold voltage in silicon nano-tube FET using halo doping and its impact on Analog/RF performances. SILICON 13:3871–3877

Singh A, Pandey CK, Nanda U (2022) Performance analysis of silicon nanotube dielectric pocket tunnel FET for reduced ambipolar conduction. Microelectron J 126:105512

Singh N, Agarwal A, Bera LK, Liow TY, Yang R, Rustagi SC, Tung CH, Kumar R, Lo GQ, Balasubramanian N, Kwong DL (2006) High-performance fully depleted silicon nanowire (Diameter ≤ 5 nm) gate-all-around CMOS devices. IEEE Electron Device Lett 27(5):383–386

Singh A, Chaudhary S, Sharma SM, Sarkar CK (2020) Improved drive capability of silicon nano tube tunnel FET using halo implantation. Silicon 12(11):2555–2561

Tekleab D (2014) Device performance of silicon nanotube field effect transistor. IEEE Electron Device Lett 35(5):506–508

Tekleab D, Tran HH, Sleight JW, Chidambarrao D (2012). Silicon Nanotube MOSFET, US Patent application US 20120217468A1.

Winkler F, Killge S, Fischer D, Richter K, Hiess A, Bartha JW (2018) TSV transistor—vertical metal gate FET inside a through silicon VIA. IEEE Electron Device Lett 39(10):1493–1496

Xu Z, Lu JQ (2011) High-speed design and broadband modeling of through-strata-vias (TSVs) in 3D integration. IEEE Trans Compon Packag Manuf Technol 1(2):154–162

Author information

Authors and Affiliations

Contributions

BS wrote the paper and also guided the other two authors in simulation work. RD did the reviews and figure preparations. etc. SB simulated the results and compared the work with existing work

Corresponding author

Ethics declarations

Conflict of interests

The authors declare no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Singh, B., Devi, R. & Bala, S. Performance enhancement of junctionless silicon nanotube gate-all-around FETs for nano-scaled devices. Multiscale and Multidiscip. Model. Exp. and Des. (2024). https://doi.org/10.1007/s41939-024-00402-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s41939-024-00402-w