Abstract

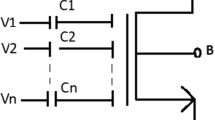

This paper presents seven novel ‘Lower-part approximate multi-bit adders’ (LAMAs). The LAMAs namely lower-part NOR, AND, NAND, XOR, XNOR, ‘lower-part constant-1 adder’ (LCONE), and ‘lower-part constant-0 adder’ (LCZERO) are derived based on the hardware architecture of ‘Lower-part OR adder’ (LOA). The performance metrics of these proposed adders are compared with LOA, lower-part NOT1, and lower-part NOT2. For a fair comparison an 8-bit LAMA is designed using Verilog ‘hardware-description-langauge’ (HDL). The 8-bit LAMA is divided into two equal segments namely ‘most-significant-bit’ (MSB) and ‘least-significant-bit’ (LSB) adders. The MSB adder is designed using ‘ripple carry adder’ (RCA) and LSB adder is designed using LAMA. To assess the performance of the proposed adders, all the ten adders are compared in terms of ‘design metrics’(DMs) such as power, delay, ‘power-delay-product’ (PDP), and area. To extract the DMs for performance comparison, all the ten adders have been designed using a Verilog ‘register-transfer-level’ (RTL) code. The RTL coded adders are then synthesized using Cadences’ ‘RTL-Compiler’(RC) tool, using 180 nm standard cell library. The synthesis results show that proposed LAMAs have better DMs compared to conventional LOA. Further to demonstrate the application of LAMAs, an image addition is performed using standard test images and their respective ‘peak-signal-to-noise-ratio’(PSNR) and ‘structural similarity index’ (SSIM) have also been extracted. The PSNR values of the proposed LAMAs are found to be better than the reported LAMAs.

Similar content being viewed by others

References

Alouani I, Ahangari H, Ozturk O, Nair S (2018) A novel heterogeneous approximate multiplier for low power and high performance. IEEE Embed Syst Lett 10(2):45–48

Parameshwara MC, Srinivasaiah HC (2017) Low-power hybrid 1-bit full adder circuit for energy efficient arithmetic applications. J Circ Syst Comput 26(1):1–15

Ataei S, Stine JE (2018) A 64 kB approximate SRAM architecture for low-power video applications. IEEE Embed Syst Lett 10(1):10–13

Pashaeifer M, Kamal M, Afzali-Kusha A, Pedram M (2019) A theoretical framework for quality estimation and optimization of DSP applications using low-power approximate adders. IEEE Trans Circ Syst I 66(1):327–340

Najafi A, Weibrich M, Vaya G. P, Garcia-Ortiz A (2017) A fair comparison of adders in stochastic regime. In: Proceeding of International Symposium on Power and Timing Modeling, Optim. and Simu. (PATMOS), 1–4

Osorio RR, Rodriguez G (2019) Truncated SIMD multiplier architecture for approximate computing in low-power programmable processors. IEEE Access 7:56353–56366

Almurib HAF, Kumar TN, Lombardi F (2016) Inexact designs for approximate low power addition by cell replacement. In: Proceeding of IEEE international conferences on design, automation, and test in Europe conference and exhibition (DATE), 660–665

Shin D, Gupta SK (2010) Approximate logic synthesis for error tolerant applications. In: Proceeding of IEEE international conferences on design, automation, and test in Europe conference and exhibition (DATE), 1–4

Shin D, Gupta SK (2008) A re-design technique for datapath modules in error tolerant applications. In: Proceedings of 17th Asian Test Symposium, pp 431–437

Mahdiani HR, Ahmadi A, Fakhraie SM, Lucas C (2010) Bio-inspired imprecise computational blocks for efficient VLSI implementation of soft-computing applications. IEEE Trans Circ Syst I 57(4):850–862

Dalloo A, Najafi A, Garcia-Ortiz A (2018) Systematic design of an approximate adder: the optimized lower part constant-OR adder. IEEE Trans Very Large Scale Int Syst 26(8):1595–1599

Parameshwara MC (2021) Approximate full adders for energy efficient image processing applications. J Circ Syst Comput 30(13):1–17

Anusha G, Deepa P (2019) Design of approximate adders and multipliers for error tolerant image processing. J Microprocess Microsyst 72(2):1–7

Yang C, Jiao H (2019) Low-power Karnaugh map approximate adder for error compensation in loop accumulations. In: Proceeding of IEEE International Conference on IC Design and Technology (ICICDT), 1–4

Ramaswamy M, Narmadha G, Deivasigamani S (2019) Carry based approximate full adder for low power approximate computing. In: Proceeding of IEEE International Conference on Smart Computing and Communications, 1–4

Zareei Zahra, Navi Keivan, Keshavarziyan Peiman (2018) Low-power, high-speed 1-bit inexact full adder cell designs applicable to low-energy image processing. Taylor Francis Int J Electron 105(3):375–384

Zhang T, Liu W, McLarnon E, O’Neill M, Lombardi F (2018) Design of majority logic (ML) based approximate full adders. In: Proceedings of IEEE international symposium on circuits and systems, pp 1–5

Lin I-C, Yang Y-M, Lin C-C (2015) High-performance low-power carry speculative addition with variable latency. IEEE Trans Very Large Scale Integr 23(9):1591–1603

Li L, Zhou H (2014) On error modeling and analysis of approximate adders. In: Proceeding of IEEE/ACM international conference on computer-aided design (ICCAD), 511–518

Vaibhav G, Debabrata M, Anand R, Kaushik R (2013) Low-power digital signal processing using approximate adders. IEEE Trans Comput-Aided Des Integr Circ Syst 32(1):124–137

Kim Y, Zhang Y, Li P (2013) An energy efficient approximate adder with carry skip for error resilient neuromorphic VLSI systems. In: Proceeding of IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 130–137

Yang Z, Jain A, Liang J, Han J, Lombardi F (2013) Approximate XOR/XNOR-based adders for inexact computing. In: Proceeding of IEEE International Conference on Nanotechnology (NANO), 690–693

Zhu N, Goh WL, Zhang W, Yeo KS, Kong ZH (2010) Design of low-power high speed truncation-error-tolerant adder and its application in digital signal processing. IEEE Trans Very Large Scale Int Syst 18(8):1225–1229

Chinna VG, Parameshwara MC, Savita S (2020) Comparative analysis of various approximate full adders under RTL codes. ICTACT J Microelectron 6(2):947–952

Jie H, Michael O (2013) Approximate computing: an emerging paradigm for energy-efficient design. In: Proceeding of International Conference of IEEE European Test Symposium (ETS) 1–4

Hegde R, Shanbhag NR (2001) Soft digital processing. IEEE Trans Very Large Scale Int 9(6):813–823

Banerjee N, Karakonstantis G, Roy K (2007) process variation tolerant low power DCT architecture. In: Proceeding Design, Auto. and Test in Europe, 1–6

Verma AK, Brisk P, Ienne P (2008) Variable latency speculative addition: a new paradigm for arithmetic circuit design. In: Proceeding of IEEE International Conference on Design, Auto. and Test in Europe Conference and Exhibition (DATE), 1250–1255

Haung J, Lach J, Robins G (2012) A methodology for energy-quality tradeoff using imprecise hardware. In: Proceeding of IEEE International Conference on Design, Auto. and Test in Europe Conference and Exhibition (DATE), 504–509

Mohapatra D, Chippa V, Raghunathan A and Roy K (2011) Design of voltage-scalable meta-functions for approximate computing. In: Proceeding of IEEE International Conference on Design, Auto. and Test in Europe Conference and Exhibition (DATE), 1–6

Miao J, He K, Gerstlauer A and Orshansky M (2012) Modeling and and synthesis of quality-energy optimal approximate adders. In: Proceeding of IEEE International Conference on Comp. Aided Design (ICCAD), 728–735

Kahng AB, Kang S (2012) Accuracy-configurable adder for approximate arithmetic designs. In: Proceeding of IEEE Design, Auto., Conference (DAC), 820–825

Liu C, Han J, Lombardi F (2015) An analytical framework for evaluating the error characteristics of approximate adders. IEEE Trans Comput 64(5):1268–1281

Liu W, Chen L, Wang C, ONeill M, Lombardi F (2014) Inexact floating-point adder for dynamic image processing. In: Proceeding of IEEE International Conference on Nanotechnology (NANO), 239–243

Shim B, Sridhara S, Shanbhag N (2004) Reliable low-power digital signal processing via reduced precision redundancy. IEEE Trans Very Large Scale Integr Syst 12(5):497–510

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Rights and permissions

About this article

Cite this article

Gowdar, C.V., Parameshwara, M.C. Lower-part approximate multi-bit adders for low-power DSP. Int. j. inf. tecnol. 14, 731–737 (2022). https://doi.org/10.1007/s41870-021-00849-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s41870-021-00849-x