Abstract

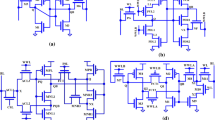

Static random-access memories (SRAMs), which are the most ubiquitous in modern system-on-chips, suffer from high power dissipation and poor stability in advanced complementary metal–oxide–semiconductor (CMOS) technology due to continuous learning, which leads to increased short-channel effects (SCEs), thereby, leading to use of new nano-devices. The fin-shaped field-effect transistor (FinFET) with lots of impressive attributes like mitigated SCEs is an efficient replacement for CMOS to overcome the aforementioned concerns. In this regard, this paper aims to explore a novel single-bitline 9-transistor (SB9T) SRAM with bit-interleaving capability appropriate for low-power near-threshold operation in 7-nm FinFET technology. The relative performance of the proposed SB9T is estimated by comparing it with other seven contemporary SRAMs such as conventional 6 T, write–read enhanced 8T (WRE8T), transmission gate read decoupled 9T (TGRD9T), one-sided Schmitt-trigger 9T (ST9T), data-independent read port 10T (DIRP10T), PMOS-PMOS-NMOS-based cell core 10T (PPN10T), and feedback-cutting 11 T (FC11T) at a near-threshold supply voltage of 0.5 V. Simulation results inferred that the SB9T offers 1.77 × /1.36 × and 2.35 × /13.13 × /1.30 × improvement in read stability and writability compared to WRE8T/ST9T and 6 T/DIRP10T/PPN10T, respectively. Furthermore, it consumes the best dynamic read power, which is at least 1.50 × , the third-best dynamic write power, and the second-best static power. The proposed SB9T SRAM offers 2.89 × /2.37 × improvement in dynamic write power/static power, at the expense of 1.742 × area overhead, compared to 6 T.

Similar content being viewed by others

Data availability

The data that support the finding of this study are available from the corresponding author upon reasonable request.

References

Abbasian, E.; Izadinasab, F.; Gholipour, M.: A reliable low standby power 10T SRAM cell with expanded static noise margins. IEEE Trans Circuits Syst I Regular Paper, 69(4), 1606–1616 (2022)

Ahmad, S.; Alam, N.; Hasan, M.: Pseudo-differential multi-cell upset immune robust SRAM cell for ultra-low power applications. AEU-Int. J. Electron. Commun. 83, 366–375 (2018)

Sharma, D.; Birla, S.: 10T FinFET based SRAM cell with improved stability for low power applications. Int. J. Electron. pp. 1–16, (2021)

Abbasian, E.; Gholipour, M.; Birla, S.: Ultra-low-power and stable 10-nm FinFET 10T sub-threshold SRAM, Microelectron. J. 123, 105427 (2022)

Eslami, N.; Ebrahimi, B.; Shakouri, E.; Najafi, D.: A single-ended low leakage and low voltage 10T SRAM cell with high yield. Analog Integr. Circ. Sig. Process 105, 263–274 (2020)

Turi, M.A.; Delgado-Frias, J.G.: Effective low leakage 6T and 8T FinFET SRAMs: using cells with reverse-biased FinFETs, near-threshold operation, and power gating. IEEE Trans. Circuits Syst. II Express Briefs 67(4), 765–769 (2019)

Oh, T.W.; Jeong, H.; Kang, K.; Park, J.; Yang, Y.; Jung, S.-O.: Power-gated 9T SRAM cell for low-energy operation. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 25(3), 1183–1187 (2016)

Abbasian, E.; Gholipour, M.: 'A low‐leakage single‐bitline 9T SRAM cell with read‐disturbance removal and high writability for low‐power biomedical applications. Int. J. Circuit Theory Appl. (2022)

Pasandi, G.; Fakhraie, S.M.: An 8T low-voltage and low-leakage half-selection disturb-free SRAM using bulk-CMOS and FinFETs. IEEE Trans. Electron Devices 61, 2357–2363 (2014)

Pasandi, G.; Fakhraie, S.M.: A 256-kb 9T near-threshold SRAM with 1k cells per bitline and enhanced write and read operations. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 23(11), 2438–2446 (2014)

Mahmoodi, E.; Gholipour, M.: Design space exploration of low-power flip-flops in FinFET technology. Integration 75, 52–62 (2020)

Ahmad, S.; Iqbal, B.; Alam, N.; Hasan, M.: Low leakage fully half-select-free robust SRAM cells with BTI reliability analysis. IEEE Trans. Device Mater. Reliab. 18(3), 337–349 (2018)

Abbasian, E.; Mani, E.; Gholipour, M.; Karamimanesh, M.; Sahid, M.; Zaidi, A.: A schmitt-trigger-based low-voltage 11T SRAM cell for low-leakage in 7-nm FinFET technology. Circuits, Syst. Signal Process. (2022)

Abbasian, E.; Gholipour, M.: Single-ended half-select disturb-free 11T static random access memory cell for reliable and low power applications. Int. J. Circ Theor. Appl. 49(4), 970–989 (2021)

Abbasian, E.; Gholipour, M.; Izadinasab, F.: Performance evaluation of GNRFET and TMDFET devices in static random access memory cells design. Int. J. Circuit Theory Appl. 49(11), 3630–3652 (2021)

Abbasian, E.; Gholipour, M.: Design of a schmitt-trigger-based 7T SRAM cell for variation resilient low-energy consumption and reliable internet of things applications. AEU-Int. J. Electron. Commun. 138, 153899 (2021)

Gupta, S.; Gupta, K.; Calhoun, B.H.; Pandey, N.: Low-power near-threshold 10T SRAM bit cells with enhanced data-independent read port leakage for array augmentation in 32-nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 66(3), 978–988 (2018)

Izadinasab, F.; Gholipour, M.: Half-select disturb-free single-ended 9-transistor SRAM cell with bit-interleaving scheme in TMDFET technology. Microelectron. J. 113, 105100 (2021)

Ensan, S.S.; Moaiyeri, M.H.; Hessabi, S.: A robust and low-power near-threshold SRAM in 10-nm FinFET technology. Analog Integr. Circ. Sig. Process 94, 497–506 (2018)

Wang, B.; Nguyen, T.Q.; Do, A.T.; Zhou, J.; Je, M.; Kim, T.T.-H.: Design of an ultra-low voltage 9T SRAM with equalized bitline leakage and CAM-assisted energy efficiency improvement. IEEE Trans. Circuits Syst. I Regul. Pap. 62(2), 441–448 (2014)

Pal, S.; Islam, A.: 9-T SRAM cell for reliable ultralow-power applications and solving multibit soft-error issue. IEEE Trans. Device Mater. Reliab. 16(2), 172–182 (2016)

Sachdeva, A.; Tomar, V.: Design of multi-cell upset immune single-end SRAM for low power applications. AEU-Int. J. Electron. Commun. 128, 153516 (2021)

Ensan, S.S.; Moaiyeri, M.H.; Moghaddam, M.; Hessabi, S.: A low-power single-ended SRAM in FinFET technology. AEU-Int. J. Electron. Commun. 99, 361–368 (2019)

Karamimanesh, M.; Abiri, E.; Hassanli, K.; Salehi, M.R.; Darabi, A.: A robust and write bit-line free sub-threshold 12T-SRAM for ultra low power applications in 14 nm FinFET technology. Microelectron. J. 118, 105185 (2021)

Karamimanesh, M.; Abiri, E.; Hassanli, K.; Salehi, M.R.; Darabi, A.: A write bit-line free sub-threshold SRAM cell with fully half-select free feature and high reliability for ultra-low power applications. AEU-Int. J. Electron. Commu. 145, 154075 (2021)

Salahuddin, S.; Jiao, H.; Kursun, V.: A novel 6T SRAM cell with asymmetrically gate underlap engineered FinFETs for enhanced read data stability and write ability. In: International Symposium on Quality Electronic Design (ISQED), pp. 353–358 (2013)

Cho, K.; Park, J.; Oh, T.W.; Jung, S.-O.: One-sided schmitt-trigger-based 9T SRAM cell for near-threshold operation. IEEE Trans. Circuits Syst. I Regul. Pap. 67(5), 1551–1561 (2020)

Sanvale, P.; Gupta, N.; Neema, V.; Shah, A.P.; Vishvakarma, S.K.: An improved read-assist energy efficient single ended PPN based 10T SRAM cell for wireless sensor network. Microelectron. J. 92, 104611 (2019)

Salahuddin, S.M.; Chan, M.: Eight-FinFET fully differential SRAM cell with enhanced read and write voltage margins. IEEE Trans. Electron Devices 62(6), 2014–2021 (2015)

Clark, L.T.; Vashishtha, V.; Shifren, L.; Gujja, A.; Sinha, S.; Cline, B.; et al.: ASAP7: A 7-nm finFET predictive process design kit. Microelectron. J. 53, 105–115 (2016)

Tu, M.-H.; Lin, J.-Y.; Tsai, M.-C.; Jou, S.-J.; Chuang, C.-T.: Single-ended subthreshold SRAM with asymmetrical write/read-assist. IEEE Trans. Circuits Syst. I Regul. Pap. 57(12), 3039–3047 (2010)

Abbasian, E.; Gholipour, M.: A variation-aware design for storage cells using Schottky-barrier-type GNRFETs. J. Comput. Electron. 19, 987–1001 (2020)

He, Y.; Zhang, J.; Wu, X.; Si, X.; Zhen, S.; Zhang, B.: A half-select disturb-free 11T SRAM cell with built-in write/read-assist scheme for ultralow-voltage operations. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 27(10), 2344–2353 (2019)

Abbasian, E.; Birla, S.; Gholipour, M.: A Comprehensive Analysis of Different SRAM Cell Topologies in 7-nm FinFET Technology," Silicon, (2021)

Acknowledgements

Authors acknowledge the funding support of the Babol Noshirvani University of Technology through grant program No. BNUT/389023/1400. Also, they acknowledge the support and lab facility provided by the Department of ECE, Manipal University Jaipur, Jaipur, India.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Abbasian, E., Gholipour, M. & Birla, S. A Single-Bitline 9T SRAM for Low-Power Near-Threshold Operation in FinFET Technology. Arab J Sci Eng 47, 14543–14559 (2022). https://doi.org/10.1007/s13369-022-06821-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13369-022-06821-6