Abstract

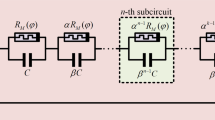

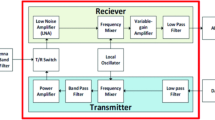

A second-order multi-bit \(\Sigma \Delta \) modulator facilitating the usage of a two-step flash analog-to-digital converter (ADC) as an internal quantizer is presented. A digital assisted low-resolution feedback digital-to-analog converter (DAC) is introduced containing digital sigma-delta modulators (DSDMs) to reduce the number of levels in the feedback DAC alleviating dynamic element matching requirements. Two-step flash ADC as an internal quantizer in a \(\Sigma \Delta \) modulator provides higher resolution; however, the delay in the two-step ADC can introduce instability in the \(\Sigma \Delta \) modulator loop. In the proposed architecture, the fast processing of the digital integrator of DSDM in the feedback path compensates the latency of the two-step flash ADC. Therefore, this architecture provides more than 6 bits of resolution in the internal quantizer. The implementation of an extra DSDM in the outermost feedback path relaxes the matching requirement of the analog and digital integrators. The effectiveness of the proposed structure is demonstrated by the study of nonlinearities of the analog integrators.

Similar content being viewed by others

References

Jeong, D.; Yoo, C.: A 4-MHz bandwidth continuous-time sigma-delta modulator with stochastic quantizer and digital accumulator. IEEE Trans. Circuits Syst. II Exp. Briefs 66(7), 1124–1128 (2019)

He, L.; et al.: A multibit deltasigma modulator with double noise-shaped segmentation. IEEE Trans. Circuits Syst. II Exp. Briefs 62(3), 241–245 (2015)

Yan, H.; He, L.; Ye, Y.; Lin, F.: A second-order continuous-time delta-sigma modulator with double self noise coupling. Analog Integr. Circuits Sig. Process 99(2), 251–259 (2019)

Rezapour, A.; Shamsi, H.: Digital noise coupled MASH delta-sigma modulator. IEEE Trans. Circuits Syst. II Exp. Briefs 66(1), 41–45 (2019)

Colodro, F.; Torralba, A.; Mora, J.L.: Digital noise-shaping of residues in dual-quantization sigma-delta modulators. IEEE Trans. Circuits Syst. I Reg. Pap. 51(2), 225–232 (2004)

Wu, J.; Zhang, Z.; Subramoniam, R.; Maloberti, F.: A 107.4 dB SNR multi-bit sigma delta ADC with 1-PPM THD at -0.12 dB from full scale input. IEEE J. Solid State Circuits 44(11), 3060–3066 (2009)

Irfansyah, A.N.; Lehmann, T.; Jenkins, J.; Tong, T.; Hamilton, T.J.: A resistive DAC for a multi-stage sigma-delta modulator DAC with dynamic element matching. Analog Integr. Circuits Signal Process. 98(1), 109–123 (2019)

Sharifi, L.; Hashemipour, O.: Multi-bit quantizer delta-sigma modulator with the feedback DAC mismatch error shaping. In: 27th Iranian Conference on Electrical Engineering (ICEE) IEEE, Iran, pp. 209–213 (2019)

Yu, J.; Maloberti, F.: A low-power multi-bit \(\Sigma \Delta \) modulator in 90-nm digital CMOS without DEM. IEEE J. Solid State Circuits 40(12), 2428–2436 (2005)

Liu, Q.; Edward, A.; Zhou, D.; Silva-Martinez, J.: A continuous-time MASH 1-1-1 delta-sigma modulator With FIR DAC and encoder-embedded loop-unrolling quantizer in 40-nm CMOS. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 26(4), 756–767 (2018)

Dey, S.; Reddy, K.; Mayaram, K.; Fiez, T.S.: A 50 MHz BW 76.1 dB DR two-stage continuous-time delta-sigma modulator with VCO quantizer nonlinearity cancellation. IEEE J. Solid State Circuits 53(3), 799–813 (2018)

Jain, A.; Pavan, S.: Continuous-time delta-sigma modulators with time-interleaved FIR feedback. IEEE Trans. Circuits Syst. I Reg. Pap. 65(2), 434–443 (2018)

Zhang, Y.; He, X.; Pun, K.: An extremely linear multi-level DAC for continuous-time delta-sigma modulators. IEEE Trans. Circuits Syst. II Exp. Briefs 66(3), 367–371 (2019)

Zhang, Y.; Basak, D.; Pun, K.: A highly linear multi-level SC DAC in a power-efficient Gm-C continuous-time delta-sigma modulator. IEEE Trans. Circuits Syst. I Reg. Pap. 66(12), 4592–4605 (2019)

Pakniat, H.; Yavari, M.: A \(\Sigma \Delta \)-FIR-DAC for multi-bit \(\Sigma \Delta \) modulators. IEEE Trans. Circuits Syst. I Reg. Pap. 60(9), 2321–2332 (2013)

Sharifi, L.; Hashemipour, O.: Mismatch error shaping of DAC unit elements in multi-bit \(\Delta \Sigma \) modulators using a novel unified ADC/DAC. Turk. J. Electr. Eng. Comput. Sci. (2020) (accepted)

Leslie, T.C.; Singh, B.: An improved sigma-delta modulator architecture. In: Proceedings of IEEE International Symposium on Circuits Systems, vol. 1. New Orleans, LA, USA, pp. 372–375 (1990)

Wang, Q.-Q.; Ge, B.-J.; Feng, X.-X.; Wang, X.-A.: Digital noise shaping multibit delta-sigma modulator. Electron. Lett. 46(16), 1110–1111 (2010)

He, L.; et al.: Digital noise-coupling technique for DeltaSigma modulators with segmented quantization. IEEE Trans. Circuits Syst. II Exp. Briefs 61(6), 403–407 (2014)

Tsai, H.; Lo, C.; Ho, C.; Lin, Y.: A 64-fJ/conv.-step continuous-time \(\Sigma \Delta \) modulator in 40-nm CMOS using asynchronous SAR quantizer and digital \(\Delta \Sigma \) truncator. IEEE J. Solid State Circuits 48(11), 2637–2648 (2013)

He, T.; Zhang, Y.; Temes, G.C.: Digital excess loop delay compensation technique with embedded truncator for continuous-time delta-sigma modulators. Electron. Lett. 52(1), 20–21 (2016)

Weng, C.; Lin, Y.; Lin, T.: A 1-V 5-MHz bandwidth 68.3-dB SNDR continuous-time delta-sigma modulator with a feedback-assisted quantizer. IEEE Trans. Circuits Syst. I Reg. Pap. 64(5), 1085–1093 (2017)

Polineni, S.; Bhat, M.S.; Rajan, A.: A 10-bit differential ultra-low-power SAR ADC with an enhanced MSB capacitor-split switching technique. Arab. J. Sci. Eng. 44(3), 2345–2353 (2019)

Acknowledgements

The authors of the manuscript thankfully acknowledge the significant help and collaborations of Prof. Franco Maloberti and Prof. Edoardo Bonizzoni, Integrated Microsystem (IMS) Laboratory, Department of Electrical, Computer, and Biomedical Engineering, University of Pavia, Italy. We wish to thank them for their invaluable comments in investigating the idea of the manuscript, its organization and the simulation process.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Sharifi, L., Hashemipour, O. Digital Assisted Truncation Noise Shaping Technique for Multi-bit \(\Sigma \Delta \) Modulators. Arab J Sci Eng 46, 1279–1286 (2021). https://doi.org/10.1007/s13369-020-05055-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13369-020-05055-8