Abstract

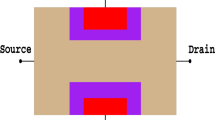

Two-dimensional (2D) analytical model for the subthreshold characteristics like Surface potential, threshold voltage, subthreshold current and swing of uniformly doped, high-k gate stack double-gate (DG) metal-oxide-semiconductor field-effect transistors (MOSFETs) is proposed in this paper. The minimum surface potential obtained by solving the 2D Poisson’s equation using evanescent mode analysis has been utilized to model the threshold voltage, subthreshold current and subthreshold swing. The effects of various parameters on these parameters have also been presented. The results show excellent matching with the numerical simulation data obtained by ATLAS™, a 2D device simulator from SILVACO.

Similar content being viewed by others

Data Availability

Yes the data and material is available.

References

Mohapatra SK, Pradhan KP, Artola L, Sahu PK (2015) Estimation of analog/RF figures-of-merit using device design engineering in gate stack double gate MOSFET. Mater Sci Semicond Process 31:455–462. https://doi.org/10.1016/j.mssp.2014.12.026

Toan HLM, Maity SK (2021) Physics based compact modeling of symmetric double gate MOS transistors with high mobility III-V channel material. Superlattice Microst 155:106925. https://doi.org/10.1016/j.spmi.2021.106925

Roy R, Chowdhury J, Das JK (2018) Analytical study of double gate MOSFET: a design and performance perspective. Proc 2nd Int Conf Inven Syst control ICISC 2018 625–634. https://doi.org/10.1109/ICISC.2018.8398875

Chaudhary R, Mukhiya R, Patel GS, et al (2018) Simulation of MOSFET with different dielectric films. Proc - 2nd Int Conf Intell circuits Syst ICICS 2018 177–183. https://doi.org/10.1109/ICICS.2018.00044

Lucky A, Singh BK, Shweta T, Mishra RA (2016) “Short Channel effects (SCEs) characterization of underlapped dual-K spacer in dual-metal gate FinFET device.” IEEE International Conference on Control, Computing, Communication and Materials (ICCCCM) :1–6, https://doi.org/10.1109/ICCCCM.2016.7918265.

Tripathi SL (2020) Low power high performance multi-gate Mosfet structures Think India Journal. 16:209–219.

Ratnesh RK, Goel A, Kaushik G, Garg H, Chandan, Singh M, Prasad B (2021) Advancement and challenges in MOSFET scaling. Mater Sci Semicond Process 134:106002. https://doi.org/10.1016/j.mssp.2021.106002

Parija SK, Swain SK, Adak S, Biswal SM, Dutta P (2021) Comparison study of DG-MOSFET with and without gate stack configuration for biosensor applications. Silicon. https://doi.org/10.1007/s12633-021-01118-z

Parija SK, Swain SK, Biswal SM, Adak S, Dutta P (2022) Performance analysis of gate stack DG-MOSFET for biosensor applications. Silicon. https://doi.org/10.1007/s12633-021-01622-2

Monisha A, RSS R (2014) Performance and characteristic analysis of double gate MOSFET over single gate MOSFET. Int Conf Electron Commun Syst ICECS 2014:12–15. https://doi.org/10.1109/ECS.2014.6892627

Gowthaman N, Srivastava VM (2021) Analysis of Nanometer-Scale n-Type Double-Gate (DG) MOSFETs Using High- Dielectrics for High-Speed Applications. Proc Int Spring Semin Electron Technol 2021-May:7–11. https://doi.org/10.1109/ISSE51996.2021.9467619

Das S, Choudhury A, Ghosh S et al (2017) Parameter modeling of linearly doped double gate MOSFET with high-k dielectrics. Proc 2nd Int Conf 2017 devices Integr circuit. DevIC 2017:136–140. https://doi.org/10.1109/DEVIC.2017.8073922

Kiran Kumar R, Shiyamala S (2020) A 2-D analytical modeling of dual work function metal gate MOSFET using high-K gate dielectric with enhanced RF/analog performance for low power applications. Silicon 12:2065–2072. https://doi.org/10.1007/s12633-019-00290-7

Hobbs CC, Fonseca LRC, Knizhnik A, Dhandapani V, Samavedam SB, Taylor WJ, Grant JM, Dip LG, Triyoso DH, Hegde RI, Gilmer DC, Garcia R, Roan D, Lovejoy ML, Rai RS, Hebert EA, Tseng HH, Anderson SGH, White BE, Tobin PJ (2004) Fermi-level pinning at the polysilicon/metal oxide interface - part I. IEEE Trans Electron Devices 51:971–977. https://doi.org/10.1109/TED.2004.829513

Swain SK, Das SK, Adak S (2020) Study of linearity performance of Graded Channel gate stacks double gate MOSFET with respect to high-K oxide thickness. Silicon 12:1567–1574. https://doi.org/10.1007/s12633-019-00257-8

Kumar Suhag A, Sharma R (2017) Design and simulation of nanoscale double gate MOSFET using high K material and ballistic transport method. Mater Today Proc 4:10412–10416. https://doi.org/10.1016/j.matpr.2017.06.390

Acknowledgements

The author would like to thank Prof. Satyabrata Jit, Professor (HAG) Indian Institute of Technology, Varanasi, for needful support.

Funding

Not Applicable.

Author information

Authors and Affiliations

Contributions

It is single author paper.

Corresponding author

Ethics declarations

Ethics Approval

The manuscript follows all the ethical standards, including plagiarism.

Consent for Publication

Yes

Consent to Participate

Yes

Conflict of Interests

No conflicts of interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Goel, E. Impact of High-K Gate Stack on Subthreshold Performance of Double-Gate (DG) MOSFETs. Silicon 14, 11539–11544 (2022). https://doi.org/10.1007/s12633-022-01891-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-022-01891-5