Abstract

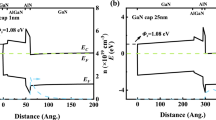

In this work, with the help of 2-D device simulation and 1-D Landau-Khalatnikov model for ferroelectric material, we have studied the scaling effect of ferroelectric material as a gate dielectric on the sub-threshold characteristics of ultra-thin body on insulator MOS transistor. The device performance is investigated for the MOS device with high mobility III-V material (InGaAs) as a channel material and its performance is compared with silicon channel based MOS device. The negative capacitance characteristics of the dielectric material is modeled by charge-dependent 1-D L-K equation related to ferroelectric polarization model. With an increase in thickness of ferroelectric material, improvement in sub-threshold characteristics such as drain induced barrier lowering coefficient and sub-threshold swing is observed. At higher ferroelectric layer thickness, hysteresis effect in the device characteristics also observed. Internal gate voltage amplification found to be proportional with the thickness of ferroelectric region for both device. With optimum ferroelectric layer thickness, device with high mobility InGaAs channel shows significant improvement in electrostatic integrity which is comparable to silicon channel based MOS device.

Similar content being viewed by others

References

del Alamo JA (2011) Nanometre-scale electronics with III-V compound semiconductors. Nature 479:317–323. https://doi.org/10.1038/nature10677

Yu C, Su P (2014) Built-in effective body-bias effect in ultra-thin-body hetero-channel III-v-on-insulator n-MOSFETs. IEEE Electron Dev Lett 35(8):823–825. https://doi.org/10.1109/LED.2014.2328628

Maity SK, Pandit S (2017) Study of G-S/D underlap for enhanced analog performance and rf/circuit analysis of UTB InAs-OI-Si MOSFET using NQS small signal model. Superlattices Microstruct 101:362–372. https://doi.org/10.1016/j.spmi.2016.11.053

Yokoyama M, Iida R, Kim S, Taoka N, Urabe Y, Yasuda T, Takagi H, Yamada H, Fukuhara N, Hata M, Sugiyama M, Nakano Y, Takenaka M, Takagi S (2010) Extremely-thin-body InGaAs-on-insulator MOSFETs on Si fabricated by direct wafer bonding. In: IEDM Tech. Dig., pp 3.1.1–3.1.4

Yokoyama M, et al. (2013) Formation of III-V-on-insulator structures on Si by direct wafer bonding. Semicond Sci Technol 28:1–10

Kim S, Yokoyama M, Taoka N, Nakane R, Yasuda T, Ichikawa O, Fukuhara N, Hata M, Takenaka M, Takagi S (2013) Sub-60-nm extremely thin body In1−xGaxAs -on-insulator MOSFETs on Si with Ni-InGaAs metal S/D and MOS interface buffer engineering and its scalability. IEEE Trans Electron Dev 60(8):2512–2517. https://doi.org/10.1109/TED.2013.2270558

Lin J, Antoniadis DA, del Alamo JA (2015) Impact of intrinsic channel scaling on ingaas quantum-well mosfets. IEEE Trans Electron Dev 62(11):3470–3476. https://doi.org/10.1109/TED.2015.2444835

Alam MA, Si M, Ye PD (2019) A critical review of recent progress on negative capacitance field-effect transistors. Appl Phys Let 114(9):090401. https://doi.org/10.1063/1.5092684

Amrouch H, Pahwa G, Gaidhane AD, Henkel J, Chauhan YS (2018) Negative capacitance transistor to address the fundamental limitations in technology scaling: processor performance. IEEE Access 6:52754–52765. https://doi.org/10.1109/ACCESS.2018.2870916

Saeidi A, Jazaeri F, Bellando F, Stolichnov I, Enz CC, Ionescu AM (2017) Negative capacitance field effect transistors; capacitance matching and non-hysteretic operation. In: 2017 47th European solid-state device research conference (ESSDERC), pp 78–81. https://doi.org/10.1109/ESSDERC.2017.8066596

Lee MH, Chen P, Liu C, Chu K, Cheng C, Xie M, Liu S, Lee J, Huang S, Liao M, Tang M, Li K, Chen M (2015) Prospects for ferroelectric HfZrOx FETs with experimentally CET= 0.98nm, SSfor= 42mV/dec, SSrev= 28mV/dec, switch-off < 0.2V, and hysteresis-free strategies.. In: 2015 IEEE International electron devices meeting (IEDM), pp 22.5.1–22.5.4, DOI https://doi.org/10.1109/IEDM.2015.7409759

Muller J, Schroder U, Boscke TS, Muller I, Bottger U, Wilde L, Sundqvist J, Lemberger M, Kucher P, Mikolajick T, Frey L (2011) Ferroelectricity in yttrium-doped hafnium oxide. J Appl Phys 110 (11):114113. https://doi.org/10.1063/1.3667205

Mueller S, Mueller J, Singh A, Riedel S, Sundqvist J, Schroeder U, Mikolajick T (2012) Incipient ferroelectricity in Al-Doped HfO2 thin films. Adv Funct Mater 22(11):2412–2417. https://onlinelibrary.wiley.com/doi/abs/10.1002/adfm.201103119

Hoffmann M, Pešić M, Chatterjee K, Khan AI, Salahuddin S, Slesazeck S, Schroeder U, Mikolajick T (2016) Direct observation of negative capacitance in polycrystalline ferroelectric HfO2, vol 26. https://onlinelibrary.wiley.com/doi/abs/10.1002/adfm.201602869

Salahuddin S, Datta S (2008) Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett 8(2):405–410. https://doi.org/10.1021/nl071804g, pMID: 18052402

Rabe K, Ahn C, Triscone JM (eds) (2007) Physics of ferroelectrics: a modern perspective. Springer, New York

Salvatore GA, Bouvet D, Ionescu AM (2008) Demonstration of subthrehold swing smaller than 60mV/decade in Fe-FET with P(VDF-TrFE)/SiO2 gate stack. In: 2008 IEEE International electron devices meeting, pp 1–4, DOI https://doi.org/10.1109/IEDM.2008.4796642

Kobayashi M, Ueyama N, Jang K, Hiramoto T (2016) Experimental study on polarization-limited operation speed of negative capacitance FET with ferroelectric HfO2. In: IEDM Tech. Dig, pp 12.3.1–12.3.4, DOI https://doi.org/10.1109/IEDM.2016.7838402

Khan AI, Radhakrishna U, Salahuddin S, Antoniadis D (2017) Work function engineering for performance improvement in leaky negative capacitance FETs. IEEE Electron Device Lett 38(9):1335–1338. https://doi.org/10.1109/LED.2017.2733382

Yeung CW, Khan AI, Sarker A, Salahuddin S, Hu C (2013) Low power negative capacitance FETs for future quantum-well body technology. In: 2013 International symposium on VLSI technology, systems and application (VLSI-TSA), pp 1–2, DOI https://doi.org/10.1109/VLSI-TSA.2013.6545648

Saeidi A, Jazaeri F, Stolichnov I, Ionescu AM (2016) Double-gate negative-capacitance MOSFET With PZT gate-stack on ultra thin body SOI: an experimentally calibrated simulation study of device performance. IEEE Trans Electron Dev 63(12):4678–4684. https://doi.org/10.1109/TED.2016.2616035

Pahwa G, Dutta T, Agarwal A, Chauhan YS (2018) Physical insights on negative capacitance transistors in nonhysteresis and hysteresis regimes: Mfmis versus mfis structures. IEEE Trans Electron Dev 65(3):867–873. https://doi.org/10.1109/TED.2018.2794499

Pahwa G, Agarwal A, Chauhan YS (2018) Numerical investigation of short-channel effects in negative capacitance MFIS and MFMIS transistors: subthreshold behavior. IEEE Trans Electron Dev 65(11):5130–5136. https://doi.org/10.1109/TED.2018.2870519

Chang CY, Endo K, Kato K, Takenaka M, Takagi S (2017) Modulation of sub-threshold properties of InGaAs MOSFETs by La2O3 gate dielectrics. AIP Adv 7(9):095215. https://doi.org/10.1063/1.4999958

Kobayashi M, Hiramoto T (2015) Device design guideline for steep slope ferroelectric FET using negative capacitance in sub-0.2V operation: operation speed, material requirement and energy efficiency. In: 2015 Symposium on VLSI technology (VLSI technology), pp T212–T213, DOI https://doi.org/10.1109/VLSIT.2015.7223678

Boscke TS, Muller J, Brauhaus D, Schroder U, Bottger U (2011) Ferroelectricity in hafnium oxide: CMOS compatible ferroelectric field effect transistors. In: 2011 International electron devices meeting, pp 24.5.1–24.5.4, DOI https://doi.org/10.1109/IEDM.2011.6131606

Sentaurus TCAD (2016) Sentaurus TCAD manuals. V.2016 edn

Vegard L (1921) Die konstitution der mischkristalle und die raumfüllung der atome. Zeitschrift für Physik 5(1):17–26. https://doi.org/10.1007/BF01349680

NSM Archive (2019) Ioffe Institute of the Russian Academy of Sciences. www.ioffe.ru/SVA/NSM/semicond/GaInAs

Caughey D, Thomas R (1967) Carrier mobilities in silicon empirically related to doping and field. Proc Inst Electr Eng 55(12):2192–2193. https://doi.org/10.1109/PROC.1967.6123

Canali C, Majni G, Minder R, Ottaviani G (1975) Electron and hole drift velocity measurements in silicon and their empirical relation to electric field and temperature. IEEE Trans Electron Dev 22(11):1045–1047. https://doi.org/10.1109/T-ED.1975.18267

Lombardi C, Manzini S, Saporito A, Vanzi M (1988) A physically based mobility model for numerical simulation of nonplanar devices. IEEE Trans Comput-Aided Des Integrated Circ Syst 7(11):1164–1171. https://doi.org/10.1109/43.9186

Ancona M, Iafrate GJ (1989) Quantum correction to the equation of state of an electron gas in a semiconductor. Phys Rev B 39(13):9536–9540

Maity SK, Pandit S (2015) Study of analog and RF performance of UTB-OI-Si substrate MOS transistor using buffered InGaAs and Silicon channel. In: 2015 6th International conference on computers and devices for communication (CODEC), pp 1–4, DOI https://doi.org/10.1109/CODEC.2015.7893193

Maity SK, Pandit S (2017) Effects of BOX engineering on analogue/RF, and circuit performance of InGaAs-OI-Si MOSFET. Int J Electron 104(11):1777–1794. https://doi.org/10.1080/00207217.2017.1312715

Lee HP, Yu CL, You WX, Su P (2017) Investigation and comparison of design space for ultra-thin-body GeOI/SOI negative capacitance FETs. In: 2017 International symposium on VLSI technology, systems and application (VLSI-TSA), pp 1–2, DOI https://doi.org/10.1109/VLSI-TSA.2017.7942460

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Maity, S.K. Sub-Threshold Performance Assessment of Ultra-Thin Body InGaAs-on Insulator Negative Capacitance MOS Transistor. Silicon 12, 2681–2688 (2020). https://doi.org/10.1007/s12633-019-00364-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-019-00364-6