Abstract

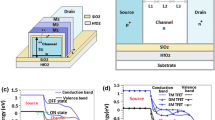

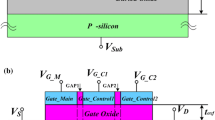

In this article, a three-dimensional model of Tri-gate Tunnel Filed effect transistors (TFET) with different gate materials is proposed. Analysis and comparison of various structures such as single material gate, double material gate and triple material gate of a Tri-gate TFET is performed with respect to both DC and AC characteristics. Various electrical parameters that define the performance of a semiconductor device are verified using Silvaco TCAD Simulation results. Parameters analyzed in this work include surface potential, lateral electric field, total electric field along the channel, drain current, transconductance and output conductance of single material, double material and triple material Tri-gate TFETs. The comparative performance analysis shows a better DC and AC performance for Triple Material Tri-gate TFET (TMTGTFET) in comparison to single material and double material Tri-gate devices. It could be inferred that short channel effects are considerably reduced in a gate engineered Tri-Gate TFET structure and it also shows remarkable improvement in ON current as the current increases 45% for TMTGTFET when compared to a SMTG TFET. To improve the TMTGTFET performance, different dielectric materials are employed for device characteristics.

Similar content being viewed by others

References

Gholizadeh M, Hosseini SE (2014) A 2-D Analytical Model for Double-Gate Tunnel FETs, IEEE Trans. on Electron Devices, vol. 61, no. 5

Sharma A, Akkala AG, Kulkarni JP, Roy K (2016) Source-under lapped GaSb–InAs TFETs with applications to gain cell embedded DRAMs. IEEE Trans Electron Devices 63(6):2563–2569

Usha C, Vimala P (2018) Analytical drain current model for fully depleted surrounding gate TFET. J Nano Res 55:75–81

Vimala P (2018) Charge based quantization model for triple-gate FINFETS. J Nano Electron Phys 10(5):050151–050155

Gnani E, Gnudi A, Reggiani S, Baccarani G (2013) Drain-conductance optimization in nanowire TFETs by means of a physics-based analytical model. Solid State Electron 84:96–102

Wu J, Taur Y (2016) A continuous Semianalytic current model for DG and NW TFETs. IEEE Trans Electron Devices 63(2):841–847

Ionescu M, Riel H (2011) Tunnel field-effect transistors as energy efficient electronic switches. Nature 479(7373):329–337

Verhulst AS, Vandenberghe WG, Maex K, Groeseneken G (2007) Tunnel field-effect transistor without gate-drain overlap. Appl Phys Lett 91(5):053102–053105

Kumar S, Goel E, Singh K, Singh B, Singh PK, Baral K, Jit S (2017) 2-D analytical Modeling of the electrical characteristics of dual-material double gate TFETs with a SiO2/HfO2 stacked gate-oxide structure. IEEE trans electron devices 64(3):960–968

Mohammadi S, Khaveh HRT (2017) An analytical model for double-gate tunnel FETs considering the junctions depletion regions and the channel Mobile charge carriers. IEEE Trans Electron Devices 64(3):1268–1276

Pan A, Chui CO (2012) A quasi-analytical model for double-gate Tunneling field-effect transistors. IEEE Electron Device Lett 33(10):1468–1470

Vishnoi R, Kumar MJ (2014) Compact analytical model of dual material gate Tunneling field effect transistor using Interband Tunneling and channel transport. IEEE Trans Electron Devices 61:1936–1942

Vanitha P, Arun Samuel TS, Nirmal D (2019) A new 2 D mathematical modeling of surrounding gate triple material tunnel FET using halo engineering for enhanced drain current. AEU Int J Electron Commun 99:34–39

Toh EH, Wang GH, Samudra G, Yeo YC (2008) Device physics and design of germanium tunneling field-effect transistor with source and drain engineering for low power and high performance applications. J Appl Phys 103(10):104504–104504-5

Komalavalli S, Arun Samuel TS, Vimala P (2019) Performance analysis of triple material tri gate TFET using 3D analytical modelling and TCAD simulation. AEU Int J Electron Commun 110:152842

Verhulst AS, Sorée B, Leonelli D, Vandenberghe WG, Groeseneken G (2010) Modeling the single-gate, double-gate, and gate-all around tunnel field-effect transistor. J Appl Phys 107:024518

Beneventi GB, Gnani E, Gnudi A, Reggiani S, Baccarani G (2014) Dual-metal-gate InAs tunnel FET with enhanced turn-on steepness and high ON-current. IEEE Trans Electron Devices 61(3):776–784

Vimala P, Nithin Kumar NR (2019) Comparative analysis of various parameters of tri-gate MOSFET with high-K spacer. J Nano Res 56:119–130

Ghanatian H, Hosseini SE (2016) Analytical modeling of subthreshold swing in undoped trigate SOI MOSFETs, J Comput Electron, pp.508–515

Marin EG, Ruiz FG, Godoy A, Tienda-Luna IM, Blanque CM, Gámiz F (2015) Impact of the Back-Gate Biasing on Trigate MOSFET Electron Mobility, IEEE Transactions on Electron Devices, vol. 62, no. 1

Saha P, Sarkhel S, Banerjee P, Sarkar SK (2018) 3D Modeling based Performance Analysis of Gate Engineered Trigate SON TFET SiO2/HfO2stacked gate oxide, 2018 IEEE International Conference on Electronics, Computing and Communication Technologies (CONECCT), pp: 1–4

Silvaco TCAD Atlas user manual

Acknowledgements

This research work is financially supported by Defense Research and Development Organization (DRDO), Government of India through the grant ERIP/ER/1504753/M/01/1629.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Vimala, P., Samuel, T.S.A. & Pandian, M.K. Performance Investigation of Gate Engineered tri-Gate SOI TFETs with Different High-K Dielectric Materials for Low Power Applications. Silicon 12, 1819–1829 (2020). https://doi.org/10.1007/s12633-019-00283-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-019-00283-6