Abstract

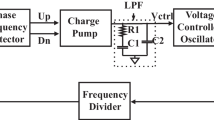

Single-event effects (SEEs) have been the primary concern in study of radiation effects since late 1970s with the discovery of soft errors in terrestrial and space environments. The interaction of a single ionized particle with electronic devices leads to SEEs. In this paper, single-event upset (SEU) on CMOS devices in designing of a voltage-controlled oscillator (VCO) is analysed. Further, mitigation approaches of SEU are also discussed. To observe the impact of radiation, a VCO was designed in Cadence Virtuoso, and GDSII file of one ring oscillator stage was extracted to incorporate the same design in Silvaco MaskViews. With the help of layer map information file, masks were identified and used to design the CMOS inverter structure file for simulation of SEU condition. The input parameters for SEU simulation were evaluated from linear energy transfer (LET) graph of heavy ion under space conditions. The current profile of CMOS inverter was extracted under influence of a high-energy particle with the help of LET graph of that particle. This current profile was applied to different nodes of VCO and upset conditions were identified. Further, the impact of upset conditions on lock stage of phase-locked loop (PLL) is discussed. Results show that the SEU has significant impact on the logic state of inverters used in ring oscillator stage compared with current starving/biasing stage. The current profile of CMOS device has strong dependence on the energy of ion, its track, angle of incidence and the material. When angle of incidence is very less (\(7^{\circ }-14^{\circ }\)) the channel will be occupied by a funnel of charge and it leads to the maximum degradation of device. This work shows that a device operating at high frequency is more susceptible to SEU. Triple modular redundancy (TMR) and Radiation Hardened By Design (RHBD) can be used to mitigate SEU. TMR consumes more power and is less accurate compared with the RHBD approach.

Similar content being viewed by others

References

Ramos A, Maestro J A and Reviriego P 2017 Characterizing a RISC-V SRAM-based FPGA implementation against Single Event Upsets using fault injection. Microelectron. Reliab. 78: 205–211

Messenger G C and Ash M S 1997 Single event phenomena. New York: Chapman and Hall

Iniewski K 2011 Radiation effects in semiconductor. New York: CRC Press

Turner J E 2007 Atoms, radiation, and radiation protection. New York: Wiley

Glenn F K 2000 Radiation detection and measurement. New York: Wiley

Dodd P E and Massengill L W 2003 Basic upset mechanisms and modeling of single event upset in digital microelectronics. IEEE Trans. Nuclear Sci. 50: 583–601

Tianiqi W, Xiao L and Zhou B 2015 Single-event upset prediction in SRAMs account for on-transistor sensitive volume. IEEE Trans. Nucl. Sci. 62(6): 3207–3215

Loveless T D, Massengill L W, Bhuva B L, Holman W T, Witulski A F and Boulghassoul Y 2007 Modeling and mitigating single-event transients in voltage-controlled oscillators. IEEE Trans. Nucl. Sci. 54(6): 2561–2567

Patil R K and Nasre V G 2010 A performance comparison of current starved VCO and source coupled VCO for PLL in 0.18 \(\upmu \)m CMOS process. Int. J. Eng. Innov. Technol. 1(2): 48–52

Prajapati A and Prajapati P P 2014 Analysis of current starved voltage controlled oscillator using 45 nm CMOS technology. Int. J. Eng. Innov. Technol. 3(3): 8076–8081

Kumar R, Karkala V and Garg R 2009 A radiation tolerant phase locked loop design for digital electronics. IEEE Trans. Nucl. Sci. 56(6): 505–510

Boulghassoul Y, Massengill L W and Bhuva B L 2005 Effects of technology scaling on SET sensitivity of RF CMOS voltage-controlled oscillators. IEEE Trans. Nucl. Sci. 52(6): 2246–2432

Cadence Virtuoso user manual [online]. http://www.cadence.com/products/cic/Pages/default.aspx

Baker R J, Harry W L and David E B 2000 CMOS circuit design, layout and simulation. In: IEEE Press series on microelectronics systems, pp. 355–361, 383–387

Silvaco Victory process user manual [online]. https://dynamic.silvaco.com/dynamicweb/jsp/downloads/DownloadManualsAction.do?req=silentmanuals&nm=victoryprocess

Silvaco Athena user manual [Online]. https://dynamic.silvaco.com/dynamicweb/jsp/downloads/DownloadManualsAction.do?req=silentmanuals&nm=athena

Silvaco Devedit user manual [online]. https://dynamic.silvaco.com/dynamicweb/jsp/downloads/DownloadManualsAction.do?req=silentmanuals&nm=devedit

Silvaco Devedit3D user manual [online]. https://dynamic.silvaco.com/dynamicweb/jsp/downloads/DownloadManualsAction.do?req=silentmanuals&nm=devedit3d

Silvaco Atlas user manual [online]. https://dynamic.silvaco.com/dynamicweb/jsp/downloads/DownloadManualsAction.do?req=silentmanuals&nm=atlas

Zajic V and Thieberger P 1999 Heavy ion linear energy transfer measurements during single event upset testing of electronic devices. IEEE Trans. Nucl. Sci. 46(1): 59–69

SRIM user manual [online]. http://www.srim.org/SRIM/Tutorials/Tutorials.htm

Jung S M and Roveda J M 2015 A radiation-hardened-by-design phase-locked loop using feedback voltage controlled oscillator. In: Proceedings of the 16th International Symposium on Quality Electron Design, Santa Clara, USA, pp. 103–106

Jain C P 2014 Structural and electrical properties of modified CMOS device under radiation environment in designing of voltage control oscillator (VCO). In: Proceedings of the International Conference on Innovative Applications of Computational Intelligence on Power, Energy and Controls with their Impact on Humanity (CIPECH14), KIET, Ghaziabad, India, pp. 379–383

Kauppila J S, Stenburg A L, Alles M L and Fransic A M 2009 A bias-dependent single-event compact model implemented into BSIM4 and a 90 nm CMOS process design kit. IEEE Trans. Nucl. Sci 56(6): 3152–3157

Shukla S, Gill S S, Kaur N, Jatana H S and Nehru V 2017 Comparative simulation analysis of process parameter variations in 20 nm triangular FinFET. Active and Passive Electronic Components, https://doi.org/10.1155/2017/5947819): 1–8

Acknowledgements

We acknowledge the Semi-Conductor Laboratory (Department of Space), Government of India, for their support provided.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Shukla, S., Gill, S.S., Jatana, H.S. et al. Modelling and mitigation of single-event upset in CMOS voltage-controlled oscillator. Sādhanā 43, 179 (2018). https://doi.org/10.1007/s12046-018-0945-4

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s12046-018-0945-4