Abstract

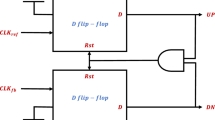

This paper introduces a modified design of Phase frequency detector (PFD) with reduced dead zone and improved charge pump (CP) with reduced current mismatch for a Phase Locked Loop (PLL). Three modified PFD circuits are proposed, designed, simulated, and the results are analyzed considering dead zone as a constraint. Design of pass transistor logic network plays a part in the diminution of the dead zone. Further, an improved design of CP is proposed to reduce current mismatch. It is achieved by placing the single ended differential amplifier in current–voltage feedback configuration which offers high output impedance. Simulations are performed using T-SPICE, implemented in IBM 0.13 µm technology under 1.3 V power supply. Results show that the modified PFD design has a dead zone of 0.3 ns and the current mismatch decrements to 0.1 µA in an improved CP design.

Similar content being viewed by others

References

AnushKannan N K, Dharani V A, Divya G, Esack N, Gokulraj M and Mangalam H 2013a Comparison and analysis of various PFD architecture for a phase locked loop design. In: Computational Intelligence and Computing Research (ICCIC), 2013 IEEE international conference on IEEE, pp. 105– 108

AnushKannan N K, Dharani V A, Divya G, Esack N, Gokulraj M and Mangalam H 2013b Design of various PFD and charge-pump architectures for a PLL-a survey. CiiT Int. J. Digital Signal Process. 5: 284–287

Bai Na, Ji Xincun, Guan Weiping and Lin Zhiting 2014 An improved charge pump with suppressed charge sharing effect. TELKOMNIKA Indonesian J. Electrical Eng. 12: 1245–1249

Best R E 2003 Introduction to PLLs, Phase-locked loops: Design, simulation and applications, Fifth Edition, Newyork, USA, Buch McGraw-Hill, chapter 1

Cheng Zhang and Marek Syrzycki 2010 Modifications of a dynamic-logic phase frequency detector for extended detection range. In: Circuits and systems (MWSCAS), 53rd IEEE international midwest symposium, IEEE pp 105–108

Dong-Keon Lee, Jeong-Kwang Lee and Hang-Geun Jeong 2010 A dual compensated charge pump with reduced current mismatch. In: Proceedings of the 4th WSEAS international conference on circuits, systems, signal and telecommunications, World Scientific and Engineering Academy and Society (WSEAS), pp. 109–112

Jae Hyung Noh and Hang Geun Jeong 2007 Charge-pump with a regulated cascode circuit for reducing current mismatch in PLLs. World Acad. Sci. Eng. Technol., Int. J. Electrical, Robotics, Electron. Commun. Eng. 1: 1001–1003

Jae-Shin Lee, Min-Sun Keel, Shin-I1 Lim and Suki Kim 2000 Charge pump with perfect current matching characteristics in phase-locked loops. Electron. Lett. 36: 1907–1908

Jayashree Nidagundi, Harish Desai, Shruti A and Gopal Manik 2013 Design and Implementation of Low Power Phase Frequency Detector (PFD) for PLL. Int. J. Sci. Eng. Technol. 2: 160–163

Khare K, Khare N, Deshpande P and Kulhade V 2008 Phase frequency detector of the delay locked loop at high frequency. In: Semiconductor electronics IEEE international conference (ICSE2008), pp 113–116

Kristen Elserougi, Ranil Fernando and Luca Wei 2006 Phase locked loop design, PhD dissertation, School of Engineering, Santa Clara University, Santa Clara, California

Kun-Seok Lee, Byeong-Ha Park, Han-il Lee and Min Jong Yoh 2003 Phase frequency detectors for fast frequency acquisition in Zero- dead-zone CPPLLs for mobile communication systems, Solid-state circuits conference, 2003 ESSCIRC’03. In: Proceedings of the 29th European IEEE, pp. 525–528

Mano M, Selva Priya G and RekhaSwathi Sri K 2013 Design and implementation of modified charge pump for phase locked loop. Int. J. Emerging Technol. Adv. Eng. 3: 558–562

Markovic D, Nikolic B and Oklobdžija V G 2000 A general method in synthesis of pass-transistor circuits. Microelectron. J. 31: 991–998

Mhd Zaher Al Sabbagh 2007 0.18 µm phase/frequency detectors and charge pump design for digital video Broadcasting for handheld’s phase-locked-loop systems MS dissertation, Graduate school of the Ohio State University, Ohio

Mozhgan Mansuri, Dean Liu and Chih-Kong Ken Yang 2002 Fast frequency acquisition phase-frequency detectors for GSamples/s phase-locked loops. IEEE J. Solid-State Circuits 37: 1331–1334

NehaPathak and Ravi Mohan 2014 Performance analysis and implementation of CMOS current starved voltage controlled oscillator for phase locked loop. Int. J. Emerging Technol. Adv. Eng. 4: 365–369

Talwekar R H and Limaye S S 2010 Design of high gain, high bandwidth Op-Amp for reduction of mismatch currents in charge pump PLL in 180 nm CMOS technology. World Acad. Sci. Eng. Technol. 72: 590–593

Wen-Ching Chang, Chun-Hung Lien and Yu-Chung Wei 2002 A fully integrated CMOS PLL for frequency synthesizer using Gm-C filter. In: Proceedings WSEAS international conference, World Scientific and Engineering Academy and Society (WSEAS), pp 451–279

Whitaker S 1983 Pass-transistor networks optimize n-MOS logic. Electronics Letters, Penton Publishing 56: 144–148

Xintian Shi 2008 Design of low phase noise low power CMOS phase locked loops. PhD dissertation, Faculty of Sciences, University of Neuchatel, Switzerland

Yun Chiu 2013 On the operation of CMOS active-cascode gain stage. J. Comput. Commun. 1: 18

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

ANUSHKANNAN, N.K., MANGALAM, H. Design of a CMOS PFD-CP module for a PLL. Sadhana 40, 1105–1116 (2015). https://doi.org/10.1007/s12046-015-0379-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12046-015-0379-1