Abstract

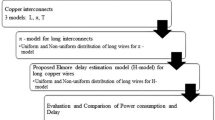

The interconnect temperature of very large scale integration (VLSI) circuits keeps rising due to self-heating and substrate temperature, which can increase the delay and power dissipation of interconnect wires. The thermal vias are regarded as a promising method to improve the temperature performance of VLSI circuits. In this paper, the extra thermal vias were used to decrease the delay and power dissipation of interconnect wires of VLSI circuits. Two analytical models were presented for interconnect temperature, delay and power dissipation with adding extra dummy thermal vias. The influence of the number of thermal vias on the delay and power dissipation of interconnect wires was analyzed and the optimal via separation distance was investigated. The experimental results show that the adding extra dummy thermal vias can reduce the interconnect average temperature, maximum temperature, delay and power dissipation. Moreover, this method is also suitable for clock signal wires with a large root mean square current.

Similar content being viewed by others

References

Semiconductor Industry Association. 2011 International Technology Roadmap for Semiconductors [M]. Berlin: Springer-Verlag, 2011.

Sahoo S, Datta M, Kar R. An efficient dynamic power estimation method for on-chip VLSI interconnects [C]// International Conference on Emerging Applications of Information Technology. Piscataway: IEEE, 2011: 379–382.

Moiseev K, Wimer S, Kolodny A. Timing-constrained power minimization in VLSI circuits by simultaneous multilayer wire spacing [J]. Integration the VLSI Journal, 2015, 48(1): 116–128.

Frankel B, Wimer S. Optimal VLSI delay tuning by wire shielding [J]. Journal of Optimization Theory and Applications, 2016, 170(3): 1060–1067.

Kar R, Maheshwari V, Mondal S, et al. Bhattacharjee. A novel power estimation method for on-chip VLSI distributed RLCG global interconnects using model order reduction technique [C]// International Conference on Advances in Computer Engineering. Piscataway: IEEE, 2010: 105–109.

Dhiman R, Chandel R. Delay analysis of buffer inserted sub-threshold interconnects [C]// Analog Integrated Circuits and Signal Processing. Massachusetts: Kluwer Academic Publishers Hingham, 2016: 4821–4829.

Mohammad A, Malgorzata C J. Delay and power optimization with TSV-aware 3D floorplanning [C]// International Symposium on Quality Electronic Design. Piscataway: IEEE, 2014: 189–197.

Ni M, Memik S O. Self-heating-aware optimal wire sizing under Elmore delay model [C]// Design, Automation & Test in Europe Conference. Piscataway: IEEE, 2007: 1–6.

Zhang Y, Dong G, Yang Y T, et al. A novel interconnect optimal buffer insertion model considering the self-heating effect [J]. Journal of Semiconductors, 2013, 34(11): 1–6.

Ajami A H, Banerjee K, Pedram M. Modeling and analysis of nonuniform substrate temperature effects on global ULSI interconnects [J]. IEEE Trans on Computer-Aided Design of Integrated and Systems, 2005, 24(6): 849–861.

Goplen B, Sapatnekar S. Placement of thermal vias in 3-D ICs using various thermal objectives [J]. IEEE Trans on Computer-Aided Design of Integrated and Systems, 2006, 25(4): 692–709.

Galicia M, Zajac P, Maj C, et al. Characterization of thermal vias for 3D ICs using FEM analysis [C]// International Workshop on Thermal Investigations of ICs and Systems. Paris: IEEE, 2015: 1–4.

Zajac P, Galicia M, Maj C, et al. Impact of floor planning and thermal vias placement on temperature in 2D and 3D processors [J]. Microelectronics Journal, 2016, 52: 40–48.

Chiang T Y, Banerjee K, Saraswat K. Effect of via separation and low-k dielectric materials on the thermal characteristics of Cu interconnects [C] // International Electron Devices Meeting. Piscataway: IEEE, 2000: 261–264.

Wang Z, Dong G, Yang Y T, et al. Effect of dummy vias on interconnect temperature variation [J]. Chinese Science Bulletin, 2011, 56 (21): 2286–2290.

Uttraphan C, Husin N S, Hani M K. An optimization algorithm for simultaneous routing and buffer insertion with delay-power constraints in VLSI layout design [C]// International Symposium on Quality Electronic Design. Piscataway: IEEE, 2014: 357–365.

Ciofi I, Contino A, Roussel P J, et al. Impact of wire geometry on interconnect RC and circuit Delay [J]. IEEE Trans on Electron Devices, 2016, 63(6): 2488–2496.

Zhang Y, Dong G, Yang Y T, et al. A novel interconnectoptimal power model considering self-heating effect [J]. Acta Physica Sinica, 2013, 62(1):709–712(Ch).

Subrina S, Kotchetkov D, Balandin A A. Heat removal in silicon-on-insulator integrated circuits with graphene lateral heat spreaders [J]. IEEE Electron Device Letters, 2010, 30(12): 1281–1283.

Jiang L J, Xu C, Rubin B J, et al. A thermal simulation process based on electrical modeling for complex interconnect, packaging, and 3DI structures [J]. IEEE Trans on Advance Packaging, 2011, 33(4): 777–785.

Magen N, Kolodny A, Weiser U, et al. Interconnect-power dissipation in a micro-processor [C]// International Workshop on System-Level Interconnect Prediction. Paris: ACM, 2004: 7–13.

Author information

Authors and Affiliations

Corresponding author

Additional information

Foundation item: Supported by the Guangdong Provincial Natural Science Foundation of China (2014A030313441), the Guangzhou Science and Technology Project (201510010169), the Guangdong Province Science and Technology Project (2016B090918071, 2014A040401076), and the National Natural Science Foundation of China (61072028)

Rights and permissions

About this article

Cite this article

Xu, P., Pan, Z. Effects of Dummy Thermal Vias on Interconnect Delay and Power Dissipation of Very Large Scale Integration Circuits. Wuhan Univ. J. Nat. Sci. 23, 438–446 (2018). https://doi.org/10.1007/s11859-018-1345-7

Received:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11859-018-1345-7

Key words

- very large scale integration (VLSI) circuits

- interconnect temperature

- interconnect delay

- thermal vias

- interconnect power dissipation