Abstract

We propose the design and fabrication of a coplanar electrode structure for an organic metal–semiconductor field-effect transistor (OMESFET), with the gate electrode self-aligned between the source and drain electrodes. We first used nanoimprint lithography (NIL) to define a channel area of the device on a patterned metal, and then used chemical wet etching to create the source and drain electrodes by removing the metal in the channel area. After the wet etching, the gate electrode was deposited in the channel area. The organic semiconductor was then deposited to cover the patterned electrodes. The rectifying response and the device characteristics prove that the self-aligned device is a functional OMESFET. In this experiment, we also demonstrated that the self-aligned OMESFET has lower driving voltages and smaller subthreshold swing (SS) than that of a conventional organic metal–insulator–semiconductor field-effect transistor (OMISFET). Compared with the most common OMESFET structure, this self-aligned coplanar structure effectively eliminates the overlapping area between the gate and source/drain electrodes commonly seen in currently reported OMESFETs, which means that this self-aligned device structure reduces the parasitic capacitance, theoretically allowing the transistor to have a higher cutoff frequency. These features render our proposed OMESFET devices more favorable for low-power and high-frequency organic circuit applications.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

Organic electronic devices have attracted widespread interest because of the possibilities of enabling low-cost fabrication and flexible electronics. One of the advantages is the feasibility to “print” the device by inkjet printing.1,2,3 Current researches of organic electronics include organic light-emitting diodes,4,5 organic solar cells6 and organic field effect transistors (OFET).7 Today, continuous improvements in organic semiconductor material synthesis and device structure optimization have gradually improved their performances. Even though device performance has been greatly improved in the past decade, OFETs still need further development to be used in practical applications, due to their high operation voltages and low operation frequencies. These deficiencies limit the adoption of OFETs in organic circuits.

Depending on the device structure, there are basically two types of OFETs: the organic metal–insulator–semiconductor field-effect transistor (OMISFET) and the organic metal–semiconductor field-effect transistor (OMESFET).8 The OMISFET structure contains an insulating layer between the gate electrode and the semiconducting polymer. The quality of the insulating layer often influences the device performance.9,10,11,12 To build a flexible device, the insulating layer also needs to be flexible, and is usually a polymer or oxide thin film. Typically, those insulators have a low breakdown potential and a low dielectric constant. To prevent device breakdown, the transistor usually requires a thick insulating layer, which in turn requires a high gate voltage to induce the field-effect charges in the transistor channel. In the MESFET structure, the gate electrode directly contacts the organic semiconductor and induces a depletion region in the semiconductor layer.13,14 The depletion region behaves like a highly insulating layer due to the lack of charge carriers. In a forward bias or without bias on the stack of the gate electrode and the organic semiconductor, only a thin depletion layer is formed. The majority portion of the transistor channel is still in a semiconducting state. This condition is considered as the “turned-on” status, because the channel is able to conduct the current through the semiconducting material. In the condition of reverse bias on the stack of the gate electrode and the organic semiconductor, the depletion layer expands through the whole thickness of the semiconductor layer, and eventually blocks charge carriers flowing from the source to the drain, turning off the device.15 This on/off mechanism only requires a relatively low voltage as compared to an OMISFET of a similar size. Therefore, OMESFETs can be a potential device for low voltage applications.16

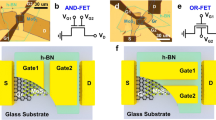

OMESFETs in recent development have been built in the configuration of top gate and bottom source/drain, with the organic semiconductor layer sandwiched between the gate and the source/drain, as shown in Fig. 1. However, this configuration generally has a large overlapping area between the gate and the source/drain electrodes, because it is difficult to align the gate electrode exactly to the channel region during fabrication. Such a large overlap introduces a large parasitic capacitance between the electrodes, as shown in Fig. 1. The parasitic capacitance is unwanted because it greatly lowers the device’s ac performance, for example, reducing the device’s cut-off frequency.15 Therefore, a bottom gate with bottom source/drain configuration is desirable for high-frequency circuit applications, because of the elimination of the parasitic overlap capacitance. However, when the device dimensions gradually shrink , it becomes more and more difficult to pattern the gate electrode between the source and drain electrodes by an optical alignment in photolithography. In this study, we propose a method to fabricate OMESFETs with a self-aligned gate electrode between the source and drain electrodes. This approach does not require a highly accurate alignment system and is able to form the gate electrode easily in the channel region without contacting the source and drain electrodes.

Experimental Method

The fabrication process of the self-aligned OMESFET is illustrated in Fig. 2 in cross-sectional view. A layer of 40 nm gold (Au) was first deposited on the silicon dioxide (SiO2) substrate with 4 nm chromium (Cr) as an adhesion layer. Then 400 nm poly(methyl methacrylate) (PMMA) was spin-coated on the top of the Au as a nanoimprinting resist (Fig. 2a). The PMMA layer was thermally imprinted by a mold with a protrusive stripe 10 mm wide and 270 nm deep (Fig. 2b). The nanoimprint was carried out at 175 °C with a pressure of 5 MPa. After cooling to room temperature, the mold was released from the PMMA film, leaving a thin PMMA residual layer on the Au surface (Fig. 2c). The pattern of the imprint mold was transferred to the PMMA layer. Oxygen reactive-ion etching (RIE) was used to remove the PMMA residual layer to expose the Au surface (Fig. 2d). The Au/Cr layer was sequentially etched in a diluted Au etchant and Cr etchant, forming an undercut profile (Fig. 2e). A 25-nm aluminum (Al) layer with 3-nm Cr adhesion layer were deposited to form the gate electrode (Fig. 2f). After lifting off in acetone solvent, the PMMA and Al/Cr on the PMMA were removed. The separated metals serve as the source, drain, and gate electrodes for the OMESFET (Fig. 2g). Finally, spin-coating a 40-nm poly(3-hexylthiophene-2,5-diyl) (P3HT) film as the active semiconducting layer on the electrodes completed the fabrication of the OMESFET device.

Fabrication process of the self-aligned OMESFET: (a) spin-coating the imprinting resist on the Au surface; (b) thermally imprinting the resist; (c) releasing the imprinting mold; (d) using O2 RIE to remove the residual layer of the resist; (e) isotropic etching of the Au/Cr to create an undercut profile; (f) depositing Al/Cr as the gate electrode; (g) removing PMMA and Al/Cr on the PMMA in acetone solvent; and (h) spin-coating P3HT as the active semiconductor layer.

The fabricated source/drain and gate electrodes were examined by optical microscope and atomic-force microscope (AFM). The transfer and output characteristics of the OMESFET device were measured using voltage source meters.

Results and Discussion

Electrode Patterning by Nanoimprint

Nanoimprint lithography (NIL) has been widely used in patterning applications, such as nanostructure patterning,17 electrode patterning,18 and organic semiconductor patterning.9,10,11,12,13,14,15,16,17,18,19,20,21 In this study, NIL was employed to define the channel length because it has the potential capability to create patterns ranging from micrometers to nanometers. The imprint mold was made of SiO2 and was coated with 1 h,1 h,2 h,2 h-perfluorodecyltrichlorosilane (FDTS), a hydrophobic coating, for easy separation of the mold from the PMMA resist after NIL. However, even though the mold had been coated with FDTS, imprinting resist above the Au electrode was peeled off while releasing the imprinting mold. This was because the PMMA resist has very poor adhesion on the Au surface. Thiol-functionalized surfactants can be used to improve adhesion between the PMMA resist and the Au electrode, but we chose not to use surfactants on the Au surface, because they interfere with charge injection across the Au/P3HT interface in our bottom contact device configuration.

In this work, the mold has a single protrusive stripe 270 nm high and 10 mm wide. The typical practice was to deposit 300-nm PMMA so that the mold can imprint 270 nm into the resist layer, leaving about 30 nm for the residual layer. To overcome the poor adhesion issue, the PMMA film was deposited with a thickness of 400 nm to prevent the PMMA from peeling off the Au surface. However, a thick PMMA resist layer also leaves a thicker residual layer, which requires a longer oxygen RIE time to remove it. Another solution to resolve the peeling issue is to utilize Teflon-AF as the imprinting resist. Typical imprinting conditions for Teflon-AF have been reported19. The better adhesion between the Teflon-AF layer and the Au surface allows imprinting of a Teflon-AF film of 300 nm in thickness without peeling-off defects. Both approaches provided results of similar quality and could be used for electrode patterning in the fabrication of a self-aligned OMESFET device.

Removing the Au and Cr metal in the channel region creates two separated metal pads serving as the source/drain electrodes. The channel length was 10 mm, and the channel width was 600 mm. To fine control the etching process, particularly to minimize the lateral etching of the metal films underneath the PMMA layer, a slow etching rate was used. Both the Au etchant and Cr etchant were diluted in DI water in the ratio of 1:2 (etchant:DI water). The wet etching process creates an undercut profile because the chemical etchant isotropically etches the metal below the resist. This undercut profile ensures the separation of the gate electrode from the source and drain electrodes when depositing the gate electrode. Once the source, drain, and gate electrodes were created, the active layer of the OMESFET was deposited by spin-coating the P3HT solution on the electrodes at 900 rpm. The P3HT solution was prepared in 20 wt% by dissolving P3HT polymer in dichlorobenzene.

Self-Aligned OMESFET

The 3D schematic of the self-aligned electrodes for OMESFET is depicted in Fig. 3a, and the microscope image of the patterned electrodes is shown in Fig. 3b. The Au and Al electrodes are separated by small gaps after electrode patterning. Figure 3c is an AFM height scan of the electrodes showing that the Au electrodes are about 45 nm tall and the Al electrode is about 28 nm tall. The gaps separating the gate and source/drain electrodes are about 300 nm. The dimension of the gap can be controlled by the etchant concentration and etching time during the wet etching of the Au/Cr layer.

The P3HT film was then deposited on the patterned electrodes as the device active layer. To have a MESFET behavior, the device needs to form a Schottky contact at the interface of the gate electrode and the P3HT layer. The Schottky contact can be verified from the rectifying response, as shown in Fig. 4. The rectifying response was obtained by varying the voltage from − 4 V to 3 V on the gate electrode while the source and drain electrodes were grounded. The rectifying response proves that the Schottky barrier exists at the interface of Al and P3HT, and it can block the current flowing from the gate to P3HT when the gate terminal is reverse-biased (VG > 0 V). From the Schottky diode I–V curve for the Al/P3HT junction, we found that the OMESFET can be operated in the gate voltage between − 1 V and at least 3 V without experiencing a large gate leakage current. Further increase of the gate voltage is not desired because a reverse breakdown of the Al/P3HT Schottky diode can occur, resulting in a huge current flow through the gate terminal.

Figure 5 shows the output ID–VD curve of the OMESFET, and the transfer ID–VG curve at VD of – 10 V. According to the electrical response, the P3HT-based OMESFET is considered as a “normally on” transistor, indicating that the channel is conductive when no bias is applied to the gate, and that the device can be turned off when the gate reverse bias reaches to a certain level (2.4 V in our device). This result verified that the approach of fabricating the self-aligned OMESFET fabrication was successful. In this demonstration, the electrical response hardly reached flat saturation currents, and it was difficult to completely turn off the drain current, resulting in a low on/off ratio. The on/off ratio here is about 1.63 with 0 V on-state gate voltage and 2.4 V off-state gate voltage, or 3.68 with − 1 V on-state gate voltage and 2.4 V off-state gate voltage. The reason is that the P3HT active layer was influenced by moisture and oxygen during the device measurement in the atmosphere, thus increasing the conductivity.22

To verify the low power advantage of the self-aligned OMSFET, we compared the performance of the self-aligned OMESFET with that of the conventional OMISFET. In this comparison, the OMISFET structure has 10 mm channel length, 500 mm channel width, 100 nm SiO2 dielectric layer and 40 nm P3HT active layer. The microscope images of the OMISFET electrode and the schematic of the device structure are shown in Fig. 6a. The OMISFET ID–VD response and the ID–VG transfer response at VD of − 60 V are normalized by the channel width (500 mm), as shown in Fig. 6b and c. The OMESFET responses previously shown in Fig. 5 are also normalized (normalized curves are not shown here) by its channel width (600 mm) in order to compare with the normalized OMISFET responses. Both normalized ID-VD responses show that the ID currents at VG of 0 V are around − 2 × 10–10 A, which means that both devices without the gate voltage effect have the same current level, indicating that the comparison is valid. The operational gate voltage of the self-aligned OMESFET is in the range from − 1 V to 2 V, but the OMISFET voltage is from 0 V to more than 30 V. In order to generate, for example, a current of − 1 × 10–9 A, the self-aligned OMESFET only needs to provide VG of 2 V and VD of − 4 V, but the OMISFET requires VG of − 10 V and VD of − 30 V. This verifies that the self-aligned OMESFET has a much lower operational voltage than that of the OMISFET. The threshold voltage (VT) of the self-aligned OMESFET is about 1 V and that of the OMISFET is about − 5 V. In addition, the subthreshold swing (SS) of the self-aligned OMESFET is about 2.83 × 103 mV/dec and the OMISFET is about 1.4 × 104 mV/dec. Table I summaries the performance of both devices. Since the self-aligned OMESFET needs further optimization and an accurate mathematical model, the frequency performance of the self-aligned OMESFET and the conventional OMESFET were not compared in this work.

The working principle of the OMESFET is related to the Schottky barrier at the metal/organic semiconductor interface, and to the depletion region in the organic semiconductor.15 Figure 7a shows the energy band diagram of the OMESFET illustrating the Schottky barrier and the depletion region. The energy band diagram includes the Fermi level, the highest occupied molecular orbital (HOMO) and the lowest unoccupied molecular orbital (LUMO) levels of the P3HT, and the work function level of the Al electrode. In this study, Al was used as the gate electrode because it offers a relatively low work function as compared with the HOMO level of the P3HT. The energy level difference between the Al work function and the P3HT HOMO level forms the Schottky barrier at the Al/P3HT interface. Due to the Schottky barrier, the current flowing from the Al electrode to the P3HT film is blocked when a positive voltage is applied on the gate. The Al/P3HT junction is forward biased when a negative voltage is applied on the gate, and a large current can flow from the P3HT film to the Al electrode.23 This mechanism explains the rectifying response shown in Fig. 4. When the device is in thermal equilibrium condition, the depletion region is formed due to the bending of the HOMO and LUMO levels, which is caused by the alignment of the P3HT Fermi level and the Al work function. With the energy level bending, carriers move away from the Al/P3HT interfacial region. Therefore, the depletion region without carriers does not conduct current. The reverse gate bias extends the bending area, resulting in the expansion of the depletion region,as shown in Fig. 7b. Figure 7c depicts the depletion region in the P3HT film. Applying a reverse bias expands the depletion region and turns off the channel at a certain biasing level.

Forming the Schottky barrier and the depletion region at the Al/P3HT interface: (a) energy band diagram illustrating the formation of the Schottky barrier and the depletion region at thermal equilibrium; (b) energy band diagram of the Schottky diode under a reverse bias; (c) the depletion region and its expansion in the P3HT film under a reverse bias.

Conclusions

A simple method to fabricate a self-aligned OMESFET without sophisticated optical alignment system is proposed and demonstrated . This approach was realized by combining NIL and chemical wet etching before the gate electrode deposition. The consideration of using NIL is its capability to create nanoscale channels although we only demonstrated a 10 mm channel length in this experiment. The purpose of the wet etching is to form the source and drain electrodes and to create an undercut profile by lateral etching, in order to form gaps between the gate and the source/drain electrodes. In this work, a self-aligned structure with 300-nm gaps separating the 45-nm-tall source/drain electrodes and the 28-nm-tall gate electrode was achieved. The advantage of a self-aligned structure is the elimination of the overlapping area between the gate and the source/drain electrodes. Without the overlapping area, the parasitic capacitance can be greatly reduced, and thus the cut-off frequency of the device can theoretically be increased. The rectifying response and the OMESFET characteristics extracted from the device have proven that the proposed self-aligned structure is a functional OMESFET. Although the frequency performance has not been shown in this work, the self-aligned OMESFET still demonstrated a lower operational voltage and lower subthreshold swing than that of OMISFET.

References

S.E. Molesa, A.D.L.F. Vornbrock, P.C. Chang, and V. Subramanian, Low-voltage inkjetted organic transistors for printed RFID and display applications. IEDM Tech. Dig. 508, 109 (2005).

W. Smaal, C. Kjellander, Y. Jeong, A. Tripathi, B.V.D. Putten, A. Facchetti, H. Yan, J. Quinn, J. Anthony, K. Myny, W. Dehaene, and G. Gelinck, Complementary integrated circuits on plastic foil using inkjet printed n- and p-type organic semiconductors: fabrication, characterization, and circuit analysis. Org. Electron. 13, 1686 (2012).

W. Clemens, W. Fix, J. Ficker, A. Knobloch, and A. Ullmann, From polymer transistors toward printed electronics. J. Mater. Res. 19, 1963 (2004).

C.W. Tang, and S.A. VanSlyke, Organic electroluminescent diodes. Appl. Phys. Lett. 51, 913 (1987).

J.H. Burroughes, D.D.C. Bradley, A.R. Brown, R.N. Marks, K. Mackay, R.H. Friend, P.L. Burns, and A.B. Holmes, Light-emitting diodes based on conjugated polymers. Nature 347, 539 (1990).

C.W. Tang, Twolayer organic photovoltaic cell. Appl. Phys. Lett. 48, 183 (1986).

H. Koezuka, A. Tsumura, and T. Ando, Field-effect transistor with polythiophene thin film. Synthetic Met. 18, 699 (1987).

G. Horowitz, Organic field-effect transistors. Adv. Mater. 10, 365 (1998).

J. Veres, S. Ogier, G. Lloyd, and D.D. Leeuw, Gate insulators in organic field-effect transistors. Chem. Mater. 16, 4543 (2004).

J. Park, S.Y. Park, S.-O. Shim, H. Kang, and H.H. Lee, A polymer gate dielectric for high-mobility polymer thin-film transistors and solvent effects. Appl. Phys. Lett. 85, 3283 (2004).

K. Shin, C. Yang, S.Y. Yang, H. Jeon, and C.E. Park, Effects of polymer gate dielectrics roughness on pentacene field-effect transistors. Appl. Phys. Lett. 88, 072109 (2006).

S. Steudel, S.D. Vusser, S.D. Jonge, D. Janssen, S. Verlaak, J. Genoe, and P. Heremans, Influence of the dielectric roughness on the performance of pentacene transistors. Appl. Phys. Lett. 85, 4400 (2004).

Y. Ohmori, H. Takahashi, K. Muro, M. Uchida, T. Kawai, and K. Yoshino, Fabrication and characteristics of Schottky gated poly(3-alkylthiophene) field effect transistors. Jap. J. Appl. Phys. 30, L610 (1991).

C.H. Kim, D. Tondelier, B. Geffroy, Y. Bonnassieux, and G. Horowitz, Operating mechanism of the organic metal-semiconductor field-effect transistor (OMESFET). Eur Phys. J. Appl. Phys. 56, 34105 (2011).

S.M. Sze, and K.K. Ng, Physics of semiconductor devices, 3rd ed., (Hoboken: Wiley, 2007).

A. Dimopoulos, A. Takshi, and J.D. Madden, Low voltage polymer transistors. Can. Con. El. Comp. En. 956, 528 (2007).

S.Y. Chou, P.R. Krauss, W. Zhang, L. Guo, and L. Zhuang, ub-10 nm imprint lithography and applications. J. Vac. Sci. Technol. B 15, 2897 (1997).

G. Leising, B. Stadlober, U. Haas, A. Haase, C. Palfinger, H. Gold, and G. Jakopic, Nanoimprinted devices for integrated organic electronics. Microelectron. Eng. 83, 831 (2006).

Y. Lo, D. Li, Z. Sun, S. Shaik, and X. Cheng, High-resolution nondestructive patterning of isolated organic Semiconductors. J. Vac. Sci. Technol. B. 30, 06FB04 (2012).

Y. Jung, and X. Cheng, Dual-layer thermal nanoimprint lithography without dry etching. J. Micromech. Microeng. 22, 085011 (2012).

X. Cheng, Y. Hong, J. Kanicki, and L.J. Guo, High-resolution organic polymer light-emitting pixels fabricated by imprinting technique. J. Vac. Sci. Technol. B 20, 2877 (2002).

S. Hoshino, M. Yoshida, S. Uemura, T. Kodzasa, N. Takada, T. Kamata, and K. Yase, Influence of moisture on device characteristics of polythiophene-based field-effect transistors. J. Appl. Phys. 95, 5088 (2004).

F. Hirose, Y. Kimura, and M. Niwano, P3HT/Al organic/inorganic heterojunction diodes investigated by I-V and C-V measurements. IEICE Trans. Electron. 92, 1475 (2009).

Acknowledgments

This work is supported by the National Science Foundation under Grant No. 1054137. Use of the TAMU Materials Characterization Facility is acknowledged.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Lo, YC., Cheng, X. Self-Aligned Organic Metal–Semiconductor Field-Effect Transistor. J. Electron. Mater. 52, 1323–1330 (2023). https://doi.org/10.1007/s11664-022-10095-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-022-10095-x