Abstract

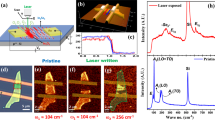

Optical memory integrates the function of optical sensing in memory devices, remarkably promoting the interconnection between sensory and memory terminals. Silicon charge-coupled photodetectors and floating gate memory have been widely used in imaging and storage technologies, respectively. However, the heterogeneous integration of the two devices requires technological innovation and complex electrical connections. In this work, we adopt a three-dimensional layer stacking method to design a novel optical memory device. On the top of Si charge-coupled photodetectors, we successively deposit two-dimensional graphene, hexagonal boron nitride, and molybdenum disulfide as a floating gate layer, a tunneling layer, and a readout layer, respectively. By applying a gate bias on lightly doped Si, a deep depletion layer is formed with a high voltage potential drop. Under dark conditions, the depletion layer cannot be filled, and the electric field across the h-BN tunnel barrier is relatively small. Under light irradiation, the deep depletion layer is gradually filled, and the h-BN tunneling layer withstands the increasing electric field, resulting in charge storage in the floating gate layer. Based on this mechanism, the device exhibits a gate voltage-dependent operation mode, including an integrated optical sensing-memory mode and an electrically driven storage mode. Under moderate gate voltage, the device can effectively detect the optical information with varied intensity and store the optical information in the floating gate, displaying optically controlled memory characteristics. Our work demonstrates a compact device structure for optical memory and displays excellent optically controlled memory performance, which can be applied in artificial vision systems.

Similar content being viewed by others

References

Clavelier L, Deguet C, Cioccio L D, et al. Engineered substrates for future More Moore and More than Moore integrated devices. In: Proceedings of International Electron Devices Meeting (IEDM), 2010. 42–45

Zhou F, Chen J, Tao X, et al. 2D materials based optoelectronic memory: convergence of electronic memory and optical sensor. Research, 2019, 2019: 9490413

Wu Y, Deng W J, Chen X Q, et al. CMOS-compatible retinomorphic Si photodetector for motion detection. Sci China Inf Sci, 2023, 66: 162401

Liu Y, Liu D, Gao C, et al. Self-powered high-sensitivity all-in-one vertical tribo-transistor device for multi-sensing-memory-computing. Nat Commun, 2022, 13: 7917

Zhao Y, Gobbi M, Hueso L E, et al. Molecular approach to engineer two-dimensional devices for CMOS and beyond-CMOS applications. Chem Rev, 2022, 122: 50–131

Bian Z, Miao J, Zhang T, et al. Carrier modulation in 2D transistors by inserting interfacial dielectric layer for area-efficient computation. Small, 2023, 19: e2206791

Cheng C D, Tiw P J, Cai Y M, et al. In-memory computing with emerging nonvolatile memory devices. Sci China Inf Sci, 2021, 64: 221402

Yang H Z, Huang P, Han R Z, et al. An ultra-high-density and energy-efficient content addressable memory design based on 3D-NAND flash. Sci China Inf Sci, 2023, 66: 142402

Hou X, Liu C, Ding Y, et al. A logic-memory transistor with the integration of visible information sensing-memory-processing. Adv Sci, 2020, 7: 2002072

Hou Y X, Li Y, Zhang Z C, et al. Large-scale and flexible optical synapses for neuromorphic computing and integrated visible information sensing memory processing. ACS Nano, 2021, 15: 1497–1508

Zhou F, Liu Y, Shen X, et al. Low-Voltage, optoelectronic CH3NH3PbI3−xClx memory with integrated sensing and logic operations. Adv Funct Mater, 2018, 28: 1800080

Gao Z, Chen S, Li R, et al. An artificial olfactory system with sensing, memory and self-protection capabilities. Nano Energy, 2021, 86: 106078

Wu G, Zhang X, Feng G, et al. Ferroelectric-defined reconfigurable homojunctions for in-memory sensing and computing. Nat Mater, 2023, 22: 1499–1506

Sekitani T, Yokota T, Zschieschang U, et al. Organic nonvolatile memory transistors for flexible sensor arrays. Science, 2009, 326: 1516–1519

Boyle W S, Smith G E. Charge coupled semiconductor devices. Bell Syst Technical J, 1970, 49: 587–593

Hiraoka Y, Sedat J W, Agard D A. The use of a charge-coupled device for quantitative optical microscopy of biological structures. Science, 1987, 238: 36–41

Fujiwara A, Takahashi Y. Manipulation of elementary charge in a silicon charge-coupled device. Nature, 2001, 410: 560–562

Padilla C, Castander F J, Alarcón A, et al. The physics of the accelerating universe camera. Astron J, 2019, 157: 246

Marega G M, Ji H G, Wang Z, et al. A large-scale integrated vector-matrix multiplication processor based on monolayer molybdenum disulfide memories. Nat Electron, 2023, 6: 991–998

Vu Q A, Kim H, Nguyen V L, et al. A high-on/off-ratio floating-gate memristor array on a flexible substrate via CVD-grown large-area 2D layer stacking. Adv Mater, 2017, 29: 1703363

Marega G M, Zhao Y, Avsar A, et al. Logic-in-memory based on an atomically thin semiconductor. Nature, 2020, 587: 72–77

Sasaki T, Ueno K, Taniguchi T, et al. Understanding the memory window overestimation of 2D materials based floating gate type memory devices by measuring floating gate voltage. Small, 2020, 16: 2004907

Zhao Y, Qiao J, Yu Z, et al. High-electron-mobility and air-stable 2D layered PtSe2 FETs. Adv Mater, 2017, 29: 1604230

Bian Z, Miao J, Zhao Y, et al. Strong interlayer interaction for engineering two-dimensional materials. Acc Mater Res, 2022, 3: 1220–1231

Miao J, Wu L, Bian Z, et al. A “Click” reaction to engineer MoS2 field-effect transistors with low contact resistance. ACS Nano, 2022, 16: 20647–20655

Geim A K, Grigorieva I V. Van der Waals heterostructures. Nature, 2013, 499: 419–425

Liu C, Chen H, Wang S, et al. Two-dimensional materials for next-generation computing technologies. Nat Nanotechnol, 2020, 15: 545–557

Wang S, Liu X, Xu M, et al. Two-dimensional devices and integration towards the silicon lines. Nat Mater, 2022, 21: 1225–1239

Liu Y, Huang Y, Duan X. Van der Waals integration before and beyond two-dimensional materials. Nature, 2019, 567: 323–333

Liu Y, Duan X, Shin H J, et al. Promises and prospects of two-dimensional transistors. Nature, 2021, 591: 43–53

Ning H K, Yu Z H, Li T T, et al. From lab to fab: path forward for 2D material electronics. Sci China Inf Sci, 2023, 66: 160411

Wu L, Wang A, Shi J, et al. Atomically sharp interface enabled ultrahigh-speed non-volatile memory devices. Nat Nanotechnol, 2021, 16: 882–887

Wang J, Zou X, Xiao X, et al. Floating gate memory-based monolayer MoS2 transistor with metal nanocrystals embedded in the gate dielectrics. Small, 2015, 11: 208–213

Acknowledgements

This work was primarily supported by National Natural Science Foundation of China (Grant Nos. 62090034, 62104214, 62261160574, 62090030), National Key R&D Program of China (Grant No. 2022YFA1204303), Young Elite Scientists Sponsorship Program by CAST (Grant No. 2021QNRC001), Opening Project of Key Laboratory of Optoelectronic Chemical Materials and Devices of Ministry of Education, Jianghan University (Grant No. JDGD-202202), and Kun-Peng Program of Zhejiang Province. We thank ZJU Micro-Nano Fabrication Center and ZJU-Hangzhou Global Scientific and Technological Innovation Center for the supports.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Bian, Z., Tian, F., Li, Z. et al. Heterogeneous integration of 2D materials on Si charge-coupled devices as optical memory. Sci. China Inf. Sci. 67, 160404 (2024). https://doi.org/10.1007/s11432-024-3993-5

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11432-024-3993-5