Abstract

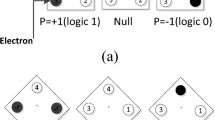

Quantum-dot Cellular Automata (QCA) is a novel computational paradigm in nanotechnology with some benefits, such as low energy usage, rapid speed, and high density. Several logical circuits have been examined in this nanotechnology, but subtractors with easy access to inputs and outputs cells are not explored thoroughly. Due to the lack of easy access to inputs and outputs, the previous designs are less expandable and cannot be easily used in other circuits. Subtractors are often executed within a binary adder when using the traditional two’s complement notation at just a small computational cost by providing an addition/subtraction selector to the carry-in and inverting the second operand. The same methodology as for adder's circuit can be used to create a subtractor, a digital circuit in nanoelectronics that performs numerical subtraction. Consequently, it is necessary to construct this circuit so that the inlets and outlets are simple to access. Therefore, a new QCA-based subtractor design is suggested in the present investigation. The scheme is then assessed and compared to state-of-the-art designs. This design offers a solution to the problem of access to input and output for data exchange in QCA. The suggested plan uses the least amount of space, the fewest number of cells, and delay three-layer crossing approaches as compared to the existing QCA design. The suggested subtractor needs 25 cells and takes up 0.01 µm2. The QCADesigner tool provides this circuit’s simulation results and confirms the suggested circuit’s exactification. The suggested circuit is among the best regarding the area, cell counts, and quantum costs.

Similar content being viewed by others

Data availability

All data are provided in the paper.

References

Ikeda, K., Suzuki, K., Konoike, R., Namiki, S., Kawashima, H.: Large-scale silicon photonics switch based on 45-nm CMOS technology. Opt. Commun. 466, 125677 (2020)

Pouyan, S.M., Miri, M., Sheikhi, M.: Design of a CMOS compatible dual polarization four-level optical modulator based on thermally-actuated phase transition of vanadium dioxide. Photon. Nanostruct. Fundam. Appl. 35, 100710 (2019)

Liu, W., Wang, J., Xu, X., Zhao, C., Xu, X., Weiss, P.S.: Single-step dual-layer photolithography for tunable and scalable nanopatterning. ACS Nano 15(7), 12180–12188 (2021)

Steinbuch, M., Oomen, T., Vermeulen, H.: Motion control mechatronics design, and Moore’s law. IEEJ J. Ind. Appl. 11(2), 245–255 (2022)

Ahmed, S., Naz, S.F., Bhat, S.M.: Design of quantum-dot cellular automata technology based cost-efficient polar encoder for nanocommunication systems. Int. J. Commun Syst 33(18), e4630 (2020)

Das, J.C., De, D.: Design of thermometer code-to-gray code converter circuit in quantum-dot cellular automata for nano-computing network. Photon. Netw. Commun. 41(3), 259–273 (2021)

Sun, J.P., Haddad, G.I., Mazumder, P., Schulman, J.N.: Resonant tunneling diodes: models and properties. Proc. IEEE 86(4), 641–660 (1998)

Hennessy, K., Lent, C.S.: Clocking of molecular quantum-dot cellular automata. J. Vac. Sci. Technol. B: Microelectron. Nanometer Struct. Process. Meas. Phenom. 19(5), 1752–1755 (2001)

Lent, C.S., Tougaw, P.D., Porod, W., Bernstein, G.H.: Quantum cellular automata. Nanotechnology 4(1), 49 (1993)

Fujisawa, T., Hayashi, T., Hirayama, Y., Cheong, H., Jeong, Y.: Electron counting of single-electron tunneling current. Appl. Phys. Lett. 84(13), 2343–2345 (2004)

Deng, L., Liu, W., Li, D., Mohammed, B.O.: A new sign detection design for the residue number system based on quantum-dot cellular automata. Photon. Netw. Commun. 42(1), 70–80 (2021)

Dhare, V., Mehta, U.: Test pattern generator for MV-based QCA combinational circuit targeting MMC fault models. IETE J. Res. 68(3), 1812–1822 (2022)

Singh, G., Raj, B., Sarin, R.K.: Fault-tolerant design and analysis of QCA-based circuits. IET Circuits Dev. Syst. 12(5), 638–644 (2018)

Sen, B., Dutta, M., Goswami, M., Sikdar, B.K.: Modular design of testable reversible ALU by QCA multiplexer with increase in programmability. Microelectron. J. 45(11), 1522–1532 (2014)

Gupta, N., Choudhary, K., Katiyal, S.: Two bit arithmetic logic unit (ALU) in QCA. Int. J. Recent Trends Eng. Technol. 8(2), 35 (2013)

Seyedi, S., Pourghebleh, B.: A new design for 4-bit RCA using quantum cellular automata technology. Opt. Quantum Electron. 55(1), 11 (2023)

Seyedi, S., Pourghebleh, B., Jafari Navimipour, N.: A new coplanar design of a 4-bit ripple carry adder based on quantum-dot cellular automata technology. IET Circuits Dev. Syst. 16(1), 64–70 (2022)

De, D., Das, J.C.: Design of novel carry save adder using quantum dot-cellular automata. J. Comput. Sci. 22, 54–68 (2017)

Roohi, A., DeMara, R.F., Khoshavi, N.: Design and evaluation of an ultra-area-efficient fault-tolerant QCA full adder. Microelectron. J. 46(6), 531–542 (2015)

Hashemi, S., Navi, K.: A novel robust QCA full-adder. Proc. Mater. Sci. 11, 376–380 (2015)

Walus, K., Vetteth, A., Jullien, G., Dimitrov, V.: RAM design using quantum-dot cellular automata, In: Nanotechnology conference, vol. 2: Citeseer, pp. 160–163 (2003)

Chaharlang, J., Mosleh, M.: An overview on RAM memories in QCA technology. Majlesi J. Electr. Eng. 11(2), (2017) https://journals.iau.ir/article_696259_b3e9006a8de1d51b619a9a8bacdb9cae.pdf

Safoev, N., Jeon, J.-C.: Design of high-performance QCA incrementer/decrementer circuit based on adder/subtractor methodology. Microprocess. Microsyst. 72, 102927 (2020)

Foroutan, S.A.H., Sabbaghi-Nadooshan, R., Mohammadi, M., Tavakoli, M.B.: Investigating multiple defects on a new fault-tolerant three-input QCA majority gate. J. Supercomput. 77, 8305–8325 (2021)

Imran, M., Collier, M., Landais, P., Katrinis, K.: Performance evaluation of hybrid optical switch architecture for data center networks. Opt. Switch. Netw. 21, 1–15 (2016)

Kassa, S., Gupta, P., Kumar, M., Stephan, T., Kannan, R.: Rotated majority gate-based 2n-bit full adder design in quantum-dot cellular automata nanotechnology. Circuit World 48(1), 48–63 (2022)

Marshal, R., Lakshminarayanan, G.: Fault resistant coplanar QCA full adder-subtractor using clock zone-based crossover. IETE J. Res. 69(1), 584–591 (2023)

Seyedi, S., Navimipour, N.J.: A Fault-tolerance nanoscale design for binary-to-gray converter based on QCA. IETE J. Res. (2021). https://doi.org/10.1080/03772063.2021.1908857

Moore, A.J., Wang, Y., Hu, Z., Kais, S., Weiner, A.M.: Statistical approach to quantum phase estimation, arXiv preprint http://arxiv.org/abs/2104.10285, (2021).

Shu, X.-B., Li, L.-N., Ren, M.-M., Mohammed, B.O.: A new binary to gray code converter based on quantum-dot cellular automata nanotechnology. Photon Netw. Commun. 41(1), 102–108 (2021)

Wu, L., Shen, Z., Ji, Y.: Using nano-scale QCA technology for designing fault-tolerant 2: 1 multiplexer. Analog Integr. Circuits Sign. Process. 109, 553–562 (2021)

Patidar, M., Gupta, N.: Efficient design and implementation of a robust coplanar crossover and multilayer hybrid full adder–subtractor using QCA technology. J. Supercomput. (2021). https://doi.org/10.1007/s11227-020-03592-5

Zhang, Y., Lv, H., Du, H., Huang, C., Liu, S., Xie, G.: Modular design of QCA carry flow adders and multiplier with reduced wire crossing and number of logic gates. Int. J. Circuit Theory Appl. 44(7), 1351–1366 (2016)

Thapliyal, H., Ranganathan, N.: A new design of the reversible subtractor circuit. In: 2011 11th IEEE international conference on nanotechnology, IEEE, pp 1430–1435 (2011)

Khan, M.H., Perkowski, M.A.: Quantum ternary parallel adder/subtractor with partially-look-ahead carry. J. Syst. Architect. 53(7), 453–464 (2007)

Mohammadi, M., Eshghi, M., Haghparast, M., Bahrololoom, A.: Design and optimization of reversible bcd adder/subtractor circuit for quantum and nanotechnology based systems. World Appl. Sci. J. 4(6), 787–792 (2008)

Raj, M., Ahmed, S., Lakshminarayanan, G.: Subtractor circuits using different wire crossing techniques in quantum-dot cellular automata. J. Nanophotonics 14(2), 026007 (2020)

Walus, K., Dysart, T.J., Jullien, G.A., Budiman, R.A.: QCADesigner: A rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 3(1), 26–31 (2004)

Walus, K.: ATIPS Laboratory QCADesigner Homepage. ATIPS Laboratory, Univ. Calgary, Calgary (2002)

Labrado, C., Thapliyal, H.: Design of adder and subtractor circuits in majority logic-based field-coupled QCA nanocomputing. Electron. Lett. 52(6), 464–466 (2016)

Lakshmi, S.K., Athisha, G., Karthikeyan, M., Ganesh, C.: Design of subtractor using nanotechnology based QCA. In: 2010 international conference on communication control and computing technologies, 2010, IEEE, pp 384–388 (2010)

Dallaki, H., Mehran, M.: Novel subtractor design based on quantum-dot cellular automata (QCA) nanotechnology. Int. J. Nanosci. Nanotechnol. 11(4), 257–262 (2015)

Reshi, J.I., Banday, M.T.: Efficient design of nano scale adder and subtractor circuits using quantum dot cellular automata (2016).

Bahar, A.N., Waheed, S., Hossain, N., Asaduzzaman, M.: A novel 3-input XOR function implementation in quantum dot-cellular automata with energy dissipation analysis. Alex. Eng. J. 57(2), 729–738 (2018)

Gassoumi, I., Touil, L., Mtibaa, A.: An efficient design of QCA full-adder-subtractor with low power dissipation. J. Electr. Comput. Eng. 2021, 1–9 (2021)

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

There is no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Hu, S. An optimized and area-efficient QCA-based subtractor with easy access to input and output: design and cost estimation. Photon Netw Commun 45, 128–135 (2023). https://doi.org/10.1007/s11107-023-00994-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11107-023-00994-2