Abstract

The Simons Observatory (SO) is a cosmic microwave background instrumentation suite in the Atacama Desert of Chile. More than 65,000 polarization-sensitive transition-edge sensor (TES) bolometers will be fielded in the frequency range spanning 27 to 280 GHz, with three separate dichroic designs. The mid-frequency 90/150 GHz and ultra-high-frequency 220/280 GHz detector arrays, fabricated at NIST, account for 39 of 49 total detector modules and implement the feedhorn-fed orthomode transducer-coupled TES bolometer architecture. A robust production-level fabrication framework for these detector arrays and the monolithic DC/RF routing wafers has been developed, which includes single device prototyping, process monitoring techniques, in-process metrology, and cryogenic measurements of critical film properties. Application of this framework has resulted in timely delivery of nearly 100 total superconducting focal plane components to SO with \(88\%\) of detector wafers meeting nominal criteria for integration into a detector module: a channel yield \(>95\%\) and \(T_{\textrm{c}}\) in the targeted range.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The Simons Observatory (SO) is a cosmic microwave background (CMB) instrumentation suite situated at an elevation of 5200 m in the Atacama Desert of Chile [1, 2]. The baseline observatory consists of one six-meter large-aperture telescope to characterize small angular scale celestial features and three half-meter small-aperture telescopes to search for gravitational waves at large angular scales to probe inflation. SO will field more than 65,000 polarization-sensitive transition-edge sensor (TES) bolometers spanning 27 to 280 GHz, with three separate dichroic designs: low-frequency (LF), mid-frequency (MF), and ultra-high-frequency (UHF) with band centers at 27/39 GHz, 90/150 GHz, and 220/280 GHz, respectively. The LF detector arrays utilize the lenslet-coupled sinuous antenna architecture and are fabricated at UC-Berkeley [3, 4]. The MF and UHF detector arrays, which implement the feedhorn-fed orthomode transducer-coupled architecture [5, 6], and the DC/RF routing wafers, which provide the cold readout interface between MF/UHF detectors and microwave multiplexers, are fabricated at NIST and account for 39 of 49 total detector modules [7,8,9,10].

The evolving science goals of CMB experiments demand larger numbers of densely packed large-format focal planes of high-yield multi-chroic detectors and readout. To meet this need, the fabrication team at NIST has developed a robust fabrication framework which allows for reliable high-throughput production of science-grade MF and UHF detector arrays and monolithic DC/RF routing wafers. Implementation of this framework has resulted in delivery of >40 150-mm high-yield superconducting TES bolometer arrays and >50 DC/RF routing wafers; the in-lab cryogenic detector array performance is described in a companion paper [11]. We present the fabrication process (Sect. 2), including in-process and post-process metrology (Sect. 3), and discuss best practices which allow for higher volume production in a shared R&D cleanroom (Sect. 4). Section 5 summarizes recent work aimed to facilitate in-lab characterization of TES bolometer arrays via the addition of a second in-series TES.

2 Fabrication Process Overview

The detector array fabrication process follows Ref. [12], which describes the rhomboidal detector array layout of repeating pixels and dense wiring buses patterned with stepped lithography in 11 separate steps. Each SO MF and UHF array has 430 optical pixels with 4 polarization-sensitive TESs per pixel in 2 frequency bands, for a total of 1720 superconducting detectors. The arrays are fabricated on double-side-polished (DSP), 500-\(\upmu\)m-thick, 150 mm silicon (Si) wafers coated with 450 nm thermal silicon oxide (SiO\(_x\)) and 2 \(\upmu\)m low-pressure chemical vapor deposited (LPCVD) super-low-stress silicon nitride (SiN\(_x\)), both deposited at a commercial vendor [13]. These dielectric layers are used to define the thermal link between the isolated bolometer island, which houses the TES, and the thermal bath of the thick Si substrate. The monolithic 1720-channel DC/RF routing wafers are fabricated on DSP, 500-\(\upmu\)m-thick, 150 mm Si wafers coated with 150 nm thermal SiO\(_x\) and utilize many of the same materials and processes as the detector arrays, but rely on a direct-write photolithography process to pattern the 6 layers of non-repeating circuitry [7].

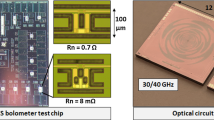

Figure 1 shows a series of micrographs from a 90 GHz TES bolometer at each layer in the fabrication process. The frontside and backside processing steps are summarized in Table 1. A SO UHF detector array and DC/RF routing wafer are shown in Fig. 2.

3 Metrology and Process Monitoring

Detector characteristics such as TES normal resistance \(R_{\textrm{n}}\), superconducting critical temperature \(T_{\textrm{c}}\), saturation power \(P_{\textrm{sat}}\), and time constant \(\tau _{\textrm{eff}}\) are controlled with well-understood device design and fabrication processes. CMB instrument performance relies on detector arrays operating as designed. For example, controlling \(T_{\textrm{c}}\) is important, as detector noise equivalent power scales as \(T_{\textrm{c}}\) \(^{\mathrm {(n+1)/2}}\), where n \(\sim {~}\)3 [14].

To ensure a fabrication process that results in repeatable high-yield wafers, we have adopted a 3-tier metrology approach. This allows for calculated decisions regarding which processes to monitor and measurements to collect during and after fabrication. It balances a high-yield repeatable fabrication process with delivery schedules, personnel skillsets, and equipment demands. Implementing this production fabrication framework has resulted in 88\(\%\) (72\(\%\)) of all detector wafers (DC/RF routing wafers) meeting nominal criteria to be integrated into a module. Detectors must have \(>95\%\) channel yield (room temperature electrical continuity, mechanical membrane yield, microscope inspection of channel defects) and \(T_{\textrm{c}}\) in the targeted range; DC/RF routing wafers must have \(>90\%\) channel yield and shunt resistance in the targeted range.

Top tier metrology. (Left) A multi-layer cross-section FIB-SEM image shows Nb (light) and SiN\(_x\) (dark) layer thickness and etch profile. This micrograph prompted the development of a simplified and more robust process to eliminate the third Nb wiring layer, seen here as an undesired remnant filament on the top surface which may cause electrical shorts. (Right) SO MF single test pixel fabricated to verify prototype design

The top tier of metrology includes process development tasks and pre-production prototyping, which validate single- and multi-step process quality and compatibility. These tasks occur when process or design changes are required. High-resolution scanning-electron microscope (SEM) imaging, with and without focused-ion beam (FIB) milling of single- and multi-layer cross-sections, allows for verification of etch processes, layer conformality, and visual detection of any defects that may compromise the device operation. Fabrication of single test pixels allows for pre-production rapid prototyping with dark and optical characterization of \(T_{\textrm{c}}\), \(P_{\textrm{sat}}\), on-chip passband filters, optical efficiency, and polarization response to feed back to detector array design [15, 16]. Measurements that match simulation confirm the design and the quality of the overall fabrication process. Examples of top tier metrology tasks are shown in Fig. 3.

Middle tier metrology. (Left) SiN\(_x\) thickness uniformity as-deposited (8 separate wafers) and after in-situ Nb deposition RF clean (5 separate wafers), showing that radial uniformity is maintained at each step and that the fabrication process is highly repeatable. (Middle) Photograph of rapid turnaround cryostat used for in-process \(T_{\textrm{c}}\) measurements. (Right) Custom 4-wire PCB for superconducting film and device characterization and plot of Al with 0.2 atomic percent Mn anneal temperature versus \(T_{\textrm{c}}\) for SO MF detector batch, with the red line indicating the target \(T_{\textrm{c}}\)

Bottom tier metrology. (Left) Measured \(T_{\textrm{c}}\) of the center (pin), edge (slot), and average for each SO MF and UHF detector array, plotted in sequential order. Some SO MF detector arrays have been re-annealed post-fabrication to raise the \(T_{\textrm{c}}\) of the AlMn TES to the target value, 160 mK \({\mathrm {\pm }}\) 10 mK. (Right) Extracted values of sheet resistance from room temperature measurements of cross-bridge test structures on the DC/RF routing wafers [17]. The dashed lines are the median value

The middle tier consists of measurements that occur with every batch. CMB instruments rely on high detector efficiency, which can be achieved with low-loss superconducting microstrip wiring. As in [18], the loss of SiN\(_x\) and Nb thin films at microwave and millimeter-wave frequencies is measured and correlated to detector optical efficiency. Additionally, it is critical to monitor thin film deposition rates, etch rates, and thickness uniformity across the wafer, as in Fig. 4. Characterization of the SiN\(_x\) thickness across the wafer at each step in the process allows the fabricated device to match the design, which directly impacts the passband placement, e.g. As mentioned, achieving a target \(T_{\textrm{c}}\) is essential and each detector array batch includes a separate witness wafer to calibrate the AlMn process by measuring \(T_{\textrm{c}}\) as a function of annealing temperature [19]. Since the AlMn \(T_{\textrm{c}}\) can be tuned with annealing, this gives a per batch prescription for achieving the targeted \(T_{\textrm{c}}\).

The SO production fabrication utilizes a detailed fabrication process sheet, where every essential processing detail is documented. Each batch of detector arrays and DC/RF routing wafers includes a fabrication summary document, providing critical information to collaborators like room temperature electrical continuity, mechanical membrane yield, and results from microscope inspection for channel defects.

The bottom tier metrology is critical on a per wafer or per layer basis, with examples as in Fig. 5. Measurements for each wafer include thickness of thermal SiO\(_x\) and LPCVD SiN\(_x\) as delivered from vendor; critical layer (AlMn, Nb, PdAu) sheet resistance; room temperature probing for filament shorts, Nb residue, via continuity, crossover isolation, and wiring residue; full wafer semi-automated room temperature electrical continuity probing; and \(T_{\textrm{c}}\) measurements from center and edge of the detector array. At the per layer level, metrology steps include thin film stress, profilometry, ellipsometry, and manual optical microscope inspection.

4 Volume Production

The NIST cleanroom, much like many other facilities fabricating low temperature detectors, is a shared R&D facility and is not designed for high levels of wafer throughput. Scaling up to higher volumes necessitated developing a fabrication framework that balances time versus risk/reward for both the implementation of metrology steps and for process changes and improvements. The serial nature and maximum capacity of many NIST cleanroom tools was taken into account by optimizing the batch size to four wafers. Carrying multiple active in-fab batches in parallel and utilizing collaborative tool scheduling allows for maximum flexibility in optimizing tool usage and personnel time.

Implementation of these efficiencies in the NIST cleanroom has allowed for high-yield production of complicated superconducting devices at the scale required for SO. Throughout the entirety of the SO production fabrication endeavor, the average realized production fabrication time for detector arrays and DC/RF routing wafers was 9 weeks and 6 weeks per batch, respectively.

5 Ongoing Improvements

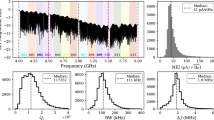

One benefit of a robust fabrication process is the capacity to add complexity in one or more steps. Experience with AlMn TESs has allowed for development of a second in-series AlMn TES with a higher \(T_{\textrm{c}}\) for increased dynamic range by adjusting the Mn concentration in Al. This enables more straightforward characterization of optical properties with standard in-lab loading conditions following [20], but optimized for 100 mK refrigeration which has become standard for current and future CMB experiments baselining this technical advancement [21, 22]. Prototype single test pixels implementing the dual-AlMn TES process have been fabricated and characterized. The dual-transition and projected \(P_{\textrm{sat}}\) for both TESs are shown in Fig. 6.

(Left) Resistance versus temperature plot showing two superconducting transitions, one for the science TES at 150 mK and one for the calibration TES at 517 mK. (Middle) Power sweep for the science TES at a range of bath temperatures. (Right) Power sweep for the calibration TES at a range of bath temperatures

6 Conclusions

We have presented a robust fabrication framework at NIST which has resulted in successful delivery of more than 40 detector arrays and more than 50 DC/RF routing wafers, completing the first phase of SO. These wafers are high-yield and have high intra- and inter-wafer uniformity, with \(88\%\) of detector wafers meeting nominal criteria for integration into a detector module: a channel yield \(>95\%\) and \(T_{\textrm{c}}\) in the targeted range [11]. By implementing volume-production best practices and metrology and process monitoring for maximum process control and repeatability, we have demonstrated a production fabrication rate of 9 weeks and 6 weeks per batch of detector arrays and DC/RF routing wafers, respectively.

References

The Simons Observatory. Collaboration et al., The Simons Observatory: science goals and forecasts. J. Cosmol. Astropart. Phys. 2019, 056 (2019). https://doi.org/10.1088/1475-7516/2019/02/056

N. Galitzki et al., The Simons Observatory: instrument overview. Millim. Submillim. Far-Infrared Detect. Instrum. Astron. IX 10708, 1070804 (2018). https://doi.org/10.1117/12.2312985

R. O’Brient et al., A dual-polarized broadband planar antenna and channelizing filter bank for millimeter wavelengths. Appl. Phys. Lett. 102, 063506 (2013). https://doi.org/10.1063/1.4791692

A. Mangu et al., The Simons Observatory: design, optimization, and performance of low frequency detectors. J. Low Temp. Phys. 256, 23 (2024)

K.W. Yoon et al., Feedhorn-coupled TES polarimeters for next-generation CMB instruments. AIP Conf. Proc. 1185, 515–518 (2009). https://doi.org/10.1063/1.3292392

J. McMahon et al., Planar orthomode transducers for Feedhorn-coupled TES polarimeters. AIP Conf. Proc. 1185, 490–493 (2009). https://doi.org/10.1063/1.3292386

E. Healy et al., Assembly development for the Simons Observatory focal plane readout module. Millim. Submillim. Far-Infrared Detect. Instrum. Astron. X 11453, 1145317 (2020). https://doi.org/10.1117/12.2561743

H. McCarrick et al., The Simons Observatory microwave SQUID multiplexing detector module design. Astrophys. J. 922, 38 (2021). https://doi.org/10.3847/1538-4357/ac2232

H. McCarrick, et al., The 90 and 150 GHz universal focal-plane modules for the Simons Observatory (2021). arXiv:2112.01458v1

E. Healy et al., The Simons Observatory 220 and 280 GHz focal-plane module: design and initial characterization. J. Low Temp. Phys. 209, 815–823 (2022). https://doi.org/10.1007/s10909-022-02788-8

D. Dutcher et al., The Simons Observatory: large-scale characterization of 90/150 GHz TES detector modules. J. Low Temp. Phys. 214, 247 (2024)

S.M. Duff et al., Advanced ACTPol multichroic polarimeter array fabrication process for 150 mm wafers. J. Low Temp. Phys. 184, 634–641 (2016). https://doi.org/10.1007/s10909-016-1576-y

Rogue Valley Microdevices. Certain commercial instruments are identified to specify the experimental study adequately. This does not imply endorsements by NIST or that the instruments are the best available for the purpose (2023). https://roguevalleymicrodevices.com/

K. Irwin, G. Hilton, Transition-Edge Sensors (Springer, Berlin, 2005), pp.63–150. https://doi.org/10.1007/10933596_3

S. Walker et al., Demonstration of 220/280 GHz multichroic Feedhorn-coupled TES polarimeter. J. Low Temp. Phys. 199, 891–897 (2020). https://doi.org/10.1007/s10909-019-02316-1

J. Hubmayr et al., Optical characterization of OMT-coupled TES bolometers for LiteBIRD. J. Low Temp. Phys. 209, 396–408 (2022). https://doi.org/10.1007/s10909-022-02808-7

M.G. Buehler, S.D. Grant, W.R. Thurber, Bridge and van der Pauw sheet resistors for characterizing the line width of conducting layers. J. Electrochem. Soc. 125, 650 (1978). https://doi.org/10.1149/1.2131517

C.L. Chang et al., Low loss superconducting microstrip development at Argonne National Lab. IEEE Trans. Appl. Supercond. 25, 1–5 (2015). https://doi.org/10.1109/TASC.2014.2369231

D. Li et al., AlMn transition edge sensors for advanced ACTPol. J. Low Temp. Phys. 184, 66–73 (2016). https://doi.org/10.1007/s10909-016-1526-8

P.A.R. Ade et al., Antenna-coupled TES bolometers used in BICEP2, keck array, and spider. Astrophys. J. 812, 176 (2015). https://doi.org/10.1088/0004-637X/812/2/176

K.N. Abazajian, et al., CMB-S4 Science Book, 1st Edn (2016). arXiv:1610.02743

S. Benton, Taurus: a Balloon-Borne polarimeter for cosmic reionization and galactic dust. NASA Proposal id. 20-APRA20-49 (2020)

Acknowledgements

This work was supported in part by the Simons Foundation (Award #457687, B.K.).

Author information

Authors and Affiliations

Contributions

S.M.D. wrote the main manuscript text and prepared the figures. All authors reviewed the manuscript or provided technical content for manuscript revisions.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Duff, S.M., Austermann, J., Beall, J.A. et al. The Simons Observatory: Production-Level Fabrication of the Mid- and Ultra-High-Frequency Wafers. J Low Temp Phys (2024). https://doi.org/10.1007/s10909-024-03117-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s10909-024-03117-x