Abstract

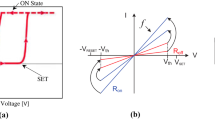

Complementary metal–oxide–semiconductor (CMOS) technology is reaching its limits due to the continuous shrinking process, which has an impact on various aspects including device size, performance, and power consumption. The memristor is one of the promising devices under investigation for use with deep-nanometer CMOS, having applicability in several fields due to its nonlinear behavior, nonvolatility, low power consumption, high density, and CMOS compatibility. Several models for memristors have been developed to date, but there is a requirement for compact models that are both flexible and sufficiently accurate. A general memristor model generated in Verilog-A is discussed herein to confirm its behavior in the one-transistor one-resistor (1T1R) oxide-based random-access memory (OxRAM) configuration, and validated at circuit level. The results of the model correlate well with experimental characterization data for the HfO2-based OxRAM memristor device, describing the characteristics of both its bipolar and unipolar memristor behaviors. The 1T1R structure is analyzed using the Spectre circuit simulator. Two cases are considered, using the cell as either programmable read-only memory (PROM) or electrically erasable programmable read-only memory (EEPROM). The simulation results confirm the desired nonlinear memristor characteristic, and the applicability of the model to fit and simulate different switching behaviors. The results are verified against both electrical and experimental characterization data, suggesting that the Verilog-A model is suitable for low-power and high-density logic circuit applications at the industrial level.

Similar content being viewed by others

References

Chua, L.: Memristor-the missing circuit element. IEEE Trans. Circuit Theory 18, 507–519 (1971)

Chua, L.O., Kang, S.M.: Memristive devices and systems. Proc. IEEE 64, 209–223 (1976)

Yakopcic, C., Taha, T.M., Subramanyam, G., & Pino, R.E.: Memristor SPICE model and crossbar simulation based on devices with nanosecond switching time. In: The 2013 International Joint Conference on Neural Networks (IJCNN) (pp. 1–7). IEEE (2013)

Kule, M., Rahaman, H., Bhattacharya, B.B.: On finding a defect-free component in nanoscale crossbar circuits. Procedia Comput. Sci. 70, 421–427 (2015)

Liu, H., Lv, H., Xu, X., Liu, R., Li, L., Liu, Q., Long, S. Wang, Y. Huo Z., Liu, M.: Gate induced resistive switching in 1T1R structure with improved uniformity and better data retention. In: 2014 IEEE 6th International Memory Workshop (IMW) (pp. 1–2). IEEE (2014)

Halawani, Y., Mohammad, B., Homouz, D., Al-Qutayri, M., Saleh, H.H.: Modeling and optimization of memristor and STT-RAM-based memory for low-power applications. IEEE Trans. VLSI Syst. 24(3), 1003–1014 (2016)

Biolek, Z., Biolek, D., Biolkova, V.: SPICE model of memristor with nonlinear dopant drift. Radioengineering 18(2), 211 (2009)

Kvatinsky, S., Friedman, E.G., Kolodny, A., Weiser, U.C.: TEAM: threshold adaptive memristor model. IEEE Trans. Circuits Syst. I Regul. Pap. 60(1), 211–221 (2013)

Chen, L., Li, C., Huang, T., Chen, Y., Wen, S., Qi, J.: A synapse memristor model with forgetting effect. Phys. Lett. A 377(45–48), 3260–3265 (2013). https://doi.org/10.1016/j.physleta.2013.10.024

Vourkas, I., Batsos, A., Sirakoulis, G.C.: SPICE modeling of nonlinear memristive behavior. Int. J. Circuit Theory Appl. 43(5), 553–565 (2015). https://doi.org/10.1002/cta.1957

Zhang, Y., Wang, X., Li, Y., Friedman, E.G.: Memristive model for synaptic circuits. IEEE Trans. Circuits Syst. II Express Briefs 64(7), 767–771 (2017)

Garbin, D., Vianello, E., Bichler, O., Rafhay, Q., Gamrat, C., Ghibaudo, G., DeSalvo, B., Perniola, L.: HfO2-based OxRAM devices as synapses for convolutional neural networks. IEEE Trans. Electron Devices 62(8), 2494–2501 (2015)

Boybat, I., Le Gallo, M., Nandakumar, S.R., Moraitis, T., Parnell, T., Tuma, T., Rajendran, B., Leblebici, Y., Sebastian, A., Eleftheriou, E.: Neuromorphic computing with multi-memristive synapses. Nat. Commun. 9(1), 2514 (2018)

Yakopcic, C., Taha, T.M., Subramanyam, G., Pino, R.E.: Generalized memristive device SPICE model and its application in circuit design. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 32(8), 1201–1214 (2013)

Rziga, F.O., Mbarek, K., Ghedira, S., Besbes, K.: The basic I-V characteristics of memristor model: simulation and analysis. Appl. Phys. A 123(4), 288 (2017)

Mbarek, K., Rziga, F.O., Ghedira, S., Besbes, K. (2017). An analysis of the dynamics of SPICE memristor model. In: 2017 International Conference on Control, Automation and Diagnosis (ICCAD) (pp. 054–059). IEEE

Oblea, A.S., Timilsina, A., Moore, D., Campbell, K.A.: Silver chalcogenide based memristor devices. In: The 2010 International Joint Conference on Neural Networks (IJCNN) (pp. 1–3). IEEE (2010)

Sun, X., Li, G., Zhang, X.A., Ding, L., Zhang, W.: Coexistence of the bipolar and unipolar resistive switching behaviours in Au/SrTiO3/Pt cells. J. Phys. D Appl. Phys. 44(12), 125404 (2011). https://doi.org/10.1088/0022-3727/44/12/125404

García-Redondo, F., Gowers, R.P., Crespo-Yepes, A., López-Vallejo, M., Jiang, L.: SPICE compact modeling of bipolar/unipolar memristor switching governed by electrical thresholds. IEEE Trans. Circuits Syst. I Regul. Pap. 63(8), 1255–1264 (2016)

Basha, N.K., Ramashri, T.: Dynamic composite resistive switching characteristics of multiple interconnected memristors. Int. J. Res. 4(7), 3171–3178 (2017)

Lee, J.S., Lee, S., Noh, T.W.: Resistive switching phenomena: a review of statistical physics approaches. Appl. Phys. Rev. 2(3), 031303 (2015)

Chen, P.Y., Yu, S.: Compact modeling of RRAM devices and its applications in 1T1R and 1S1R array design. IEEE Trans. Electron Devices 62(12), 4022–4028 (2015)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Rziga, F.O., Mbarek, K., Ghedira, S. et al. An efficient Verilog-A memristor model implementation: simulation and application. J Comput Electron 18, 1055–1064 (2019). https://doi.org/10.1007/s10825-019-01357-9

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-019-01357-9