Abstract

In this study, a simple, reliable, and universal circuit model of bipolar resistive-switching random-access memory (RRAM) is presented for the circuit-level simulation of a high-density cross-point RRAM array. For higher accuracy and reliability, the compact model has been developed to match the measurement data of the fabricated RRAM devices with \(\hbox {SiN}_{{x}}\) and \(\hbox {HfO}_{{x}}\) switching layers showing different reset switching behaviors. In the SPICE simulation, the RRAM cross-point array is virtually realized by embedding the empirically modeled memory cells, by which device performances such as read margin and power consumption in the high-density array are closely investigated.

Similar content being viewed by others

References

Fackenthal, R., Kitagawa, M., Otsuka, W., Prall, K., Mills, D., Tsutsui, K., Javanifard, J., Tedrow, K., Tsushima, T., Shibahara, Y., Hush, G.: A 16Gb ReRAM with 200 MB/s write and 1 GB/s read in 27 nm technology. In: IEEE International Solid-State Circuits Conference, pp. 338–340 (2014)

Kim, B.Y., Lee, K.J., Chung, S.O., Kim, S.G., Ko, Y.S., Kim, H.S.: Low power switching of Si-doped Ta\(_{2}\)O\(_{5}\) resistive random access memory for high density memory application. Jpn. J. Appl. Phys. 55, 04EE09 (2016)

Sakuragawa, Y., Takagi, Y., Ikai, T., Maeda, K., Dao, T.T., Sakai, H., Murata, H.: Achieving high ON/OFF ratio and good stability in organic nonvolatile resistive memory devices with polyisocyanide bearing oligothiophene. Jpn. J. Appl. Phys. 55, 03DC10 (2016)

Hsiao, Y.-P., Yang, W.-L., Wu, C.-C., Lin, L.-M., Chin, F.-T., Lin, Y.-H., Yang, K.-L.: Improving high-resistance state uniformity and leakage current for polyimide-based resistive switching memory by rubbing post-treatment. Jpn. J. Appl. Phys. 55, 01AA09 (2016)

Wu, C.-Y., You, H.-C., Lin, G.-K., Yang, W.-L.: Improving the operational characteristic stability in Al/Au/ZnO/Al resistive random access memory devices. Jpn. J. Appl. Phys. 55, 044101 (2016)

Su, Y.-T., Chang, T.-C., Tsai, T.-M., Chang, K.-C., Chu, T.-J., Chen, H.-L., Chen, M.-C., Yang, C.-C., Huang, H.-C., Lo, I., Zheng, J.-C., Sze, S.M.: Suppression of endurance degradation by applying constant voltage stress in one-transistor and one-resistor resistive random access memory. Jpn. J. Appl. Phys. 56, 010303 (2017)

Jo, S.H., Chang, T., Ebong, I., Bhadviya, B.B., Mazumder, P., Lu, W.: Nanoscale memristor device as syanpse in neuromorphic systems. Nano Lett. 10, 1297 (2010)

Chang, T., Jo, S.-H., Lu, W.: Short-term memory to long-term memory transition in a nanoscale memristor. ACS Nano 5, 7669 (2011)

Gao, B., Kang, J., Zhou, Z., Chen, Z., Huang, P., Liu, L., Liu, X.: Metal oxide resistive random access memory based synaptic devices for brain-inspired computing. Jpn. J. Appl. Phys. 55, 04EA06 (2016)

Kawahara, A., Azuma, R., Ikeda, Y., Kawai, K., Katoh, Y., Tanabe, K, Nakamura, T., Sumimoto, Y., Yamada, N., Nakai, N., Sakamoto, S., Hayakawa, Y., Tsuji, K., Yoneda, S., Himeno, A., Origasa, K., Shimakawa, K., Takagi, T., Mikawa, T., Aono, K.: An 8 Mb multi-layered cross-point ReRAM macro with 443 MB/s write throughput. In: IEEE International Solid-State Circuits Conference, pp. 432–434 (2012)

Liu, T.-Y., Yan, T.H., Scheuerlein, R., Chen, Y., Lee, J.K., Balakrishnan, G., Yee, G., Zhang, H., Yap, A., Ouyang, J., Sasaki, T, Addepalli, S., Al-Shamma, A., Chen, C.-Y., Gupta, M., Hilton, G., Joshi, S., Kathuria, A., Lai, V., Masiwal, D., Matsumoto, M., Nigam, A., Pai, A., Pakhale, J., Siau, C.-H., Wu, X., Yin, R., Peng, L., Kang, J.-Y., Huynh, S., Wang, H, Nagel, N., Tanaka, Y., Higashitani, M., Minvielle, T., Gorla, C, Tsukamoto, T., Yamaguchi, T. Okajima, M., Okamura, T., Takase, S., Hara, T., Inoue, H., Fasoli, l., Mofidi, M., Shrivastava, R., Quader, K.: A \(130.7\text{mm}^{2}\) 2-layer 32 Gb ReRAM memory device in 24 nm technology. In: IEEE International Solid-State Circuits Conference, pp. 210–212 (2013)

Eryilmaz, S.B., Kuzum, D., Yu, S., Wong, H.-S.P.: Device and system level design considerations for analog-non-volatile-memory based neuromorphic architectures. In: IEEE International Electron Devices Meeting, pp. 64–67 (2015)

Burr, G.W., Naraynan, P., Shelby, R.M., Boybat, S.I., Nolfo, C., Leblebici, Y.: Large-scale neural networks implemented with non-volatile memory as the synaptic weight element: comparative performance analysis (accuracy, speed, and power). In: IEEE International Electron Devices Meeting, pp. 76–79 (2015)

Yu, S., Chen, P.-Y., Cao, Y., Xia, L., Wang, Y., Wu, H.: Scaling-up resistive synaptic arrays for neuro-inspired architecture: challenges and prospect. In: IEEE International Electron Devices Meeting, pp. 451–454 (2015)

Prezioso, M., Kataeva, I., Merrikh-Bayat, F., Hoskins, B., Adam, G., Sota, T., Likharev, K., Strukov, D.: Modeling and implementation of firing-rate neuromorphic-network classifiers with Bilayer \(\text{ Pt }/\text{ Al }_{2}\text{ O }_{3}/\text{ TiO }_{{\rm 2-x}}/\text{ Pt }\) memristors. In: IEEE International Electron Devices Meeting, pp. 455–458 (2015)

Chen, B., Cai, F., Zhou, J., Ma, W., Sheridan, P., Lu, W.D.: Efficient in-memory computing architecture based on crossbar arrays. In: IEEE International Electron Devices Meeting, pp. 459–462 (2015)

Moon, K., Chan, E., Park, J., Gi, S., Chu, M., Baek, K.: High density neuromorphic system with \(\text{ Mo }/\text{ Pr }_{0.7}\text{ Ca }_{0.3}\text{ MnO }_{3}\) synapse and \(\text{ NbO }_{2}\) IMT oscillator neuron. In: IEEE International Electron Devices Meeting, pp. 463–466 (2015)

Guan, X., Yu, S., Wong, H.-S.P.: A SPICE compact model of metal oxide resistive switching memory with variations. IEEE Electron Device Lett. 33, 1405 (2012)

Li, H., Huang, P., Gao, B., Chen, B., Liu, X., Kang, J.: A SPICE model of resistive random access memory for large-scale memory array simulation. IEEE Electron Device Lett. 35, 211 (2014)

Chang, H.-L., Li, H.-C., Liu, C.W., Chen, F., Tsai, M.-J.: A parameterized SPICE macromodel of resistive random access memory and circuit demonstration. In: Proceedings of SISPAD, vol. 163 (2011)

Blaso, J., Jančovič, P., Fröhlich, K., Suñé, J., Miranda, E.: Modeling of the switching I–V characteristics in ultrathin (5 nm) atomic layer deposited HfO2 films using the logistic hysteron. J. Vac. Sci. Technol. B 33, 01A102 (2015)

Kim, Y.S., Min, K.-S.: Behavioral current–voltage model with intermediate states for unipolar resistive memories. J. Semicond. Technol. Sci. 13, 539 (2013)

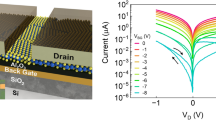

Kim, S., Cho, S., Ryoo, K.-C., Park, B.-G.: Effects of conducting defects on resistive switching characteristics of \(\text{ SiN }_{x}\)-based resistive random-access memory with MIS structure. J. Vac. Sci. Technol. B 33, 6 (2015)

Kim, S., Cho, S., Park, B.-G.: Sub-100-nA-operating Si-compatible \(\text{ Ni }/\text{ Ti }/\text{ HfO }_{2}/\text{ SiO }_{2}/\text{ Si }\) RRAM device for high-density integration and low-power applications. J. Nanosci. Nanotechnol. 16, 10 (2016)

Yang, Y., Gao, P., Gaba, S., Chang, T., Pan, X., Lu, W.: Observation of conducting filament growth in nanoscale resistive memories. Nat. Commun. 3, 732 (2012)

Krishnan, K., Tsuruoka, T., Aono, M.: Direct observation of anodic dissolution and filament growth behavior in polyethylene-oxide-based atomic switch structures. Jpn. J. Appl. Phys. 55, 06GK02 (2016)

Kim, S., Jung, S., Kim, M.-H., Cho, S., Park, B.-G.: Gradual bipolar resistive switching in \(\text{ Ni }/\text{ Si }_{3}\text{ N }_{4}/\text{ n }^{+}\text{-Si }\) resistive-switching memory device for high-density integration and low-power applications. Appl. Phys. Lett. 106, 212106 (2015)

Kim, S., Park, B.-G.: Improved multi-level capability in \(\text{ Si }_{3}\text{ N }_{4}\)-based resistive switching memory using continuous gradual reset switching. J. Phys. D Appl. Phys. 50, 2 (2016)

Acknowledgements

This work was supported in part by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIP) (2015R1A2A1A01007307) and in part by the Brain Korea 21 Plus Project in 2017.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kim, MH., Kim, S., Ryoo, KC. et al. Circuit-level simulation of resistive-switching random-access memory cross-point array based on a highly reliable compact model. J Comput Electron 17, 273–278 (2018). https://doi.org/10.1007/s10825-017-1116-2

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-017-1116-2